# A TIMED SEMANTICS FOR A HIERARCHICAL DESIGN NOTATION

Phillip James Brooke

A thesis submitted in partial fulfilment of the requirements for the Degree of Doctor of Philosophy

> University of York Department of Computer Science

> > April 1999

#### Abstract

The software control systems that are embedded in many products are increasingly complex. There are many stages in the typical software design life cycle, and these include testing, and sometimes use formal methods.

This thesis aims to strengthen the design life cycle by demonstrating a pragmatic use of formal methods for an industrially-applicable design method.

We take a design method and notation called DORIS (which is used by British Aerospace), and give a formal syntax for the notation. This then forms the structure into which we place activities (the active processing parts of the system), and intercommunication data areas (IDAs, the 'passive' parts of the system through which activities communicate).

We aim to give an industrially useful semantics for this notation, so we use several models of Timed CSP as the underlying semantic domain. This allows us to represent the many timed and liveness requirements in BAe's work using the well-understood theory for Timed CSP.

For a given system design, we can generate a Timed CSP representation of the system from its DORIS design. This representation is an abstraction of the behaviour of the system modelling the interactions between components in that system. This Timed CSP model can be analyzed and assertions tested against it. However, because of the size of these systems, tool support is necessary.

The final part of this thesis concerns the construction of such toolsupported proofs, using both a bespoke tool for generating Timed CSP from the DORIS design, and two industrial-strength tools, PVS and FDR. We illustrate this with two case studies, one of them a significant model based on a real system.

This work demonstrates that even when using current state-of-the-art tools, it is difficult to apply these methods in practice. We conclude that without significant advances in tool technology, it will continue to be difficult to prove non-trivial properties about large systems at the level of abstraction presented in this thesis.

# Contents

| A | cknov | vledgements                         | 15 |

|---|-------|-------------------------------------|----|

| A | uthor | 's Declaration                      | 17 |

| Ι | Int   | roduction and Survey                | 19 |

| 1 | Intr  | oduction                            | 21 |

|   | 1.1   | Motivation                          | 21 |

|   |       | 1.1.1 Problem Domain                | 21 |

|   |       | 1.1.2 General Approach              | 21 |

|   |       | 1.1.3 MASCOT and DORIS              | 22 |

|   |       | 1.1.4 Reasoning about Designs       | 22 |

|   |       | 1.1.5 Application of Formal Methods | 23 |

|   | 1.2   | Contribution of this Thesis         | 24 |

|   | 1.3   | Development of Ideas                | 24 |

|   | 1.4   | Overview                            | 25 |

| 2 | Bacl  | cground Survey                      | 27 |

|   | 2.1   | Critical Systems                    | 27 |

|   | 2.2   | Formal Methods                      | 28 |

|   | 2.3   | MASCOT and DORIS                    | 30 |

|   |       | 2.3.1 MASCOT                        | 30 |

|   |       | 2.3.2 DORIS                         | 33 |

|   | 2.4   | Communicating Sequential Processes  | 33 |

|   |       | 2.4.1 Model of Computation          | 34 |

|   |       | 2.4.2 Untimed CSP                   | 35 |

|   |       | 2.4.3 Timed CSP                     | 38 |

|   |       |                                     |    |

|    |     | 2.4.4   | Hierarchy and Refinement            | . 41 |

|----|-----|---------|-------------------------------------|------|

|    |     | 2.4.5   | Summary and Remarks                 | . 43 |

|    |     | 2.4.6   | Other Notations                     | . 43 |

|    | 2.5 | Notat   | ional Issues                        | . 45 |

|    | 2.6 | Mecha   | anical Proving                      | . 47 |

|    |     | 2.6.1   | FDR                                 | . 47 |

|    |     | 2.6.2   | PVS                                 | . 48 |

|    |     | 2.6.3   | MADGE                               | . 48 |

|    |     | 2.6.4   | Other Tools                         | . 49 |

|    | 2.7 | Summ    | nary of Survey                      | . 49 |

|    | 1   |         |                                     |      |

| ΙΙ | T   | neoret  | ical Semantics                      | 51   |

| 3  | Den | otatior | nal Semantics for DORIS             | 53   |

|    | 3.1 | Ratior  | nale                                | . 53 |

|    |     | 3.1.1   | Denotational Semantics              |      |

|    |     | 3.1.2   | Timed CSP                           | . 54 |

|    | 3.2 |         | nal Description of DORIS            |      |

|    |     | 3.2.1   | Data Interaction Architecture       |      |

|    |     | 3.2.2   | Entities of a DORIS System          |      |

|    | 3.3 | 2       | x                                   |      |

|    |     | 3.3.1   | Tags                                |      |

|    |     |         | BNF-style Notation                  |      |

|    |     | 3.3.3   | Complex Constructs                  |      |

|    |     | 3.3.4   | Basic Constructs                    |      |

|    | 3.4 | -       | ystem Tuple                         |      |

|    | 3.5 |         | Semantics                           |      |

|    | 3.6 | Semar   |                                     |      |

|    |     | 3.6.1   | Basic Components                    |      |

|    |     | 3.6.2   | Complex Constructs                  |      |

|    |     | 3.6.3   | Semantics of the System             |      |

|    | 3.7 | Exam    | L                                   |      |

|    | 3.8 |         | extual Information                  |      |

|    |     | 3.8.1   | Path Resolution                     |      |

|    | • • | 3.8.2   | Allocation to Transputers and Links |      |

|    | 3.9 | Refine  | ement                               | . 74 |

## CONTENTS

| 4 |      | cification of IDAs 79                             |

|---|------|---------------------------------------------------|

|   | 4.1  | Overview                                          |

|   |      | 4.1.1 General Model                               |

|   |      | 4.1.2 Distribution Issues                         |

|   | 4.2  | Types of Shared Variable                          |

|   |      | 4.2.1 Lamport's Variables                         |

|   |      | 4.2.2 Simpson's Variables                         |

|   | 4.3  | Untimed Two-Point Models                          |

|   | 4.4  | Fixing the Two-Point Pool                         |

|   | 4.5  | Three-Point IDA Specifications                    |

|   |      | 4.5.1 Preliminaries                               |

|   |      | 4.5.2 Constant                                    |

|   |      | 4.5.3 Pool                                        |

|   |      | 4.5.4 Channel Family                              |

|   |      | 4.5.5 Signal Family                               |

|   |      | 4.5.6 Void Protocols                              |

|   |      | 4.5.7 Integral and Separate Response Protocols 98 |

|   | 4.6  | IDA Semantics                                     |

|   | 4.7  | Composition                                       |

|   | 4.8  | Multiplexing                                      |

|   | 4.9  | Forwarding                                        |

|   | 4.10 | Implementation                                    |

|   |      | 4.10.1 Lamport's Safe Variable                    |

|   |      | 4.10.2 Lamport's Regular Variable                 |

|   |      | 4.10.3 Lamport's Atomic Variable                  |

|   |      | 4.10.4 Four-slot Implementation of the Pool 106   |

|   | 4.11 | Timed IDAs                                        |

|   |      | 4.11.1 Specifications                             |

|   |      | 4.11.2 Implementations                            |

|   |      | •                                                 |

| 5 | Lang | guage for Activities 111                          |

|   | 5.1  | Overview                                          |

|   |      | 5.1.1 Activity Description Language               |

|   |      | 5.1.2 Graphical Notations                         |

|   | 5.2  | Alphabets and Events                              |

|   | 5.3  | Syntax                                            |

|   | 5.4  | Semantics                                         |

|   | 5.5  | Example                                           |

|   |      |                                                   |

|    | 5.6 | Support for Modelling a Scheduler1245.6.1Why Model A Scheduler?1245.6.2Abstraction1245.6.3Initial Approach1255.6.4Descheduling1265.6.5Example1275.6.6Deadlines1285.6.7Untimed Scheduler Predicates129 |

|----|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| II | I M | lechanical Implementation 131                                                                                                                                                                         |

| 6  | Mec | hanical Support 133                                                                                                                                                                                   |

|    | 6.1 | Overview                                                                                                                                                                                              |

|    | 6.2 | Rationale                                                                                                                                                                                             |

|    |     | 6.2.1 Related Work                                                                                                                                                                                    |

|    |     | 6.2.2 Choice of PVS and FDR                                                                                                                                                                           |

|    |     | 6.2.3 Other Tools                                                                                                                                                                                     |

|    | 6.3 | Summary of Mechanical Support                                                                                                                                                                         |

|    | 6.4 | PVS                                                                                                                                                                                                   |

|    |     | 6.4.1 Timed CSP                                                                                                                                                                                       |

|    |     | 6.4.2 Timed CSP Theory Construction                                                                                                                                                                   |

|    |     | 6.4.3 DORIS                                                                                                                                                                                           |

|    |     | 6.4.4 TCC Proofs                                                                                                                                                                                      |

|    |     | 6.4.5 Time and Effort Required                                                                                                                                                                        |

|    | 6.5 | FDR                                                                                                                                                                                                   |

|    |     | 6.5.1 Time                                                                                                                                                                                            |

|    |     | 6.5.2 DORIS                                                                                                                                                                                           |

|    |     | 6.5.3 Program Definitions of IDAs                                                                                                                                                                     |

|    |     | 6.5.4 Time and Effort Required                                                                                                                                                                        |

|    | 6.6 | Bespoke Tool for Translating DORIS to Timed CSP 155                                                                                                                                                   |

| 7  | IDA | Analysis 159                                                                                                                                                                                          |

|    | 7.1 | Predicate and Program Specifications: The Pool 159                                                                                                                                                    |

|    |     | 7.1.1 Untimed Traces Model                                                                                                                                                                            |

|    |     | 7.1.2 Timed Failures Model                                                                                                                                                                            |

|    |     | 7.1.3 Time and Effort                                                                                                                                                                                 |

|    | 7.2 | FDR and Time                                                                                                                                                                                          |

|    |     |                                                                                                                                                                                                       |

|    | 7.3  | Four-slot Implementation of the Pool          | 168 |

|----|------|-----------------------------------------------|-----|

|    | 7.4  | Composition of IDAs                           |     |

|    | 7.5  | PVS Lemmas                                    |     |

|    | 7.6  | Comments on Results                           | 174 |

| 8  | Case | e Studies                                     | 175 |

|    | 8.1  | Introduction to Case Studies                  | 175 |

|    | 8.2  | Small Case Study                              |     |

|    |      | 8.2.1 Translation of the Design               |     |

|    |      | 8.2.2 Required Properties                     |     |

|    | 8.3  | Small Case Study: Safety Condition Analysis   |     |

|    | 0.0  | 8.3.1 Sketch Proof                            |     |

|    |      | 8.3.2 PVS Proof                               |     |

|    |      | 8.3.3 FDR Check                               |     |

|    | 8.4  | Small Case Study: Liveness Condition Analysis |     |

|    |      | 8.4.1 Sketch Proof                            |     |

|    |      | 8.4.2 PVS Proof                               |     |

|    |      | 8.4.3 FDR Check                               |     |

|    | 8.5  | Large Case Study                              |     |

|    |      | 8.5.1 Summary of the Design                   |     |

|    |      | 8.5.2 Code Stubs                              |     |

|    |      | 8.5.3 Machine Assistance                      |     |

|    |      | 8.5.4 Required Property                       |     |

|    | 8.6  | Large Case Study Analysis                     |     |

|    |      | 8.6.1 FDR                                     |     |

|    |      | 8.6.2 PVS                                     | 187 |

|    | 8.7  | Comments on Results                           | 188 |

|    |      |                                               |     |

| IV | 7 D  | Discussion and Conclusions                    | 191 |

| 9  | Diec | cussion                                       | 193 |

| 9  | 9.1  | DORIS Semantics                               | 193 |

|    | 7.1  | 9.1.1 Why Timed CSP?                          |     |

|    |      |                                               | 194 |

|    |      | 9.1.3 IDAs                                    |     |

|    |      | 9.1.4 Activities                              |     |

|    |      | 9.1.5 Timing                                  |     |

|    |      | ······································        | 170 |

|        | 9.2                                                   | Mecha                                                                                                       | inical Translation of DORIS to Timed CSP                                                                                                                                                                                                                  | 198                                                                                                                                          |

|--------|-------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

|        | 9.3                                                   | Mecha                                                                                                       | inical Support                                                                                                                                                                                                                                            |                                                                                                                                              |

|        |                                                       | 9.3.1                                                                                                       | Timed CSP, DORIS, and PVS                                                                                                                                                                                                                                 | 199                                                                                                                                          |

|        |                                                       | 9.3.2                                                                                                       | DORIS, Timed CSP, and FDR                                                                                                                                                                                                                                 | 200                                                                                                                                          |

|        | 9.4                                                   | Remar                                                                                                       | ·ks                                                                                                                                                                                                                                                       | 200                                                                                                                                          |

|        |                                                       | 9.4.1                                                                                                       | Correctness of Designs                                                                                                                                                                                                                                    | 200                                                                                                                                          |

|        |                                                       | 9.4.2                                                                                                       | Industrial Scale                                                                                                                                                                                                                                          | 201                                                                                                                                          |

|        |                                                       | 9.4.3                                                                                                       | PCI Metric                                                                                                                                                                                                                                                | 202                                                                                                                                          |

|        |                                                       | 9.4.4                                                                                                       | Alternative Approaches                                                                                                                                                                                                                                    | 203                                                                                                                                          |

|        | 9.5                                                   | Future                                                                                                      | e Work                                                                                                                                                                                                                                                    | 204                                                                                                                                          |

|        |                                                       | 9.5.1                                                                                                       | General Formal Methods Tool Support                                                                                                                                                                                                                       | 204                                                                                                                                          |

|        |                                                       | 9.5.2                                                                                                       | Improved Proof Interfaces                                                                                                                                                                                                                                 |                                                                                                                                              |

|        |                                                       | 9.5.3                                                                                                       | More Investigation of IDAs and General Lemmas                                                                                                                                                                                                             | 205                                                                                                                                          |

|        |                                                       | 9.5.4                                                                                                       | Code Generation and Animation                                                                                                                                                                                                                             | 206                                                                                                                                          |

|        |                                                       |                                                                                                             |                                                                                                                                                                                                                                                           |                                                                                                                                              |

| 10     |                                                       | clusion                                                                                                     |                                                                                                                                                                                                                                                           | 207                                                                                                                                          |

|        |                                                       |                                                                                                             | oblem                                                                                                                                                                                                                                                     |                                                                                                                                              |

|        |                                                       |                                                                                                             | olution                                                                                                                                                                                                                                                   |                                                                                                                                              |

|        | 10.3                                                  | Final F                                                                                                     | Remarks                                                                                                                                                                                                                                                   | 208                                                                                                                                          |

|        |                                                       |                                                                                                             |                                                                                                                                                                                                                                                           |                                                                                                                                              |

|        |                                                       |                                                                                                             |                                                                                                                                                                                                                                                           |                                                                                                                                              |

| v      | Ar                                                    | ppend                                                                                                       | ices. Glossaries, and Bibliography                                                                                                                                                                                                                        | 211                                                                                                                                          |

| V      | Aŗ                                                    | opend                                                                                                       | ices, Glossaries, and Bibliography                                                                                                                                                                                                                        | 211                                                                                                                                          |

|        | •                                                     | •                                                                                                           | ices, Glossaries, and Bibliography<br>for DORIS                                                                                                                                                                                                           | 211<br>213                                                                                                                                   |

|        | Sem                                                   | antics f                                                                                                    |                                                                                                                                                                                                                                                           | 213                                                                                                                                          |

|        | Sem<br>A.1                                            | <b>antics f</b><br>Static S                                                                                 | for DORIS                                                                                                                                                                                                                                                 | <b>213</b><br>213                                                                                                                            |

| A      | Sem<br>A.1<br>A.2                                     | <b>antics f</b><br>Static S<br>Path R                                                                       | for DORIS<br>Semantics for DORIS                                                                                                                                                                                                                          | <b>213</b><br>213<br>216                                                                                                                     |

|        | Sem<br>A.1<br>A.2<br>Prot                             | antics f<br>Static S<br>Path R<br>otype E                                                                   | for DORIS<br>Semantics for DORIS                                                                                                                                                                                                                          | <ul> <li>213</li> <li>213</li> <li>216</li> <li>223</li> </ul>                                                                               |

| A      | Sem<br>A.1<br>A.2<br>Prot<br>B.1                      | antics f<br>Static S<br>Path R<br>otype I<br>ASCII                                                          | for DORIS<br>Semantics for DORIS                                                                                                                                                                                                                          | <ul> <li>213</li> <li>213</li> <li>216</li> <li>223</li> <li>223</li> </ul>                                                                  |

| A      | Sem<br>A.1<br>A.2<br>Prot<br>B.1<br>B.2               | antics f<br>Static S<br>Path R<br>otype D<br>ASCII<br>Examp                                                 | for DORIS Semantics for DORIS Lesolution Algorithm                                                                                                                                                                                                        | <ul> <li>213</li> <li>213</li> <li>216</li> <li>223</li> <li>225</li> </ul>                                                                  |

| A      | Sem<br>A.1<br>A.2<br>Prot<br>B.1                      | antics f<br>Static S<br>Path R<br>otype D<br>ASCII<br>Examp                                                 | for DORIS<br>Semantics for DORIS                                                                                                                                                                                                                          | <ul> <li>213</li> <li>213</li> <li>216</li> <li>223</li> <li>225</li> </ul>                                                                  |

| A<br>B | Sem<br>A.1<br>A.2<br>Prot<br>B.1<br>B.2<br>B.3        | antics f<br>Static S<br>Path R<br>otype D<br>ASCII<br>Examp<br>Algori                                       | for DORIS Semantics for DORIS                                                                                                                                                                                                                             | <b>213</b><br>213<br>216<br><b>223</b><br>223<br>225<br>228                                                                                  |

| A<br>B | Sem<br>A.1<br>A.2<br>Prot<br>B.1<br>B.2<br>B.3<br>PVS | antics f<br>Static S<br>Path R<br>otype E<br>ASCII<br>Examp<br>Algori<br>Model                              | for DORIS Semantics for DORIS                                                                                                                                                                                                                             | <ul> <li>213</li> <li>213</li> <li>216</li> <li>223</li> <li>225</li> <li>228</li> <li>229</li> </ul>                                        |

| A<br>B | Sem<br>A.1<br>A.2<br>Prot<br>B.1<br>B.2<br>B.3        | antics f<br>Static S<br>Path R<br>otype D<br>ASCII<br>Examp<br>Algori<br>Model<br>Basic C                   | for DORIS Semantics for DORIS Semantics for DORIS                                                                                                                                                                                                         | <ul> <li>213</li> <li>213</li> <li>216</li> <li>223</li> <li>225</li> <li>228</li> <li>229</li> <li>229</li> </ul>                           |

| A<br>B | Sem<br>A.1<br>A.2<br>Prot<br>B.1<br>B.2<br>B.3<br>PVS | antics f<br>Static S<br>Path R<br>otype E<br>ASCII<br>Examp<br>Algori<br>Model<br>Basic C<br>C.1.1          | for DORIS         Semantics for DORIS         Semantics for DORIS         Sesolution Algorithm         DORIS Tool         Syntax for DORIS Systems         ole         thm         thm         of Timed CSP         Concepts         Events and Alphabets | <ul> <li>213</li> <li>213</li> <li>216</li> <li>223</li> <li>225</li> <li>228</li> <li>229</li> <li>229</li> </ul>                           |

| A<br>B | Sem<br>A.1<br>A.2<br>Prot<br>B.1<br>B.2<br>B.3<br>PVS | antics f<br>Static S<br>Path R<br>otype I<br>ASCII<br>Examp<br>Algori<br>Model<br>Basic C<br>C.1.1<br>C.1.2 | for DORIS Semantics for DORIS Semantics for DORIS                                                                                                                                                                                                         | <ul> <li>213</li> <li>213</li> <li>216</li> <li>223</li> <li>225</li> <li>228</li> <li>229</li> <li>229</li> <li>229</li> <li>230</li> </ul> |

| A<br>B | Sem<br>A.1<br>A.2<br>Prot<br>B.1<br>B.2<br>B.3<br>PVS | antics f<br>Static S<br>Path R<br>otype E<br>ASCII<br>Examp<br>Algori<br>Model<br>Basic C<br>C.1.1          | for DORIS         Semantics for DORIS         Semantics for DORIS         Sesolution Algorithm         DORIS Tool         Syntax for DORIS Systems         ole         thm         thm         of Timed CSP         Concepts         Events and Alphabets | <b>213</b><br>213<br>216<br><b>223</b><br>225<br>228<br><b>229</b><br>229<br>229<br>230<br>230                                               |

|     |       | C.1.5   | Observations: Timed Failures | 231 |

|-----|-------|---------|------------------------------|-----|

|     |       | C.1.6   | Useful Functions             | 231 |

|     | C.2   | Interfa | Ice                          | 232 |

|     |       | C.2.1   | Base Processes               | 232 |

|     |       | C.2.2   | Derived Processes            | 234 |

| D   | IDA   | Progra  | ms                           | 237 |

| Gl  | ossar | у       |                              | 243 |

| Gl  | ossar | y of Sy | mbols                        | 251 |

| Bil | oliog | raphy   |                              | 255 |

# **List of Figures**

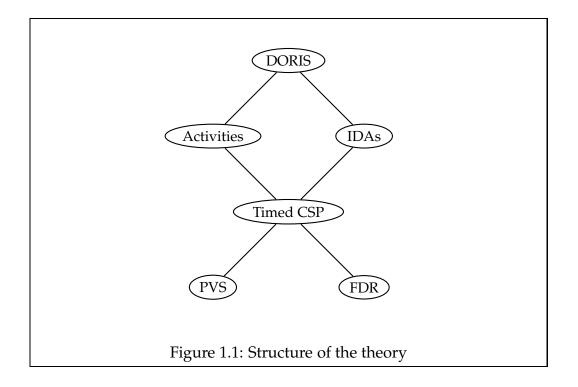

| 1.1               | Structure of the theory 26                                                                   |

|-------------------|----------------------------------------------------------------------------------------------|

| 2.1<br>2.2<br>2.3 | An example MASCOT-3 system32Syntax for untimed CSP35Syntax for Timed CSP38                   |

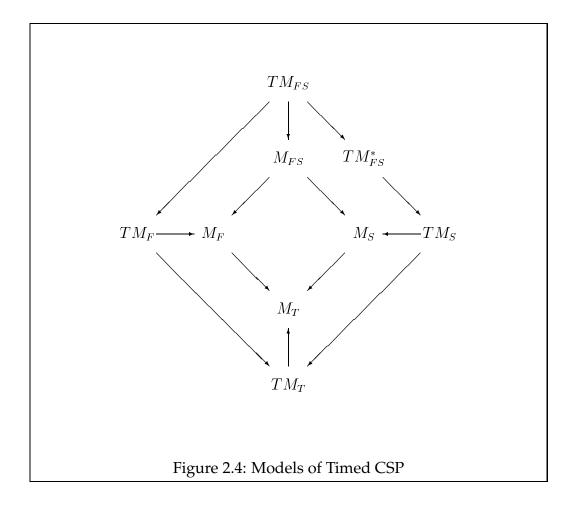

| 2.4               | Models of Timed CSP                                                                          |

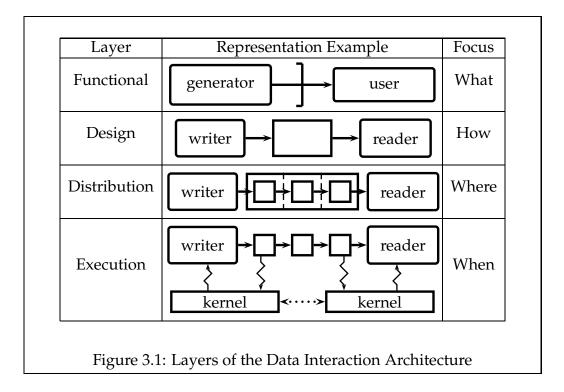

| 3.1               | Layers of the Data Interaction Architecture                                                  |

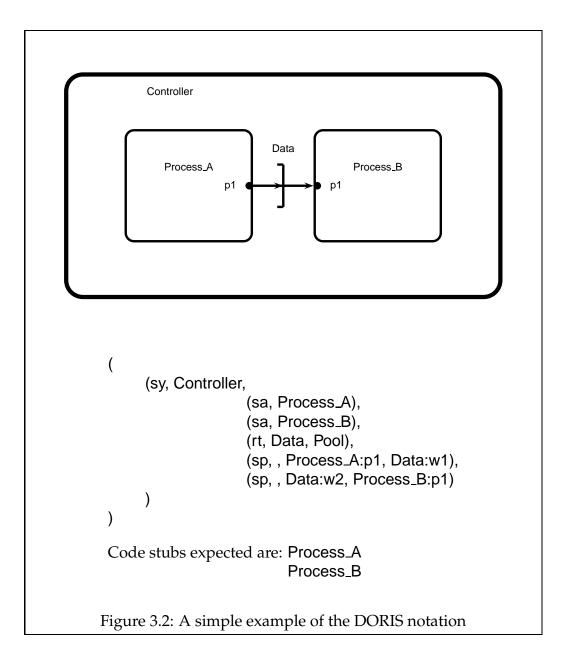

| 3.2               | A simple example of the DORIS notation                                                       |

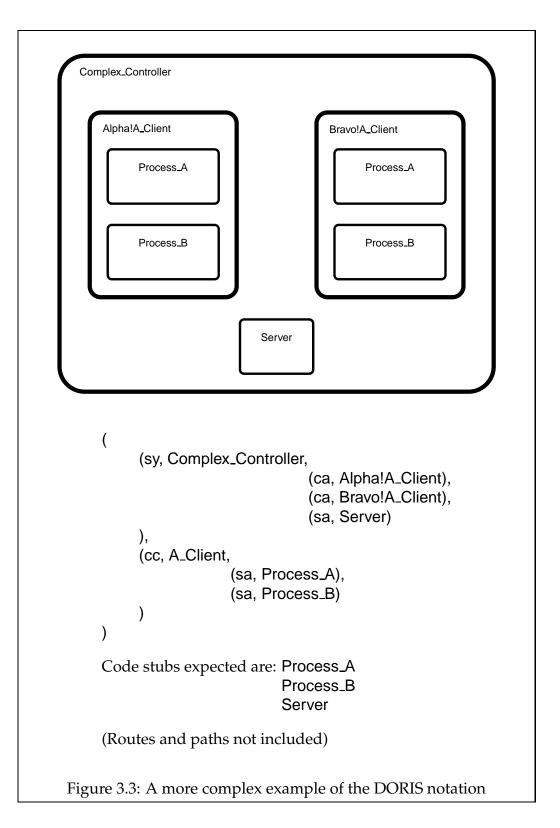

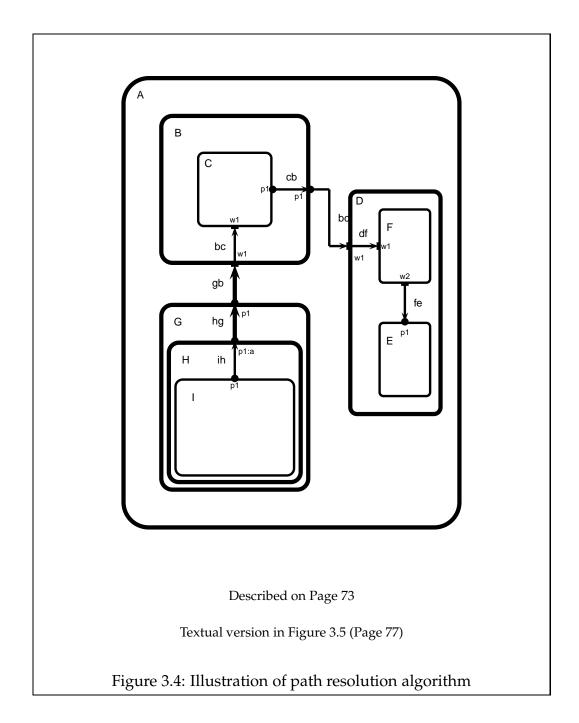

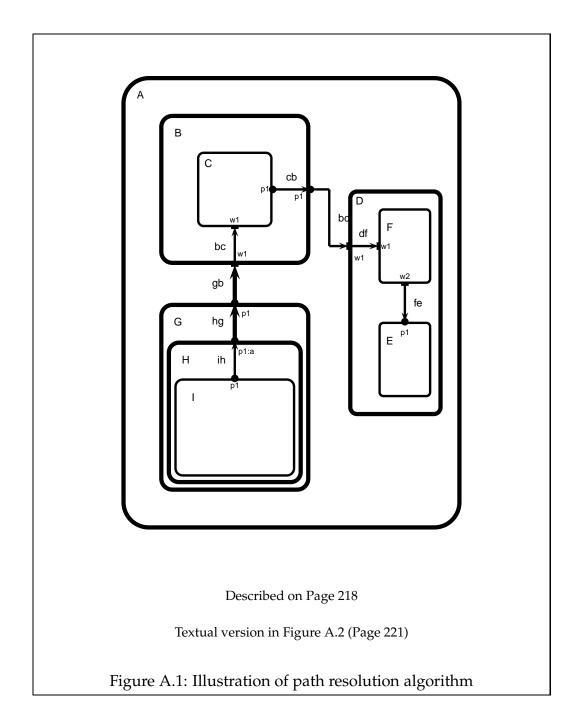

| 3.3<br>3.4        | A more complex example of the DORIS notation 60<br>Illustration of path resolution algorithm |

| 3.5               | Textual statement of path resolution example                                                 |

| 4.1               | Lamport's shared variables (Figure 5 [59])                                                   |

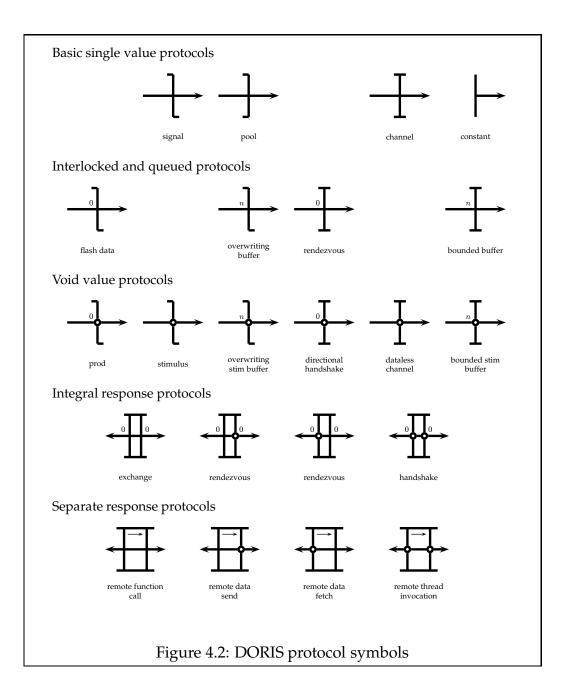

| 4.2               | DORIS protocol symbols                                                                       |

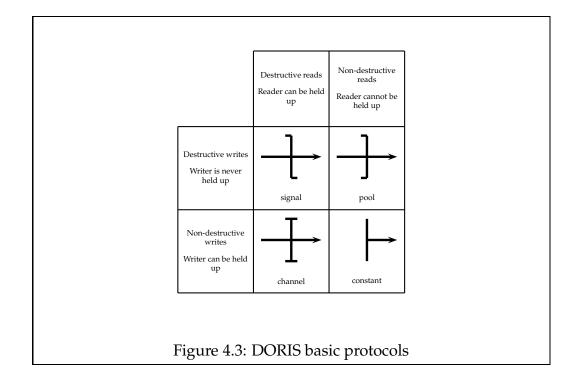

| 4.3               | DORIS basic protocols 85                                                                     |

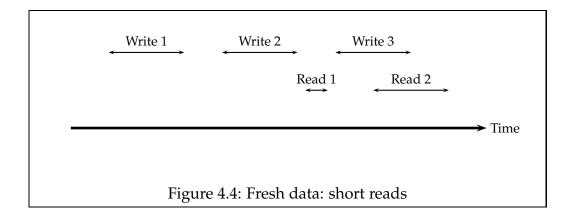

| 4.4               | Fresh data: short reads                                                                      |

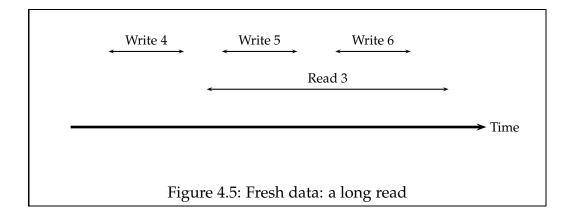

| 4.5               | Fresh data: a long read                                                                      |

| 4.6               | 'Unbounded buffer' composition of routes 100                                                 |

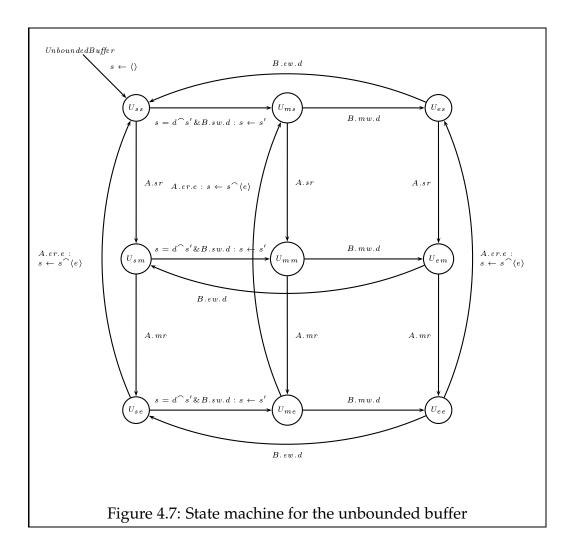

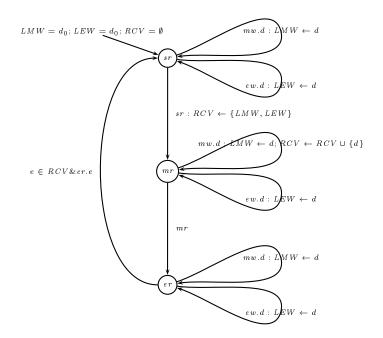

| 4.7               | State machine for the unbounded buffer                                                       |

| 4.8               | Simple forwarding across transputer links                                                    |

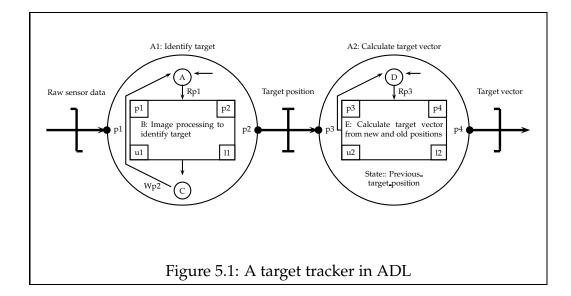

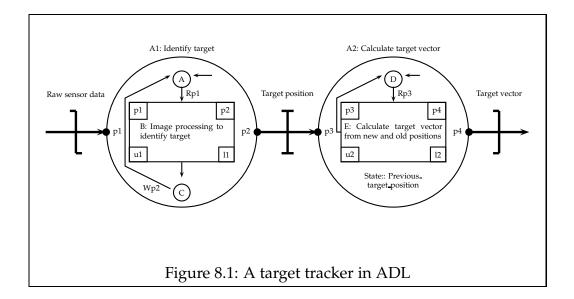

| 5.1               | A target tracker in ADL                                                                      |

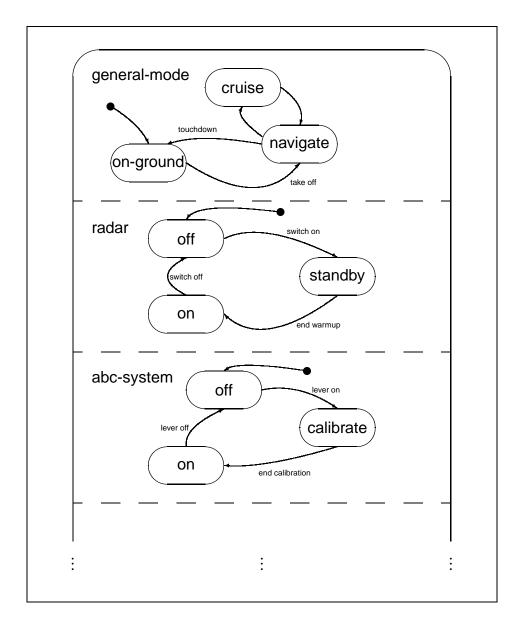

| 5.2               | Statechart for part of an avionics system                                                    |

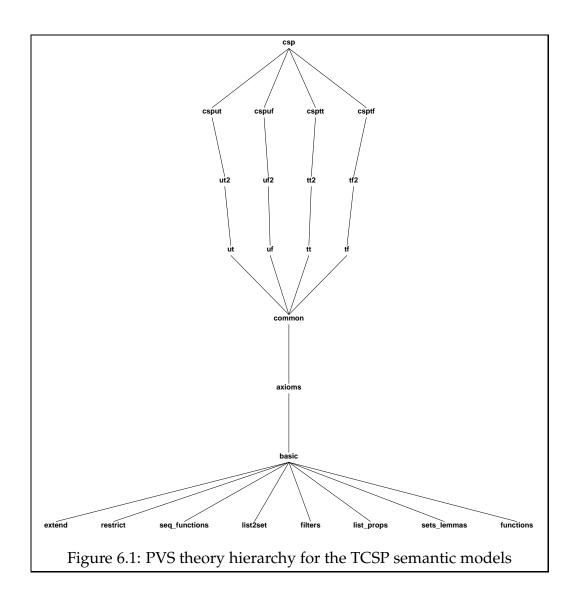

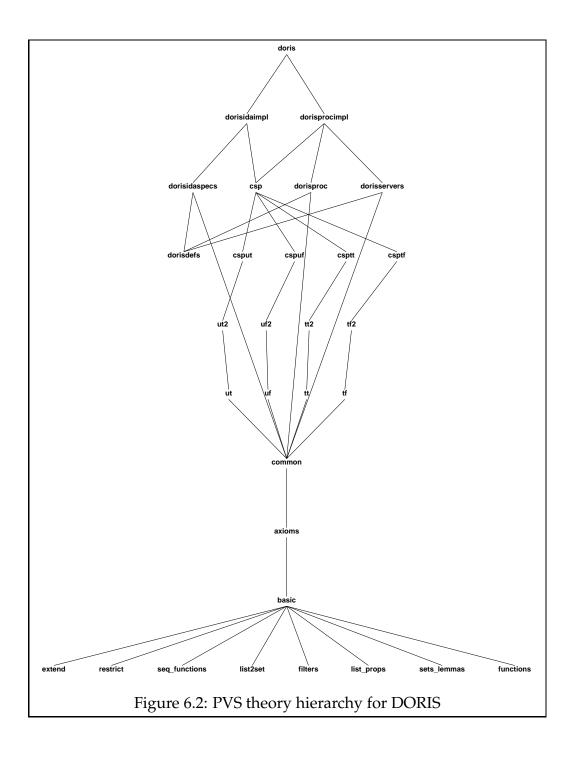

| 6.1               | PVS theory hierarchy for the TCSP semantic models 138                                        |

| 6.2               | PVS theory hierarchy for DORIS                                                               |

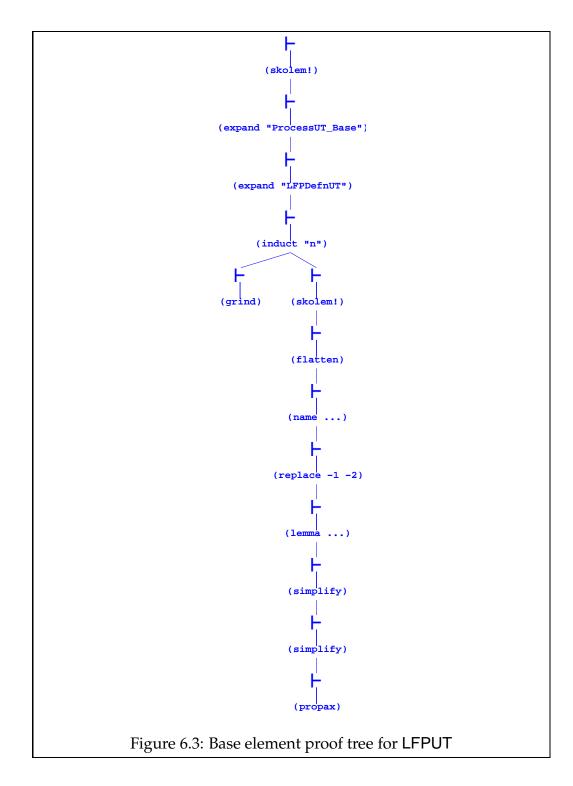

| 6.3               | Base element proof tree for LFPUT                                                            |

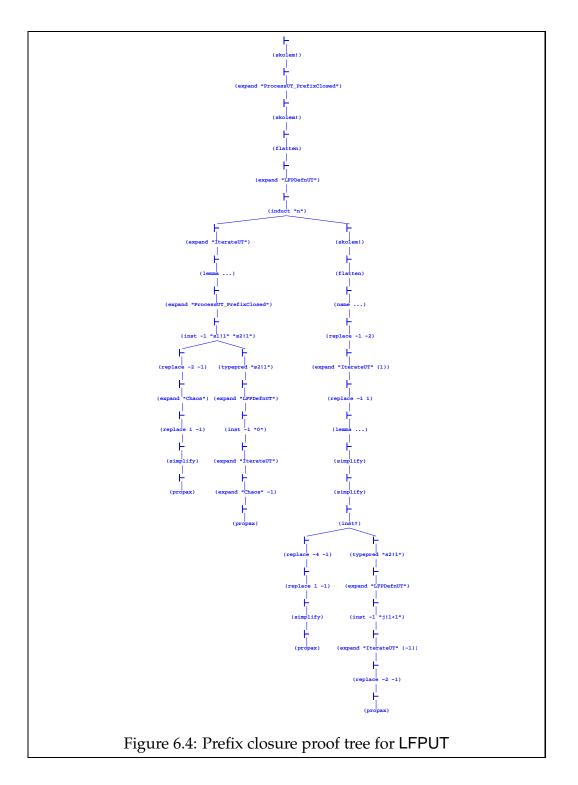

| 6.4               | Prefix closure proof tree for LFPUT                                                          |

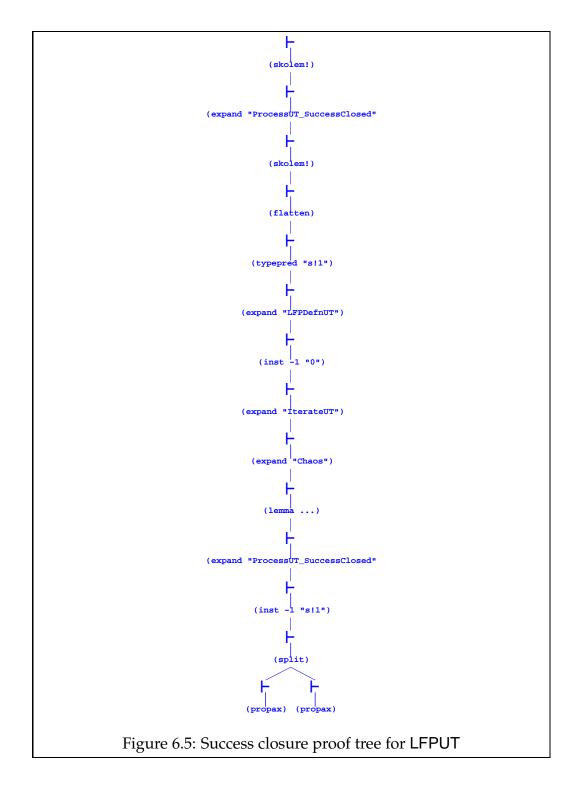

| 6.5               | Success closure proof tree for LFPUT                                                         |

| 7.1 | Results of composition of untimed IDAs                          |

|-----|-----------------------------------------------------------------|

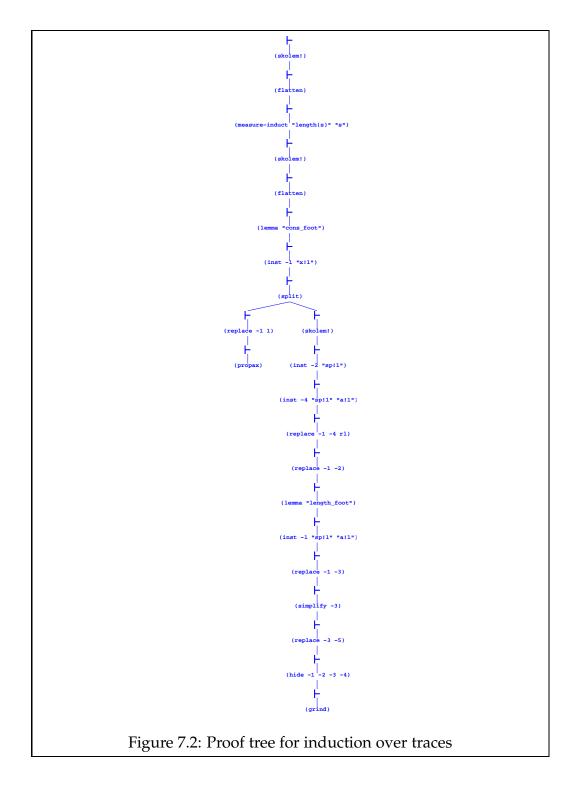

| 7.2 | Proof tree for induction over traces                            |

| 8.1 | A target tracker in ADL                                         |

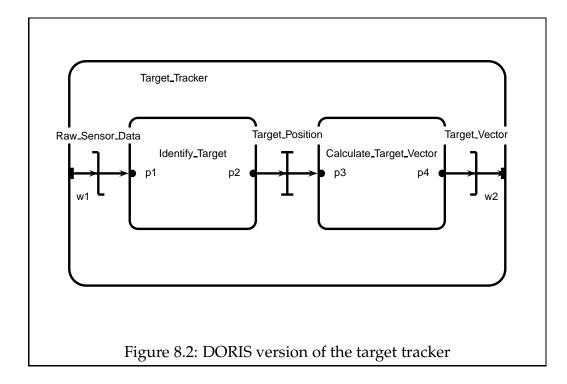

| 8.2 | DORIS version of the target tracker                             |

| 8.3 | Textual statement of small case study                           |

| 8.4 | Code stub for Identify_Target                                   |

| 8.5 | Code stub for Calculate_Target_Vector                           |

| 8.6 | dt input file for the small case study                          |

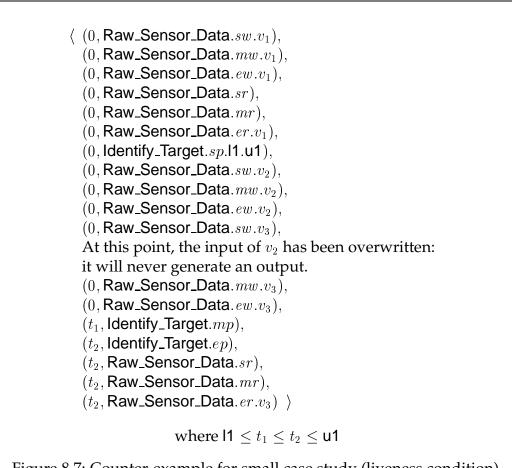

| 8.7 | Counter-example for small case study (liveness condition) . 184 |

| 8.8 | Breakdown of large case study by DORIS type                     |

| A.1 | Illustration of path resolution algorithm                       |

| A.2 | Textual statement of path resolution example                    |

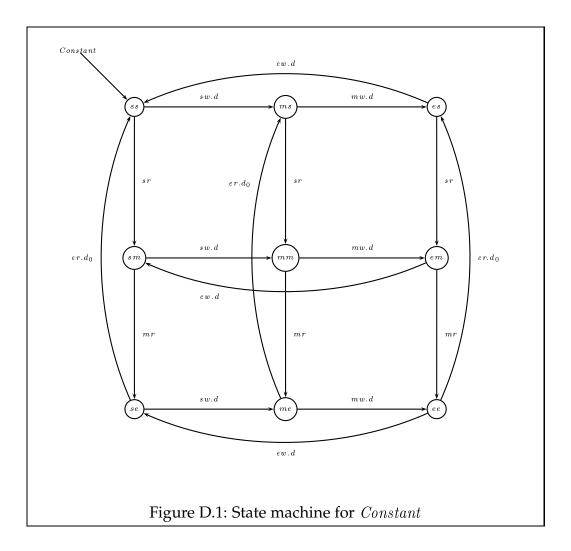

| D.1 | State machine for <i>Constant</i>                               |

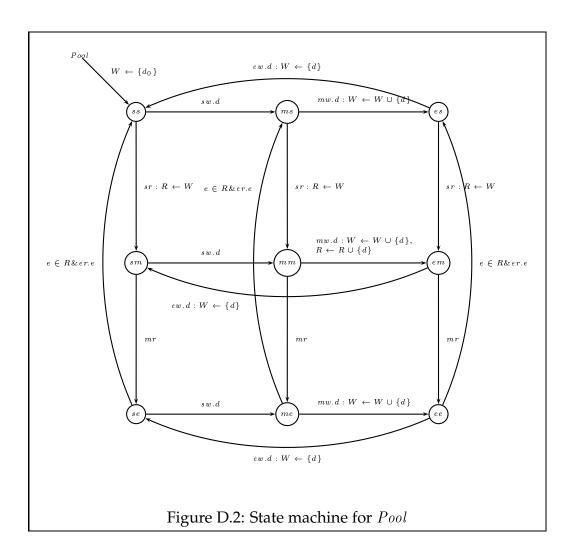

| D.2 | State machine for <i>Pool</i>                                   |

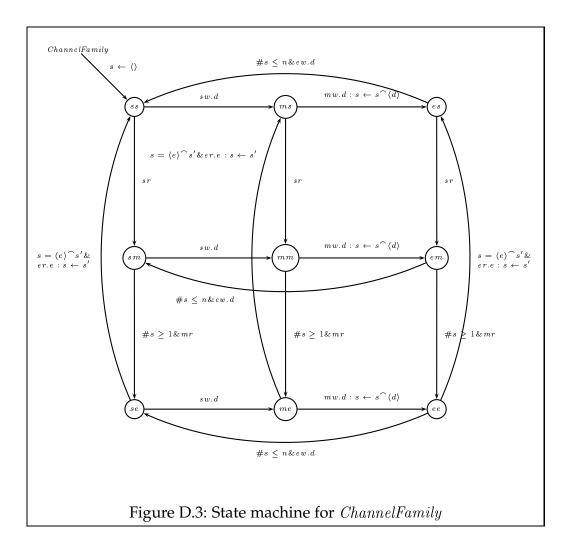

| D.3 | State machine for <i>ChannelFamily</i>                          |

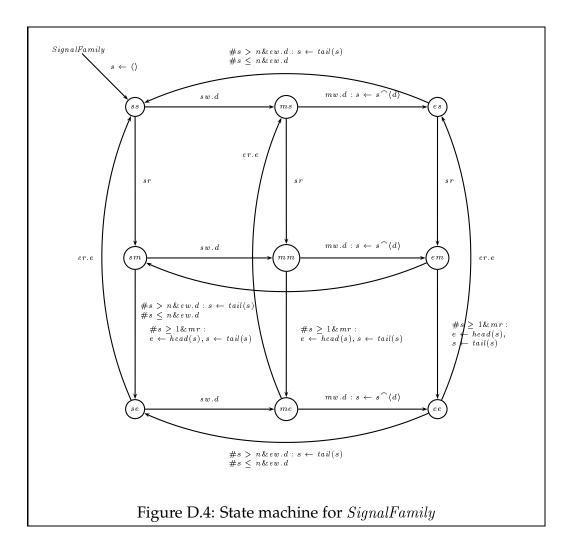

| D.4 | State machine for <i>SignalFamily</i>                           |

#### Acknowledgements

I would like to thank many people, in particular:

Professor John McDermid, Stephen Paynter (my industrial supervisor), Jim Armstrong, Hugo Simpson, Richard Paige, and Dave Stringer-Calvert, who have offered me much advice and critical feedback on my work.

The examiners, Steve Schneider and Alan Wood.

My supervisor, Jeremy Jacob.

Darren Buttle, Simon Fowler, and Darren Priddin, for being happy to talk about anything not to do with this work.

EPSRC and British Aerospace for funding this work under the ROPA and CASE schemes.

#### **Author's Declaration**

This thesis is the result of my own original work (except where explicitly noted), and has not been submitted for any other qualification at any other university.

An earlier version of the work on the pool IDA contained in Chapters 4 and 7 has been presented at the Northern Formal Methods Workshop, and subsequently published in the proceedings of that workshop [9].

## LIST OF FIGURES

# Part I

# Introduction and Survey

# Chapter 1 Introduction

# 1.1 Motivation

#### 1.1.1 Problem Domain

British Aerospace (BAe) embed large, complex, concurrent computer systems in some of their products. Many of these systems are *safety critical*: a failure could lead to loss of life or other undesirable consequences. The particular computer systems that BAe are immediately concerned with are the *embedded* applications which control aircraft, both piloted and pilotless.

These applications interact with the real world in a complex way, and so they are often very complex systems themselves.

#### 1.1.2 General Approach

When building computer systems, one general problem is to minimise the likelihood of a failure of these systems.

One approach to minimise the failure rate is 'testing'. Testing is an important part of the software engineering process, but cannot find all errors, since it would take an infeasible amount of effort to test every set of inputs to the system.<sup>1</sup> These systems, moreover, are often *reactive*, *i.e.* they respond to events from the environment in which they are embedded. The generation of responses to these events is often required to be within a

<sup>&</sup>lt;sup>1</sup>Here, we take 'a set of inputs' to mean the entire history of a particular execution. This means that every possible input at each possible state of the system should be tested.

deadline. This makes the testing problem worse; a complex test harness needs to be constructed for these systems.

The problem of building complex computer systems is recognised, and careful design can help reduce the number of faults. As Drew Hamilton has stated, 'no one intentionally writes bad code' [37]. Despite this, faults do occur in practice, so many (defence) contractors are required to conform to a specific software engineering standard (*e.g.* Defence Standard 00-55 [17]). These standards often involve formal methods (techniques and tools based on mathematical modeling and formal logic), in addition to testing.

#### 1.1.3 MASCOT and DORIS

We now turn our attention to the methods for designing such systems. There are a large number of notations and methods available. In this thesis, we concentrate on those methods used by BAe,<sup>2</sup> which include the Modular Approach to Software Construction, Operation, and Test (MAS-COT) [67, 107], the Data Oriented Requirements Implementation Scheme (DORIS) [110, 112], and Statecharts [39]. All of these notations are 'hierarchical'; *i.e.* some constructs can be decomposed hierarchically: they can be refined to other constructs which may themselves be decomposed.

The design notation within DORIS (which is very similar to MASCOT-3's design notation) deals with the architectural structure of the system, and consists of activities (processes) communicating with each other and their environment via 'inter-communication data areas' (IDAs, *a.k.a.* routes or protocols). The MASCOT notation has been studied (Paynter produced an abstract formalisation of MASCOT in his thesis [84]), although not in the timed domain.

#### 1.1.4 Reasoning about Designs

The notations mentioned above (MASCOT and Statecharts) use diagrams. When such a diagram is drawn to denote a system, we have some idea of what it means: we understand the semantics of the system, even if only informally. Importantly, the writer may have intended a different meaning

<sup>&</sup>lt;sup>2</sup>British Aerospace and EPSRC funded the work in this thesis: the overall problem that this thesis addresses is broadly constrained by these interests.

to the meaning that a particular reader infers. If we want to reason more precisely about the system, we need to use mathematical reasoning. To do this, we need to define the semantics of the notation more formally.

It is not trivial to define such a semantics. For instance, over 20 attempts to give a semantics to Harel's Statecharts have been published (von der Beeck has surveyed a number of these [6]), and none of these are entirely satisfactory. Other graphical notations also have problems of ambiguity, illustrated by both Leveson [64] and Baresi [3]. As discussed in an earlier literature survey [10], there are persistent problems.

Many applications must satisfy timing requirements for their functional output to be useful. For example, a fly-by-wire flight control system that generates the correct commands to the control surfaces of an aircraft ten minutes after the pilot's input will result in the loss of the aircraft. The timing requirements, *e.g.* the commands will be generated within (say) 10 milliseconds of input, are an important part of the specification.

This explicit introduction of time presents much of the complication in producing useful models of systems. State machines can be constructed to model systems, but modelling time introduces a very large (or even infinite) state space.

A separate problem concerns the interaction of concurrent processes. Such processes often communicate through shared variables. This interaction complicates analysis of the functional and timing properties of a given system. This is the motivation for the DORIS IDAs 'decoupling' of concurrent processes (*i.e.* separating the description of how and when data is transferred between the processes from the description of what data is transferred).

There is other work on the behaviour of concurrent variables. For instance, Lamport has described three types of shared variable, safe, regular and atomic, which can be considered as particular types of IDAs [59]. In this thesis, we use Lamport's variables as the primitive components out of which we implement the DORIS IDAs.

#### 1.1.5 Application of Formal Methods

As well as defining the semantics of a system, we need to be able to apply these semantics productively. Formal methods addresses this by using specific tools and techniques to determine properties of the system from the semantics.

There is an increasingly wide range of tools. Some are theorem provers (they assist a human user in performing a traditional proof); others are state space exploration tools (they attempt to search the entire state space of the system). Others simulate, or animate, systems — this is especially useful for design prototyping, since a system can only be formally checked against a formal set of requirements.

Finally, we note that formal methods are still not widely accepted in industry [48]. We suggest the following analogy: that the formal notations currently used (say, in Timed CSP [20]), are still at the level of machine code, whereas system designers need more abstract notations, at the level of high-level programming languages.

## **1.2** Contribution of this Thesis

The aim of the work described in this thesis is to produce a semantics for a hierarchical design notation in such a manner that it is acceptable to a wide range of software engineers, *e.g.* those working on systems like the large case study in this thesis (Section 8.5, Page 185). This must allow the construction of larger components that reflect the application domains where the notation is used, thus enabling functional decomposition of systems. Finally, the semantics should also be effectively machine supported.

### **1.3 Development of Ideas**

This thesis describes the design notation within the DORIS method — it is a hierarchical design notation used in industry.

We give this notation a BNF-style grammar, and outline a Timed CSPbased semantics for the syntax that allows systems to be constructed hierarchically. Each component of a system either includes other components (using a Timed CSP parallel composition operator), or is a primitive component that can be represented by carefully constructed Timed CSP expressions.

The two types of primitive components in DORIS are the IDAs (shared variables) and activities.

The IDAs are defined by specifying their behaviour. This is not trivial, as the IDAs can have writes and reads occurring concurrently. We investigate the IDAs further by exploring how they can be implemented in terms of Lamport's shared variables, and how compositions of IDAs behave.

Activities are abstractions of the 'processing' parts of a system. In the semantic model, they are Timed CSP expressions that interact with the activity's environment, and represent the passing of time spent calculating results. To aid the modelling of real systems, we define a simple language containing loops, termination, choice, input, output, and 'calculation', which translates into Timed CSP.

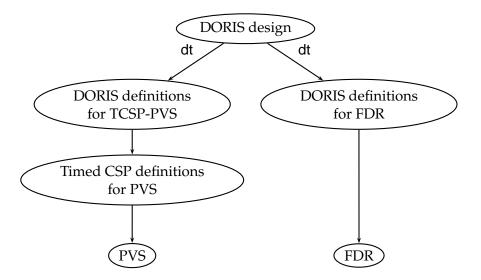

At this point, we can take a DORIS design, and translate it into Timed CSP. This is detailed work, and is aided by a tool specifically written for the purpose, named dt. This tool generates output intended to be used with a PVS [15, 79, 80, 96, 105] embedding of Timed CSP semantic models, or for input to FDR [28]. Using these tools, we can attempt to show, by machine proof, or state space exploration, that particular properties hold. These two tools are used as complementary approaches to applying our semantics for DORIS.

# 1.4 Overview

The thesis is in four parts. The first part contains this introduction, and a brief background survey. More details of relevant literature are given in each chapter as needed.

The second part presents the theoretical semantics for DORIS: Chapter 3 presents an overview of DORIS, and provides the overall framework for the following two chapters, which concern the definition of IDAs (Chapter 4) and activities (Chapter 5).

We then turn our attention to the mechanical support of this work in the third part. This starts with Chapter 6, where our method is described. The mechanical methods devised are then used in Chapter 7 to prove properties about IDAs.

Chapter 8 sets out two case studies. The first is based on a small example by Paynter *et al.* [83]. The second concerns a large design from British Aerospace. Subsequently, we report the analysis of these case studies.

The final part of the thesis consists of Chapters 9 and 10, which summarise this work, and discuss future possibilities.

Figure 1.1 illustrates the structure of the theory in this thesis: DORIS consists of two major parts, the IDAs and activities, both of which are given a semantics in terms of Timed CSP. Finally, mechanical support is provided by the PVS and FDR tools.

A glossary of terms, definitions and abbreviations, a glossary of symbols, and an annotated bibliography conclude the thesis.

# Chapter 2 Background Survey

In this chapter, we provide a general introduction and overview to the domain of critical systems engineering and formal methods (FM). We also introduce MASCOT and DORIS, and a process algebra, Timed CSP.

Throughout the rest of the thesis, further material is introduced where it is needed. An annotated bibliography is also provided (Page 255).

### 2.1 Critical Systems

The systems that BAe typically use DORIS to design are *safety* or *mission critical*. The failure of a safety critical system could result in the loss of life. A mission critical system failing will probably not result in loss of life, but could cause severe difficulties. For example, a weapon system failing to hit a target is mission critical, but the flight control system of a manned aircraft is safety critical.

A system which could potentially damage the wider environment can be considered safety critical: oil distribution systems could pollute a large area quickly; they are dependent on computer control of pumps and valves. Nuclear power plants are heavily dependent on their control systems to ensure safe operation.

Other systems can be described as critical systems: a company may depend on its computers to ensure that orders go to the right place on time: they are *business critical*. If such a system fails, it could cause the company to go out of business. A *security critical* system may allow information into the possession of unauthorised people, which could cause severe repercussions.

We can see that the concept of a critical system can encompass many domains and types of failure. However, they all have one common theme: they must operate reliably and robustly.

In many circumstances, it is impractical to test a critical system in its 'final' environment, *e.g.* an ambulance control system. Then how do we tell whether the system will work?

There are already many software engineering methods aimed at designing systems, *e.g.* SSADM. What is lacking in many of these methods is a way to reliably determine that the final system does exactly what it is meant to. Once designed and built, a system can be tested; however, testing cannot cover all possible circumstances (except for trivial systems).

More can be done: formal methods are still relatively under-used in industry, although defence contractors are often required to conform to safety standards that mandate formal methods.

# 2.2 Formal Methods

A NASA guidebook states that formal methods consist

"... of a set of techniques and tools based on mathematical modeling and formal logic that are used to specify and verify requirements and designs for computer systems and software." [75]

There are several important points here:

- formal methods are based on mathematical and logical techniques;

- formal methods consist of techniques and tools (otherwise they are of no use);

- computer systems as well as software are (sometimes) amenable to such analysis; and

- formal analysis of a computer system (or software) is based on a *model* of that computer system.

It is the last point that is particularly important: if a formal model of a washing machine concludes that the washing machine will always complete a programme that has been started, then is the analysis invalidated if the user disconnects the power supply during the programme? In this case, there would be an explicit or (more likely) an implicit assumption that the power supply always remains connected.

The issue here is that we must understand clearly what assumptions are made during the construction of a model: the analysis is not about the 'real' system. Barwise discusses this subject in some depth in a refutation of Fetzer's argument [29]. In his conclusions, Barwise says

"[Articles critical about computer system correctness] will help to generate an improved understanding among professionals and the public of what such proofs show and what they do not show about the correctness of physical computers operating in the real world." [4]

Jackson makes some similar points in his short articles [52].

Much of the rationale for formal methods in software engineering relies on the distinction between traditional engineering disciplines and the problems with writing software. These problems are twofold:

- 1. Software is discrete and discontinuous. A small change to source code or system input can have a large effect on the behaviour of the overall system. Most engineering systems (*e.g.* bridges) have a range of tolerances that can be exploited to give a margin of safety.

- 2. The sheer complexity of software and the bespoke approach to the construction of software allows design flaws to be easily missed. The interaction of even a moderate number of complex components vastly increases the overall complexity of the system.

The reader is recommended to read Rushby's introduction where these issues are more fully discussed [97].

Another useful reference is the two-volume NASA guidebook [75,76]. This is a wide-ranging, thorough, and quite readable guidebook. It serves well as an overall reference into formal methods techniques.

Although formal methods are not widely used, there is no reason why they should not be used in the development of all software, except for the (perceived) cost of using FM for a system that simply does not warrant the level of assurance required.<sup>1</sup>

# 2.3 MASCOT and DORIS

Since DORIS draws much of its notation and methodology from MASCOT, it is appropriate to first introduce MASCOT.

### 2.3.1 MASCOT

The Modular Approach to Software Construction, Operation, and Test (MASCOT) incorporates:

- a means of design representation,

- a method for deriving the design,

- a way of constructing software so that it is consistent with the design,

- a means of executing the constructed software so that the design structure remains visible at run-time, and

- facilities for testing the software in terms of the design structure [67].

MASCOT originated during the early 1970s, with an 'Official Definition of MASCOT' (*a.k.a.* MASCOT-1) being produced in 1978. This came about through work on embedded real-time systems. MASCOT-2 followed in the early 1980s, with the current standard (MASCOT-3) issued in 1987.

One of the motivations for MASCOT is the intangibility of (large) software systems. This causes difficulty in understanding how a particular system works. To address this, MASCOT, in common with many structured methods, approaches the problem top-down; *i.e.* the overall structure of the system is set out, with further refinements as more detail is required. The lowest level of design (in this context) is the source code in the target language.

MASCOT is not just a notation; it is a method. The MASCOT process has three distinct phases:

<sup>&</sup>lt;sup>1</sup>Of course, this does not prevent people using such software for critical purposes. For example, consider Wiener's example of a surgeon who used a spreadsheet to analyze data from a patient during open-heart surgery [119, Page 128].

- **Network Design** An iterative process which creates a hierarchy of subsystems, IDAs and servers (all described below). This phase identifies the purpose of each component.

- **Component Design** Each of these components is (if necessary) refined into more components (activities). The bottom-level activities are then designed and coded.

- **Integration and Test** Each component is tested individually, then with its neighbours, and so on, until the whole system has been constructed.

- There are a number of component types referred to above:

- **System** This is the 'product' which the method aims to produce.

- **Subsystem** The system is broken down into functionally separate components called *subsystems*.

- **Server** The system interacts with its environment through sensors and actuators via servers (a specialised subsystem).

- Activities These are the parts of the system which perform the bulk of the 'work', *e.g.* calculations.

- **IDAs** Intercommunication Data Areas (IDAs) link the activities and servers together by allowing data to flow around the system in a controlled manner.

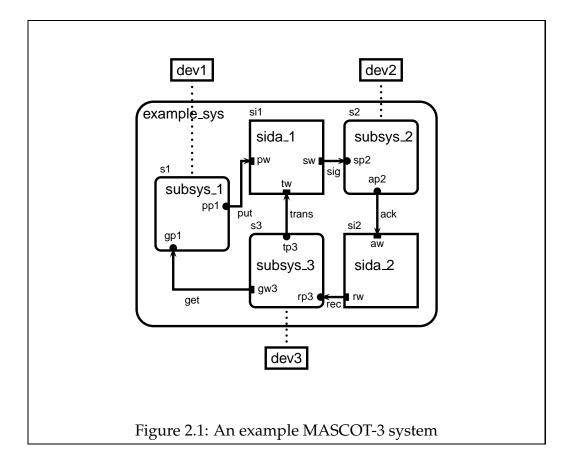

An example MASCOT-3 system is given in Figure 2.1, taken from Page 2-3 of the MASCOT-3 manual [67]. This example contains a system called 'example\_sys', which contains three subsystems (with round cornered boxes) and two IDAs (the square cornered boxes inside example\_sys). There are three devices through which the system communicates with its environment.

An important feature to note is the distinction between *ports* and *windows*. The ports are represented by the small disks on the edge of an activity at the end of a path (*e.g.* ap2 in subsys\_2). A window is represented by a small filled-in rectangle (*e.g.* aw in sida\_2). The action associated with a window is considered to be passive, and is driven by the active end, indicated by the port. In MASCOT and DORIS, paths may only connect a port

to a window or *vice versa*. Similarly, each port and window has a direction of data flow associated with it, which is indicated by the arrow heads.<sup>2</sup>

#### 2.3.2 **DORIS**

The primary reference for the Data Orientated Requirements Implementation Scheme (DORIS) is Simpson's *Methodological and Notational Conventions in DORIS Real Time Networks* [110].

DORIS is a wide-ranging method primarily intended for applications using real-time networks, and is itself a British Aerospace product. It includes concepts drawn from MASCOT-2 and MASCOT-3, (DORIS is very closely related to MASCOT-3) as well as the Controlled Requirements Expression (CORE) method [16]. DORIS covers a wide span of the computer system and software development process.

This chapter does not describe DORIS any further. Instead, Chapter 3 describes the DORIS notation itself (Page 53).

The IDAs (which can be treated as shared variables) are discussed in Chapter 4. Two broad classes of shared variables are discussed, in Section 4.2 (Page 81): Simpson's (DORIS) IDAs [112] and Lamport's safe, regular and atomic variables [59].

Part of the DORIS notation includes MASCOT-3-like activities. We introduce a simple language to describe these activities in Chapter 5. Section 5.1 (Page 111) describes two alternative approaches: the Activity Description Language (ADL) [83] and Statecharts [40].

## 2.4 Communicating Sequential Processes

This thesis uses Hoare's Communicating Sequential Processes (CSP) [46] as the semantic domain for the DORIS notation (see Chapter 3, Page 53 for the rationale). CSP is a mathematical approach to the study of concurrency and communication. It has been extended to incorporate real-time in Timed CSP (TCSP) by Reed and Roscoe [92], and further developed by Schneider [100], and Davies [23].

<sup>&</sup>lt;sup>2</sup>Strictly, path fragments from a port to another port (or one window to another) are allowed. This occurs when hierarchical constructs are involved. Similarly, bidirectional paths are permitted: in this thesis, they are represented as two unidirectional paths.

Davies and Schneider's paper *A Brief History of Timed CSP* [20] describes the untimed and timed models. (Other summaries have also been produced [18].) Roscoe has recently published a text covering untimed CSP [95], and Schneider's forthcoming book covers Timed CSP [102].

#### 2.4.1 Model of Computation

A *program* is a term in the syntax of CSP, and a *process* is an element of a semantic model. There are a number of different models, corresponding to different types of *observations*.

An observation is a record of the entire history of a particular execution of a process. In one of the simplest CSP models,<sup>3</sup> a CSP process interacts with its environment via synchronisations called *events*. They are considered to occur at a specific point in time, and have no duration. They occur only with the agreement of both the process and the environment that it is placed in.

The sequence of events that occur is known as a trace, and traces are the observations in the untimed traces semantic model. (We will use several semantic models of CSP in this thesis.)

There are several assumptions underlying this model of computation:

- **Maximal progress** A program will execute as many internal (hidden) events as possible.

- **Maximal parallelism** We assume that there are no restrictions such as scheduling limits. (Later in the thesis, we will restrict the amount of work each activity can do by explicitly modelling a scheduler.)

- **Finite variability** A program may only undergo finitely many state changes in a finite amount of time.

- **Synchronous communication** Each communication event requires the simultaneous participation of all involved programs.

Instantaneous events The events have no duration.

<sup>&</sup>lt;sup>3</sup>There are simpler CSP models, but this (untimed traces) model is the simplest commonly used.

$$P ::= Stop \mid Skip \mid a \to P \mid P; P \mid P \Box P \mid P \sqcap P$$

$$\mid a : A \to P_a \mid f(P) \mid P \setminus A \mid P \parallel P \mid P \parallel ||P$$

$$\mid P \parallel_A P \mid \parallel_{A_i}^i P_i \mid \mu X \bullet F(X)$$

Our definition of CSP will be drawn primarily from the paper cited above by Davies and Schneider [20], Schneider's more recent description [101], and the two books by Roscoe and Schneider [95, 102].

#### 2.4.2 Untimed CSP

The language of untimed CSP has the syntax in Figure 2.2. We briefly describe this notation.

'*Stop*' is the program which will do nothing; it will never interact with its environment. *Stop* can model a broken printer: it will never accept any jobs; it can do nothing at all.

' $\rightarrow$ ' is called 'prefix'; ' $a \rightarrow P'$  is the program which engages in the event a, and then behaves as P. For example,  $coin \rightarrow Stop$  is the process which engages in a *coin* event, and then does nothing.

'Skip' does nothing, except terminate successfully by engaging in the special termination event ' $\checkmark$ ' (pronounced 'tick' or 'success'). Sequential composition is denoted by ';'. The sequential composition of two processes, *P* and *Q*, ('*P*; *Q*') behaves at first as *P*. If *P* terminates successfully (*i.e. P* engages in ' $\checkmark$ '), the composed process then behaves as *Q*. Thus the process  $coin \rightarrow Skip$ ;  $coin \rightarrow Stop$  can engage in two *coin* events before behaving as Stop again.

'*P*  $\square$  *Q*' means that the environment may choose between *P* and *Q* (external choice), whereas '*P*  $\sqcap$  *Q*' results in *P* or *Q* being chosen nondeterministically (internal choice). The distinction here is important when considering liveness properties of a process: external choice will offer both possible processes; internal choice does not have to.

' $a : A \rightarrow P_a$ ' (general, or menu choice) offers a first event from the (possibly infinite) set *A*. The environment can choose any of the events in *A*: suppose it chooses *a*. Once the event *a* has occurred, the process *a* :

$A \rightarrow P_a$  then behaves as  $P_a$ . This allows the parameterisation of processes based on the particular event.

This permits the modelling of communication along channels with additional syntax. If a data channel c can pass values from a set D, then for any  $d \in D$ , c!d means 'write the value d on channel c', and is defined as c.d, where c.d is a compound event. (Compound events are simply events with additional structure: they have no special meaning, except for simplying descriptions. For instance, if we are only interested that some event, c.doccurs, but are not worried what the specific d is, we may write c.)

Similarly, reading from the channel *c* is written  $c?x : D \to P_{c.x}$ , and is defined as  $e : \{x : D | c.x\} \to P_{c.x}$ . This use of structured syntax can be useful for structuring models of systems.

f(P)' is a program P, but with the events relabelled as dictated by f. This has a similar purpose to 'generic instantiation' in high-level programming languages.

$P \setminus A'$  is the program *P*, but with the events in the set *A* hidden from the environment. Such hidden events do not need the cooperation of the environment, and occur as soon as *P* can perform them.

The program ' $P \parallel_A Q$ ' is the parallel combination in which P and Q synchronise on the events in  $A \cup \{\checkmark\}$ , and interleave all other events.  $\checkmark$  is included in the set of events to synchronise on because both processes must agree to terminate successfully. (This particular variant of parallel composition is often known as 'hybrid parallel'.)

The program 'P || Q' denotes 'synchronising parallel', where P and Q cooperate on all events in the intersection of the alphabets of P and Q. The asynchronous (shuffle) parallel operator, 'P || |Q' is the program where events of P and Q are interleaved, except for  $\checkmark$ , which P and Q must cooperate on. Both of these parallel operators can be defined in terms of the hybrid parallel operator.

The final parallel operator is the 'network parallel' (*a.k.a.* general(ised), or interface parallel): ' $||_{A_i}^i P_i'$ . This takes a number of processes,  $P_i$ , each of which has an associated alphabet  $A_i$ , called the 'interface'. For a particular event to occur, then every process  $P_i$  which has that event in its interface must agree on that occurrence.  $||_{A_i}^i P_i$  is sometimes written in the form  $||_i(P_i, A_i)$  or  $||\{(P_i, A_i)\}$ .

Recursive programs, such as ' $\mu X \bullet F(X)$ ', uniquely satisfy P = F(P)(in the untimed models) if F is guarded. ( $\mu X \bullet F(X)$  always has a welldefined semantics in the untimed models.) F is guarded in untimed CSP if every free occurrence of *X* is preceded by at least one observable (*i.e.* non-hidden) event.

There are a number of semantic models for (untimed) CSP. The simplest presented here is based on observations of events engaged in by the program with its environment. This is known as the traces model. For a program P, Traces(P) is the set of all possible sequences of observable events that P may engage in.

By using trace specifications, we can capture safety properties.<sup>4</sup> For example,

$$\forall tr \in Traces(P) \quad \bullet \quad tr = \langle \rangle$$

requires that *P* never performs any observable event. (This entire expression is often abbreviated to  $tr = \langle \rangle$ , where it is understood that tr is the typical trace.) The relation *P* sat *S* means

$$\forall tr \in Traces(P) \bullet S(tr)$$

where *S* is a predicate, *i.e.* every trace in *P* satisfies the specification *S*.

A clock that ticks has a specification with an infinite set of traces.

$$tr \in \{\langle\rangle, \langle tick\rangle, \langle tick, tick\rangle, \ldots\}$$

This can be satisfied by the recursive program

$$\mu X \bullet tick \to X$$

We can use *refusal sets* to capture liveness (readiness) properties. A refusal set records the events that the process will not engage in. This allows us to define specifications that state that under certain circumstances, the process is not allowed to refuse an event. Even if the environment is not prepared to engage in that event, the process cannot itself refuse it.

The typical refusal set is denoted by rf. A failure is a pair (tr, rf), which means that the program has been observed to engage in the trace tr, and will deadlock if only the events in rf are offered by the environment. For example, we may specify a machine that cannot refuse to produce a chocolate, if the last event engaged in was accepting a token:

$$last(tr) = token \implies chocolate \notin rf$$

<sup>&</sup>lt;sup>4</sup>In this context, 'safety properties' are not necessarily related to 'safety' in the sense of 'safety critical'. Here, safety properties constrain which traces may occur.

$$P ::= Stop \mid Skip \mid Wait t \mid a \to P \mid P; P \mid P \square P$$

$$\mid P \sqcap P \mid a : A \to P_a \mid P \stackrel{t}{\triangleright} P \mid P \swarrow t P$$

$$\mid f(P) \mid P \setminus A \mid P ||P \mid P |||P \mid P ||_A P$$

$$\mid ||_{A_i}^i P_i \mid \mu X \bullet F(X)$$

Figure 2.3: Syntax for Timed CSP

The semantic model can be extended to include divergences. Divergences can model livelock. In Hoare's text [46], a divergence of a program P is a trace after which the program behaves as the *Chaos* process — the most nondeterministic process possible. An alternative treatment (originally due to Reed [93]) associates a stability value (0 or  $\infty$ ) with each trace or failure. If the stability value is  $\infty$ , then the program diverges after performing *tr*.

#### 2.4.3 Timed CSP

In the untimed traces model, the interval between two consecutive events could be from one millisecond to several million years: we simply do not have that information available. Sometimes, we might want to know exactly how long a particular interval was between two such events. Timed CSP (TCSP) is an extension of untimed CSP to include this timing information.

There are a number of variants of Timed CSP. CSP was originally extended by Reed and Roscoe [92, 93]. Schneider's and Davies' doctoral theses build on this work [23, 100]. As noted above, Schneider has a forthcoming book on the subject [102].

Timed CSP has the syntax in Figure 2.3 (similar to the syntax in Figure 2.2). Times, *t*, are non-negative real numbers. No lower bound is placed on the interval between consecutive events.

There are three new constructs: *Wait* (delay),  $\stackrel{t}{\triangleright}$  (timeout), and  $\swarrow_{t}$  (timed interrupt):

'*Wait t*' does nothing for time *t*, and then behaves as *Skip*.

The program  $P \triangleright Q'$  is a timeout: if *P* engages in no events before time *t* has passed, then the program behaves as *Q*. If the first event of *P* occurs at precisely time *t*, then the outcome (*P* or *Q*) is nondeterministic. Otherwise, the program behaves as *P*.

' $P \swarrow_t Q'$  is the timed interrupt program. It behaves as P until time t, after which it behaves as Q.