# SI-GE PHOTODETECTION TECHNOLOGIES FOR INTEGRATED OPTOELECTRONICS

### A DISSERTATION

# SUBMITTED TO THE DEPARTMENT OF ELECTRICAL ENGINEERING AND THE COMMITTEE ON GRADUATE STUDIES

OF STANFORD UNIVERSITY

IN PARTIAL FULFILMENT OF THE REQUIREMENTS FOR THE DEGREE OF DOCTOR OF PHILOSOPHY

Ali Kemal Okyay

September 2007

© Copyright Ali Kemal Okyay 2007 All Rights Reserved

| I certify that I have read this dissertation and that in my opinion it is fully adequate, in scope and quality, as dissertation for the degree of Doctor of Philosophy. |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (Prof. Krishna C. Saraswat) Principal Advisor                                                                                                                           |

| I certify that I have read this dissertation and that in my opinion it is fully adequate, in scope and quality, as dissertation for the degree of Doctor of Philosophy. |

| (Prof. David A. B. Miller)                                                                                                                                              |

| I certify that I have read this dissertation and that in my opinion it is fully adequate, in scope and quality, as dissertation for the degree of Doctor of Philosophy. |

| (Prof. Mark Brongersma)                                                                                                                                                 |

| Approved for the University Committee on Graduate Studies                                                                                                               |

In the name of Allah, the most compassionate, the most merciful...

All truths are easy to understand once they are discovered;

the point is to discover them.

Galileo Galilei

#### **ABSTRACT**

The communications bottleneck is identified as one of the grand challenges in the progress of silicon computation. While individual logic elements have become significantly faster, computational speed is limited by the communication between different parts of a processor. Traditional copper wires are efficient at short distances, but they suffer excessive power dissipation and delay in global lines, and cannot cope with the ever growing bandwidth demand. Moreover, with the chip architectures evolving towards a modular design, the requirements for increased bandwidth density further strain the electrical interconnects. Optical interconnects (OIs) can provide a solution to the communication bottleneck by alleviating significant power dissipation and delay problems faced by copper wires. Monolithically integrated photodetectors with very low capacitance are sought after for the receiver end of high performance OIs.

In the first part of this dissertation, Ge based metal-semiconductor-metal (MSM) optical detectors integrated on Silicon are discussed. The Ge layer is grown by a novel multi-step Ge-on-Si direct epitaxial growth technique. An important byproduct of this growth technique is tensile strain within the Ge film, resulting in enhanced absorption around 1550 nm. Experimental results of electrical and optical characterization of Ge detectors are presented. A very high responsivity of 0.84 A/W at 1550 nm is reported. The results of physical investigation of the origin of strain in the Ge layers are presented, and a significant red shift in the absorption edge of Ge is reported in the grown films.

A novel CMOS compatible optoelectronic switch is introduced in the second part of this dissertation. The proposed device is a Si MOSFET with Ge gate. The basic operation of the proposed device was investigated by simulations. An experimental proof-of-principle operation was demonstrated. The gate photocurrent is amplified by the MOSFET gain at the drain terminal. 1000 × amplification was reported. The speed of the device and the potential of complementary function in are discussed by simulations.

#### **ACKNOWLEDGEMENTS**

I not only use all of the brains I have, but all I can borrow.

Woodrow Wilson

It is close to the end of my six-year-long adventure here at Stanford... My father always said "starting something is almost like finishing it". That view can only be truly understood at the end.

Stanford gave me all the great opportunities that a Ph.D. student should have. The perfect blend of research and education, combined with a beautiful climate and wonderful neighborhood put Stanford way ahead of other top universities within the US.

This work would not have been possible without the help and contribution of many individuals. I am grateful to many people who made my stay at Stanford a wonderful experience. My deepest gratitude goes to my advisor, Prof. Krishna C. Saraswat. He was involved in every aspect of my research and was always available for a discussion. I especially appreciate his patience and the time he gave me to explore a large number of areas in novel device physics and technology. He was an inspiration for me on many issues including how to run a research group. He has been undoubtedly one of the most kind and helpful people I have ever interacted at Stanford. I have been extremely fortunate to work with the finest advisor that one could possibly hope for. I am grateful for his guidance and endless support.

I am also grateful to my associate advisor Prof. David A. B. Miller for being an inspirational professor at Stanford and also for serving as a reader in my thesis committee. He was always available for discussion and I thank him for all his valuable time and guidance. I have enjoyed a long interaction with his research group through a number of collaborations. I am also grateful for the wide opportunity he gave me to be able to use his labs extensively.

Next, I would like to thank Prof. Mark Brongersma for being an inspirational teacher and also serving as a reader in my thesis committee. I am grateful to him for being such a kind and exceptional professor at Stanford.

I want to also acknowledge my gratitude to Prof. James Harris for being the chair of my oral defense committee. I took all the classes he taught at Stanford between 2001 and 2005. I learned most of my fundamental semiconductor physics knowledge from his classes. He also gave me the opportunity to be a teaching assistant in one of his classes. He is a unique person and has a truly amazing personality and I am very fortunate to have known him.

I want to also acknowledge professors Olav Solgaard, Shanhui Fan and Gregory Kovacks. I am grateful for their help and guidance through the course of my research.

I want to thank Dr. Muhannad Bakir and Prof. James Meindl at GATECH for the collaboration on polymer waveguide and integration work.

All the semiconductor fabrication work would not be possible without the support of many individuals including Dr. Ann Marshall, Maurice, Gladys, Mahnaz, Mike, Mario, Uli, Elmer, Nancy, Ted, Ed, and Bob at the SNF and GLAM. I also want to thank Tom in Ginzton labs. I want to specially thank Dr. Eric Perozzielo for his sincere help and his seemingly infinite knowledge about semiconductor processing.

I would like to thank "the antenna Quattro" Salman, Ekin, Luke and Dany for a great team work and a delightful collaboration.

I want to also extend my thanks to Onur Fidaner with whom I spent long hours in the fab for the last two years working on the SiGe electro-absorption modulator.

I would like to also deeply thank to our administrative associate Irene Sweeney. Her perfection in handling the administrative issues gave me a greater opportunity to focus on my research. I also would like to thank my lab mates Amol Joshi, Pranav Kalavade, Marci Liao, Ting-Yen Chiang, Chi On Chui, Rohit Shenoy, Tejas Krishnamohan, Ammar Nayfeh, Jungyup Kim, Hoyeol Cho, Abhijit Pethe, Hoon Cho, Crystal Kenney, Donghyun Kim, Duygu Kuzum, Gunhan Ertosun, Hoon Cho, Hyun-Yong Yu, Jin Hong Park, Kyung Hoae Koo, Sarves Verma, Shyam Raghunathan, Raja Jain together with Aydogan Ozcan, Hilmi Volkan Demir, Hatice Altug, Fatih Yanik,

Fatih Sarioglu, Utkan Demirci, Omer Oralkan, Ragip Pala, Ryohei Urata, Noah Helman, Jon Roth, Kailash Gopalakrishnan, Il Wung Jung, Yaocheng Liu, Raymond Woo.

No words would ever do justice to express my deepest thanks and gratitude to my most wonderful family – my parents and my sister, Reyyan. I will be eternally grateful to them for being there for me at all times. Their continuous love, sacrifice, support and encouragement have allowed me to pursue my ambitions...

... In what is following, you will read about a part of my technical experience here at Stanford. Of course it is difficult to fit everything in one thesis; and most probably there are a lot of details I have left out. Nevertheless, I hope the following pages will provide you with a coherent story of our optoelectronic technologies.

# **DEDICATION**

To my sister Reyyan and my loving parents

# **TABLE OF CONTENTS**

| List of tables                                            | XV  |

|-----------------------------------------------------------|-----|

| List of figures                                           | xvi |

| CHAPTER 1: INTRODUCTION                                   | 1   |

| 1.1 Motivation                                            | 1   |

| 1.2 Organization of the dissertation                      | 4   |

| References                                                | 6   |

| CHAPTER 2: OPTICAL INTERCONNECTIONS: POTENTIALS           |     |

| AND CHALLENGES                                            | 11  |

| 2.1 Introduction                                          | 11  |

| 2.2 Inter-chip interconnects                              | 11  |

| 2.3 Intra-chip interconnects                              | 13  |

| 2.4 Anatomy of optical interconnect                       | 14  |

| 2.5 Monolithic integration                                | 15  |

| References                                                | 19  |

| <b>CHAPTER 3: EFFECTIVE DARK CURRENT SUPPRESSION WITI</b> | H   |

| ASYMMETRIC METAL-SEMICONDUCTOR-METAL OPTICAL              |     |

| DETECTORS IN GROUP IV SEMICONDUCTORS                      | 24  |

| 3.1 Introduction                                          | 24  |

| 3.2 Analytic current transport model in MSM structures    | 25  |

| 3.3 Electron and hole currents                            | 26  |

| 3.4 Asymmetric workfunction metal electrodes              | 30  |

| 3.4.1 Theory and simulations                              | 30  |

| 3.4.2 Fabrication                                         | 33  |

| 3.4.3 Experimental results and discussion                 | 34  |

| 3.5 Asymmetric contact area metal electrodes              | 39  |

| 3.5.1 Theory and simulations                              | 39  |

| 3.5.2 Fabrication                                         | 40  |

| 3.5.3 Experimental results and discussion                 | 41  |

|          | 3.6 Conclusions                                                       | 43    |

|----------|-----------------------------------------------------------------------|-------|

|          | References                                                            | 45    |

| <b>C</b> | HAPTER 4: HIGH PERFORMANCE GERMANIUM OPTICAL                          |       |

| D.       | ETECTORS INTEGRATED ON SILICON                                        | 48    |

|          | 4.1 Introduction                                                      | 48    |

|          | 4.1.1 Review of epitaxial growth mechanism                            | 49    |

|          | 4.1.2 Origin of threading dislocations                                | 52    |

|          | 4.1.3 Quantifying dislocation density                                 | 53    |

|          | 4.1.4 Literature review of techniques reducing threading dislocations | 53    |

|          | 4.2 Experimental procedure                                            | 56    |

|          | 4.2.1 Heteroepitaxy of Ge on Si                                       | 56    |

|          | 4.2.2 Photodetector fabrication                                       | 61    |

|          | 4.3 Results and discussion                                            | 63    |

|          | 4.3.1 Surface roughness and dislocation density                       | 63    |

|          | 4.3.2 Electrical characterization                                     | 67    |

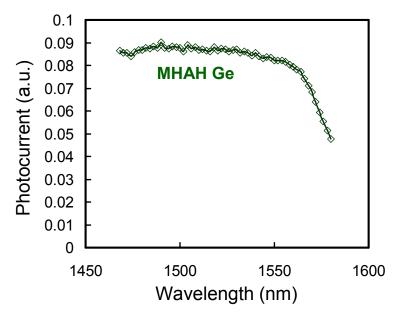

|          | 4.3.3 Optical characterization                                        | 70    |

|          | 4.4 Strain and stress in MHAH-grown Ge layers                         | 73    |

|          | 4.4.1 Residual tensile strain in Ge layers                            | 74    |

|          | 4.4.2 Origin of the residual tensile strain                           | 77    |

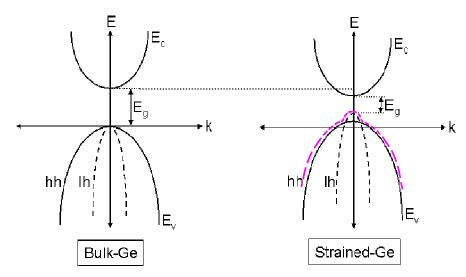

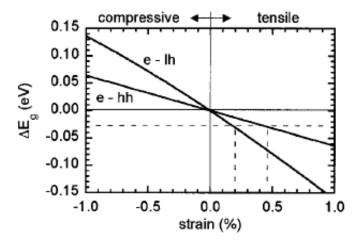

|          | 4.4.3 Effects of strain on Ge band structure                          | 78    |

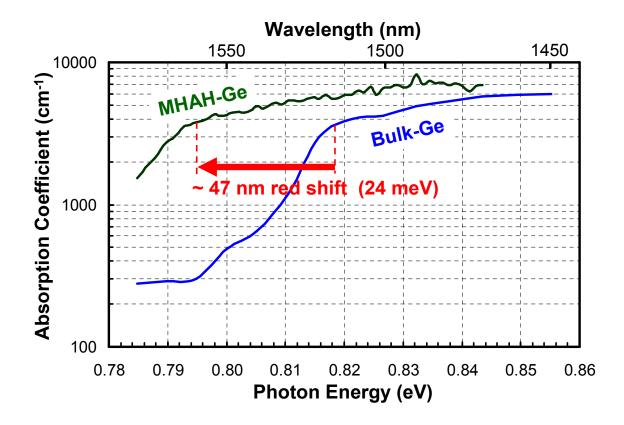

|          | 4.4.4 Red shift of Ge absorption edge                                 | 81    |

|          | 4.5 Conclusions                                                       | 83    |

|          | References                                                            | 84    |

| C.       | HAPTER 5: INTEGRATION OF OPTICAL POLYMER PILLAR                       |       |

| W        | AVEGUIDES WITH MSM PHOTODETECTORS                                     | 94    |

|          | 5.1 Introduction                                                      | 94    |

|          | 5.2 Experimental procedure                                            | 97    |

|          | 5.3 Geometrical design and images of completed devices                | 99    |

|          | 5.4 Results and discussion                                            | . 103 |

|          | 5.5 Conclusion                                                        | . 109 |

|          | Pafarancas                                                            | 110   |

| <b>CHAPTER 6:</b> A NOVEL CMOS COMPATIBLE SEMICONDUCTO            | R   |

|-------------------------------------------------------------------|-----|

| OPTOELECTRONIC SWITCHING DEVICE: BRINGING LIGHT                   |     |

| TO LATCH                                                          | 113 |

| 6.1 Introduction                                                  | 113 |

| 6.1.1 Literature review of phototransistors                       | 117 |

| 6.2 Device description and operation                              | 121 |

| 6.2.1 Device structure                                            | 121 |

| 6.2.2 Principle of operation                                      | 122 |

| 6.2.3 The MOS capacitor                                           | 126 |

| 6.2.4 Small signal FET gain                                       | 128 |

| 6.3 Device fabrication                                            | 130 |

| 6.3.1 Ge-SiO <sub>2</sub> -Si capacitor fabrication               | 130 |

| 6.3.2 Optoelectronic transistor fabrication                       | 132 |

| 6.4 Device characterization                                       | 136 |

| 6.4.1 Experimental setup and characterization                     | 137 |

| 6.4.2 Temporal response                                           | 138 |

| 6.5 Complementary operation                                       | 142 |

| 6.5.1 More light, less conduction                                 | 142 |

| 6.5.2 Optically controlled electrical inverter: Paving the way to |     |

| bring light to latch                                              | 144 |

| 6.6 Optoelectronic MOSFET and the traditional receiver            | 147 |

| 6.7 Performance improvement and scalability                       | 149 |

| 6.7.1 Tunnel-FET                                                  | 149 |

| 6.7.2 Photo-MOSFET                                                | 151 |

| 6.7.3 Nano-metallic light concentrators                           | 153 |

| 6.8 Conclusions                                                   | 154 |

| References                                                        | 156 |

| CHAPTER 7: CONCLUSIONS                                            | 166 |

| Recommendations for future work                                   | 168 |

| APPENDIX A                                                        | 170 |

| APPENDIX R                                                        | 177 |

# LIST OF TABLES

| Number     |                                         | Page |

|------------|-----------------------------------------|------|

| 6.1        | Optical MOSFET process flow and details | 133  |

| 6.2        | The ITRS technology design parameters   | 148  |

|            |                                         |      |

|            |                                         |      |

| <b>B.1</b> | Typical MHAH recipe                     | 177  |

# LIST OF FIGURES

| nber Page                                                                                     |

|-----------------------------------------------------------------------------------------------|

| The chain of communication systems versus the length of the                                   |

| interconnection and the business volume of the corresponding                                  |

| technology                                                                                    |

| A typical server cabinet with (a) electrical cables (b) optical links                         |

| interconnecting between different sections                                                    |

| Illustration of types of optical and electrical propagation and their                         |

| velocities. (After [34])                                                                      |

|                                                                                               |

|                                                                                               |

| (a) Total chip power vs. the year of introduction. (b) Chip power                             |

| density vs. the year of introduction                                                          |

| Power dissipation of chip-to-chip interconnections vs. distance                               |

| Delay of on-chip electrical and optical links vs. interconnect length 14                      |

| Block diagram of a typical optical interconnect                                               |

| Absorption coefficient for various semiconductors vs. photon                                  |

| energy                                                                                        |

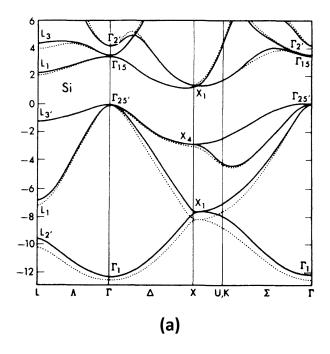

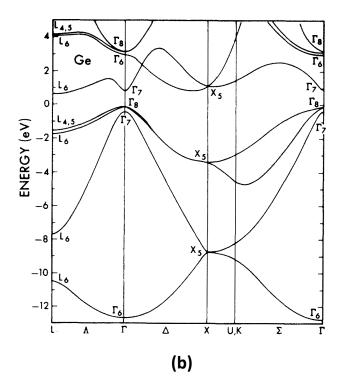

| Band structures of (a) Si and (b) Ge (After [41])                                             |

|                                                                                               |

|                                                                                               |

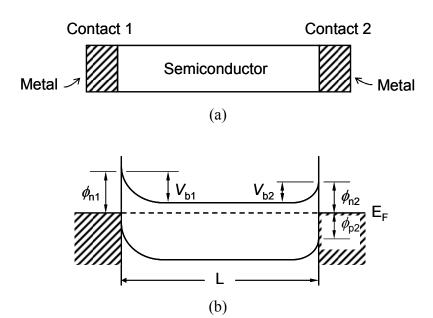

| (a) Schematic diagram of a metal-semiconductor-metal structure.                               |

| (b) The corresponding energy band diagram at thermal equilibrium                              |

| where $\phi_{n1}$ and $\phi_{n2}$ are the electron barrier heights, and $V_{b1}$ and $V_{b2}$ |

| are the built-in potentials for contacts 1 and 2, respectively                                |

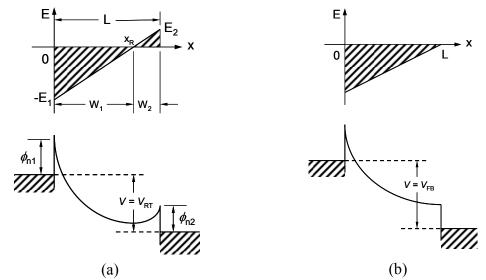

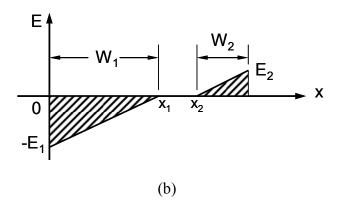

| (a) Field distribution and energy diagram of an MSM structure at                              |

| reach-through (b) Condition of flat-band at which the energy band                             |

| at $x = L$ becomes flat                                                                       |

| $a_{1,\lambda} = \iota_{\lambda}$ decourses that                                              |

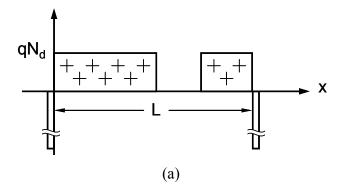

| (a) The charge distribution, (b) electric field, (c) and potential                            |

|                                                                                               |

|      | applied on contact 2. The contact 1 is reverse biased and contact 2                     |      |

|------|-----------------------------------------------------------------------------------------|------|

|      | is forward biased                                                                       | 29   |

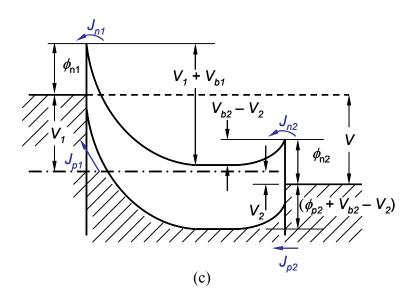

| 3.4  | Simplified energy band diagram illustration of sources of dark                          |      |

|      | current in an MSM PD under external voltage bias                                        | . 31 |

| 3.5  | Simulated PD currents versus bias voltage at both zero and 50                           |      |

|      | $nW/\mu m^2$ illuminations. An MSM structure per unit width with $2$                    |      |

|      | $\mu m$ inter-electrode spacing and 2 $\mu m$ thick Si substrate was used.              |      |

|      | $\Phi_{m2}$ was arbitrarily fixed at 4.2 eV with various $\Phi_{m1}$ . Light was at     |      |

|      | normal incident from the top with a wavelength of 623 nm                                | 31   |

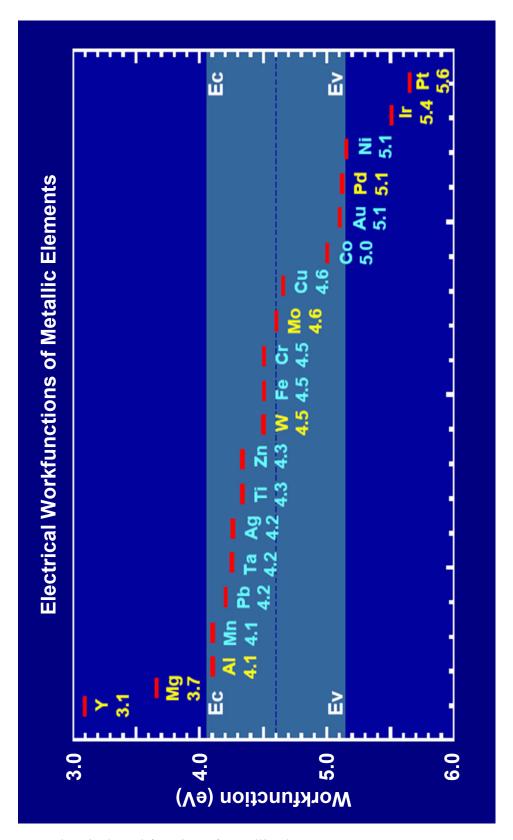

| 3.6  | Electrical workfunction of metallic elements                                            | 32   |

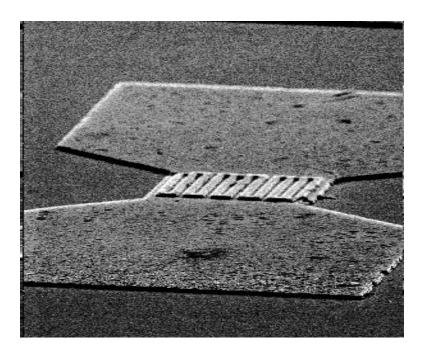

| 3.7  | SEM image of a completed MSM photodetector. Interdigitated                              |      |

|      | fingers are shown. Metal pads fan out from the active area for                          |      |

|      | probing                                                                                 | 33   |

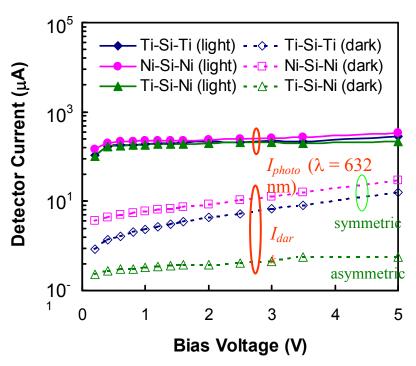

| 3.8  | Experimental photoresponse and dark currents measured from both                         |      |

|      | symmetric (Ti or Ni electrodes only) and asymmetric (Ti and Ni                          |      |

|      | electrodes together) MSM-PDs on Si substrate. The MSM-PDs                               |      |

|      | investigated had 5 $\mu m$ $\times$ 5 $\mu m$ fingers (width $\times$ spacing) and area |      |

|      | of $10^4  \mu\text{m}^2$                                                                | 34   |

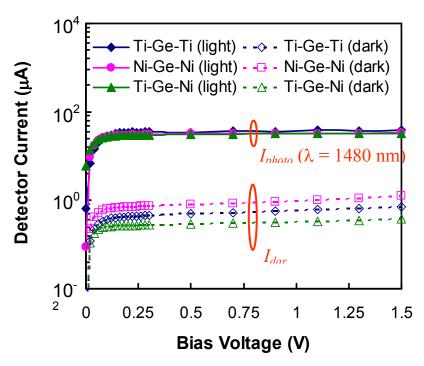

| 3.9  | Experimental photoresponse and dark currents measured from both                         |      |

|      | symmetric (Ti or Ni electrodes only) and asymmetric (Ti and Ni                          |      |

|      | electrodes together) MSM-PDs on Ge substrate. The MSM-PDs                               |      |

|      | investigated had 5 $\mu m$ $\times$ 5 $\mu m$ fingers (width $\times$ spacing) and area |      |

|      | of $10^4  \mu\text{m}^2$                                                                | 35   |

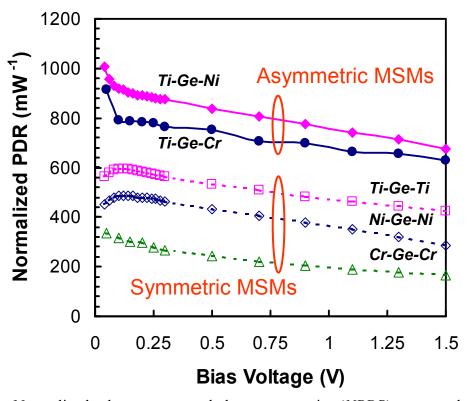

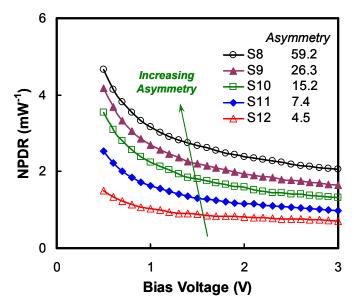

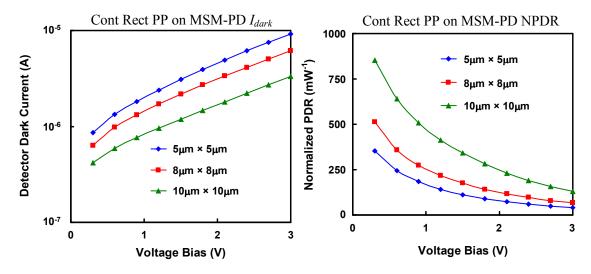

| 3.10 | Normalized photocurrent-to-dark current ratio (NPDR) extracted                          |      |

|      | from various Ge symmetric and asymmetric MSMs with 5 $\mu m \times 5$                   |      |

|      | $\mu m$ fingers and area of $10^4~\mu m^2$ under 1480 nm illumination                   | 36   |

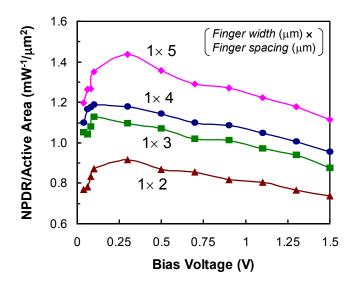

| 3.11 | The effect of varying MSM finger spacing on the extracted NPDR                          |      |

|      | normalized to the active unblocked absorption area. Ti-Ge-Ni PDs                        |      |

|      | were used as an example with fixed finger width of 1 $\mu m$ at $\lambda =$             |      |

|      | 1320 nm illumination                                                                    | 37   |

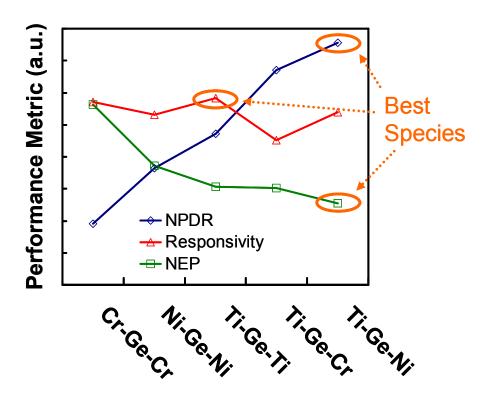

| 3.12 | Comparison of $NPDR$ , $NEP$ and $\Re$ of symmetric and asymmetric                             |      |

|------|------------------------------------------------------------------------------------------------|------|

|      | MSMs                                                                                           | . 38 |

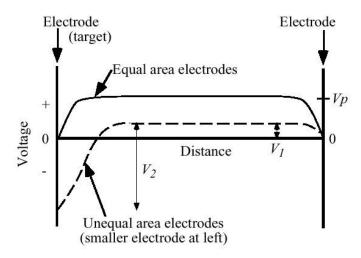

| 3.13 | The potential profile in an unequal electrode area RF sputtering                               |      |

|      | system                                                                                         | . 39 |

| 3.14 | Simulated dark current reduction in MSMs with increasing contact                               |      |

|      | area asymmetry. The total contact area of each detector is fixed in                            |      |

|      | the simulations. Simulations were done on MSMs with 1 $\mu m$ inter-                           |      |

|      | electrode spacing on 5 µm thick Si substrate                                                   | . 40 |

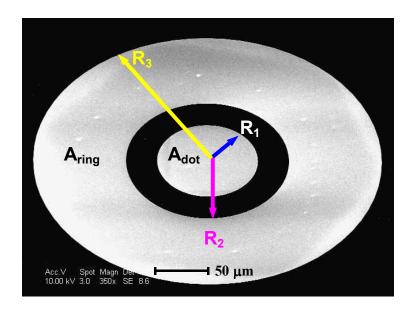

| 3.15 | SEM image of a completed circular MSM photodetector with                                       |      |

|      | asymmetric contact area. Critical dimensions are defined with the                              |      |

|      | arrows                                                                                         | . 41 |

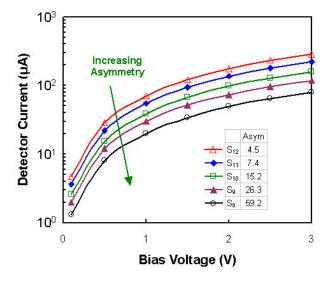

| 3.16 | Experimental <i>I-V</i> under dark conditions. Dark current decreases                          |      |

|      | from $S_{12}$ to $S_8$ in the same direction as increasing area asymmetry                      | . 42 |

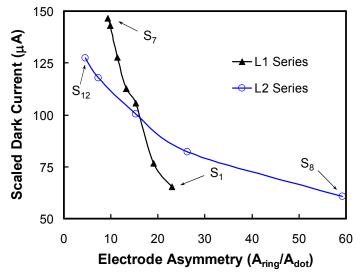

| 3.17 | $I_{dark}$ (scaled by $A_{total}$ ) versus area asymmetry. From $S_{12}$ to $S_8$ , $I_{dark}$ |      |

|      | decreases in the same direction as increasing asymmetry. $L_I$ series                          |      |

|      | show a steeper reduction in $I_{dark}$ due to increasing asymmetry and                         |      |

|      | electrode spacing                                                                              | . 42 |

| 3.18 | NPDR extracted under 632 nm illumination. NPDR is higher for                                   |      |

|      | larger asymmetry photodetectors due to reduced $I_{dark}$ with                                 |      |

|      | increasing electrode asymmetry and no significant degradation in                               |      |

|      | photoresponse                                                                                  | . 43 |

|      |                                                                                                |      |

|      |                                                                                                |      |

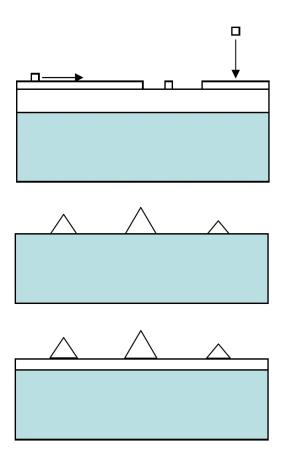

| 4.1  | Schematic illustration of the three equilibrium growth modes: (a)                              |      |

|      | Frank-van de Merwe (layer-by-layer), (b) Volmer-Weber                                          |      |

|      | (Cluster), and (c) Stranski-Krastanov (layer-cluster)                                          | . 50 |

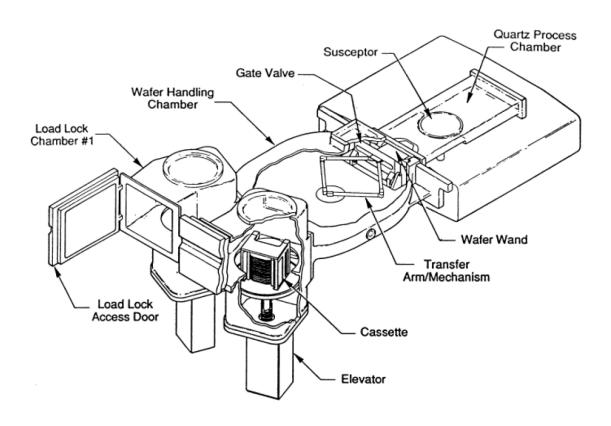

| 4.2  | ASM basic wafer-handling section drawing, courtesy of ASM                                      |      |

|      | Epitaxy                                                                                        | . 57 |

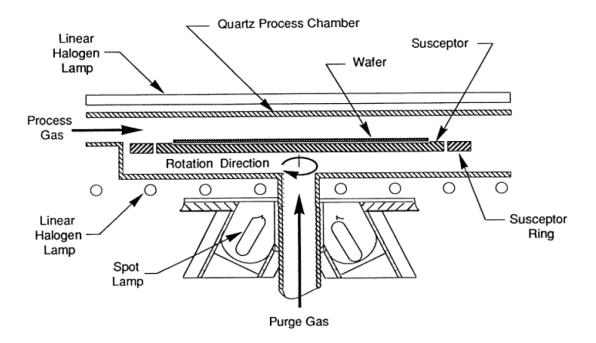

| 4.3  | Reactor quartz susceptor and lamp arrays drawing, courtesy of                                  |      |

|      | ASM                                                                                            | . 58 |

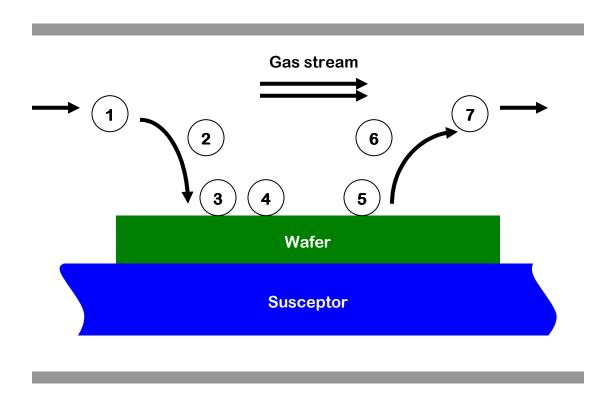

| 4.4  | The seven parts of a CVD process                                                               | . 59 |

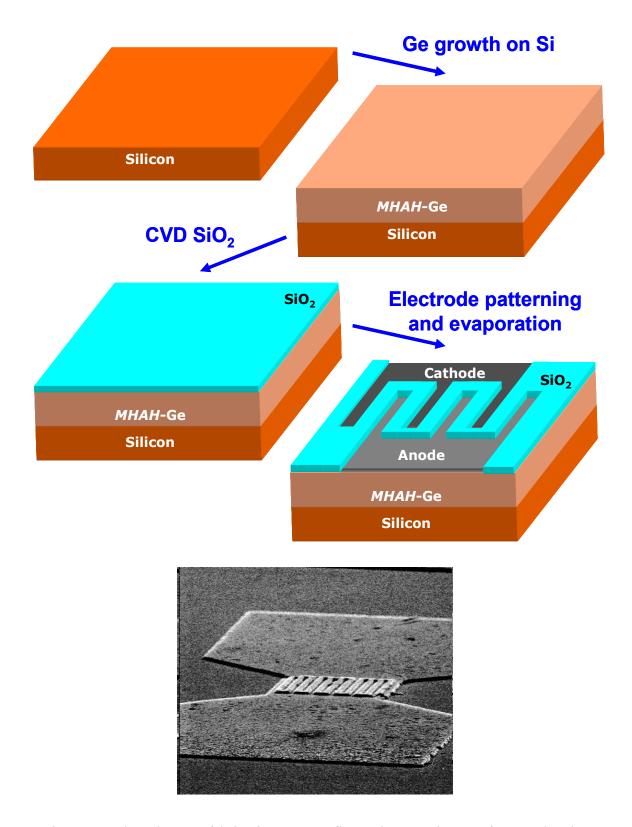

| 4.5  | Photodetector fabrication process flow. The SEM image of a                |      |

|------|---------------------------------------------------------------------------|------|

|      | completed MSM is shown at the bottom                                      | . 62 |

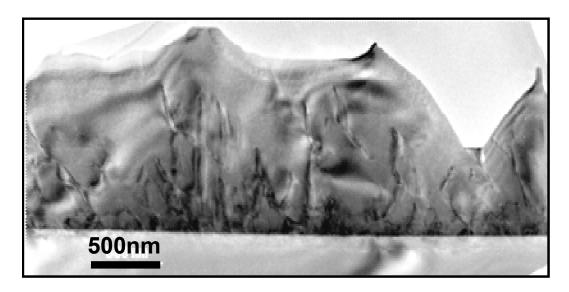

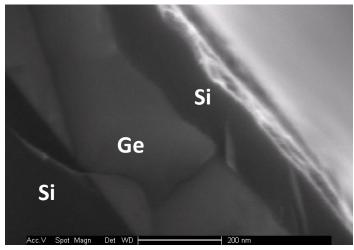

| 4.6  | Cross sectional TEM image of 1-µm-thick as-grown Ge layer on Si           |      |

|      | at 400°C. Misfit dislocations at the Ge/Si interface thread to the        |      |

|      | surface                                                                   | . 64 |

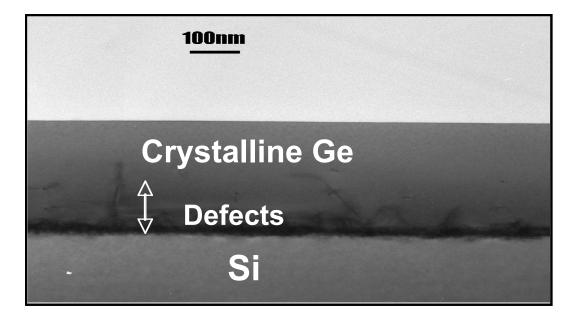

| 4.7  | Cross sectional TEM image of 400-nm-thick Ge layer grown on Si            |      |

|      | at 400°C followed by 1 hr anneal in H <sub>2</sub> ambient at 825°C. Both |      |

|      | defect density and surface roughness are reduced. Most of the             |      |

|      | defects are concentrated at the Ge/Si interface, while the surface is     |      |

|      | low in defect density                                                     | . 64 |

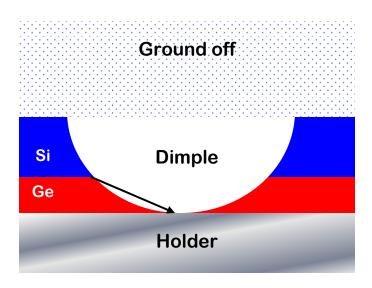

| 4.8  | Schematic of the plan-view sample after preparation for                   |      |

|      | measurement                                                               | . 65 |

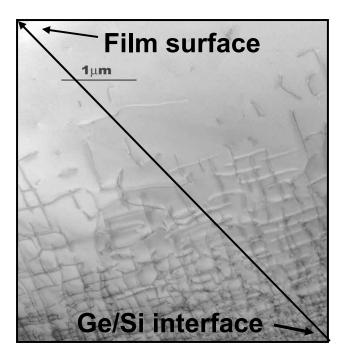

| 4.9  | Plan-view TEM image of 400-nm-thick Ge layer grown on Si by               |      |

|      | MHAH technique. The sample becomes thinner in the direction of            |      |

|      | the arrow, indicated in the previous figure as well. The upper layer      |      |

|      | of the film shows drastic reduction in defect density                     | . 66 |

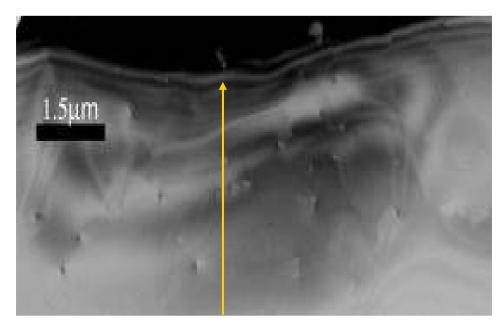

| 4.10 | Plan-view TEM image of a 4.5-µm-thick MHAH-grown Ge layer                 |      |

|      | on Si. 200-nm-depth from the surface is shown. Dislocation                |      |

|      | density is reduced to less than $7 \times 10^7$ cm <sup>-2</sup>          | . 66 |

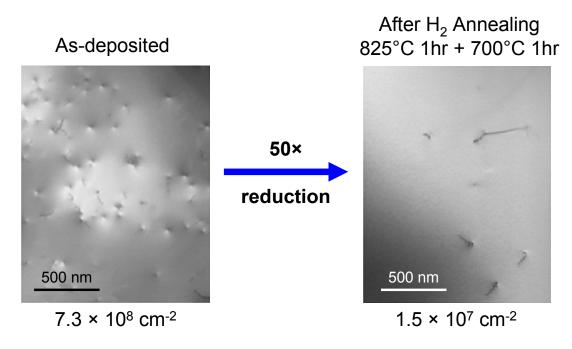

| 4.11 | Plan-view TEM image of as-grown and H2 annealed Ge on Si                  |      |

|      | showing 50× reduction in dislocation density. Film growth is              |      |

|      | carried out in an industry-standard epi-reactor in Canon                  | . 67 |

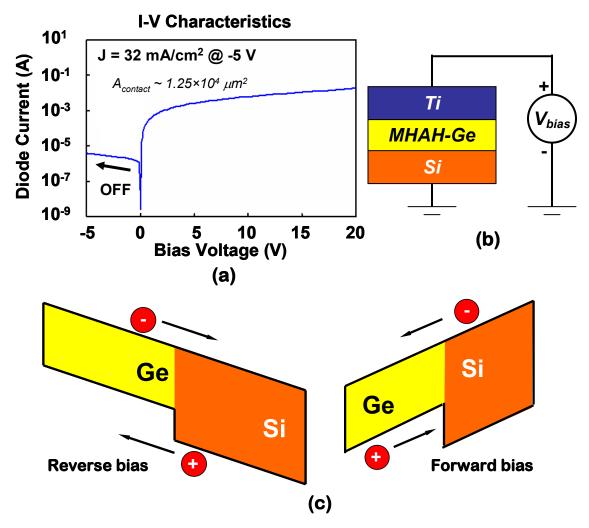

| 4.12 | (a) Measured I-V characteristics of the Ti-Ge Schottky diode.             |      |

|      | Decent rectification obtained with low reverse saturation current         |      |

|      | density. (b) The schematic of the measured MS diode structure and         |      |

|      | applied bias. (c) Energy band diagram of the measured MS diode            | . 68 |

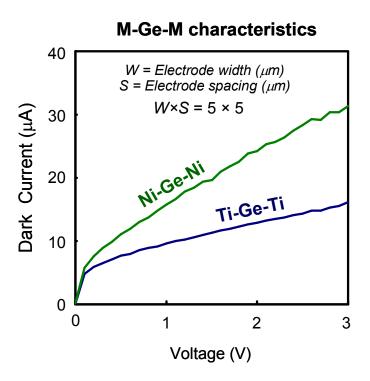

| 4.13 | Experimental I-V characteristics of back-to-back MS diodes.               |      |

|      | Interdigitated MSM with electrode width and spacing 5 $\mu m$ . Ti-       |      |

|      | Ge-Ti and Ni-Ge-Ni symmetric detectors.                                   | . 69 |

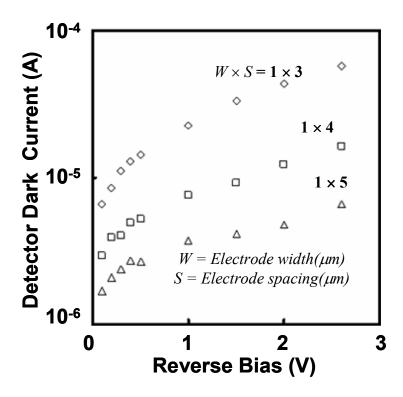

| 4.14 | Experimental I-V characteristics of Ti-Ge-Ti interdigitated MSM           |      |

|      | with electrode width 1 μm and spacing 3,4, and 5 μm                       | . 70 |

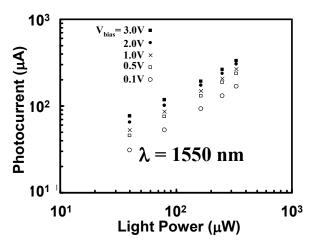

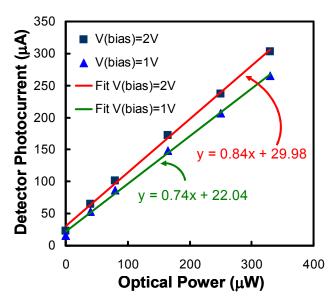

| 4.15 | Photocurrent versus light intensity at different applied reverse bias    |    |

|------|--------------------------------------------------------------------------|----|

|      | for Ti-Ge-Ti MSM with electrode width and spacing 5 $\mu m$              | 71 |

| 4.16 | Detector current vs. input optical power ( $\lambda = 1550$ nm) for MSM  |    |

|      | with electrode width and spacing 5 $\mu m$ . The points are measured     |    |

|      | data and the lines are theoretical fit                                   | 71 |

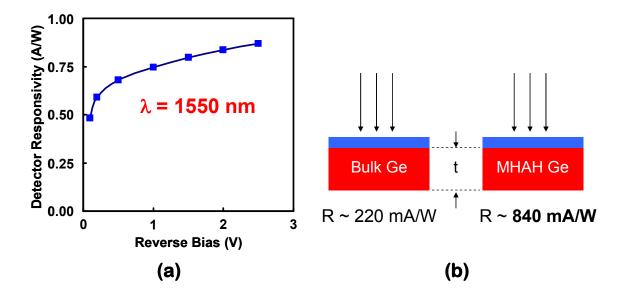

| 4.17 | (a) Measured responsivity of Ti-Ge-Ti MSM with electrode width           |    |

|      | and spacing 5 µm. At every bias point, responsivity is extracted         |    |

|      | from the slope of the linear fit in the previous figure. (b)             |    |

|      | Comparison of theoretical vs. experimental responsivity                  | 72 |

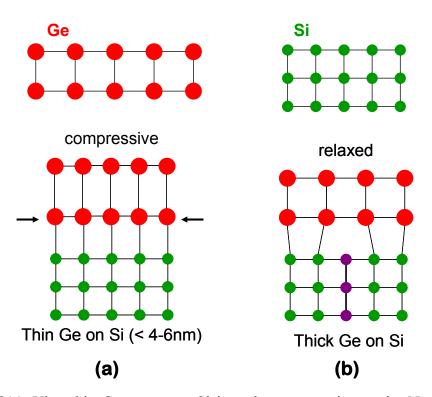

| 4.18 | (a) Ultra-thin Ge grown on Si is under compressive strain. No            |    |

|      | defects are introduced until critical thickness is achieved (~ 5 nm).    |    |

|      | (b) Thick Ge layer grown on Si. The stress is relieved by forming        |    |

|      | dislocations and Ge attains the relaxed lattice constant                 | 74 |

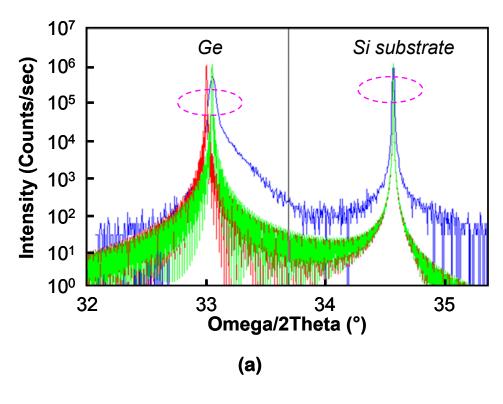

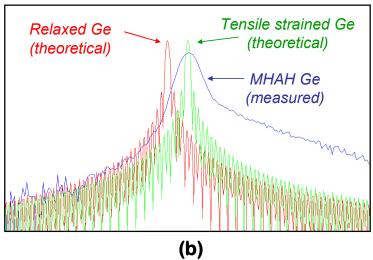

| 4.19 | (a) (004) $\Omega$ –2 $\theta$ XRD scan of MHAH-Ge grown on Si. The peak |    |

|      | on the right is from the Si(001) substrate and the one on the left is    |    |

|      | Ge lattice (b) Magnified view of the Ge peak. The blue curve is the      |    |

|      | measured signal, the red and green curves are calculated curves for      |    |

|      | relaxed and tensile strained Ge, respectively                            | 76 |

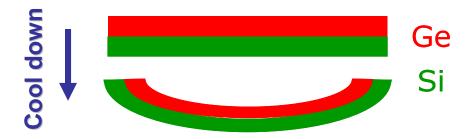

| 4.20 | Schematic illustration of mismatch between coefficients of thermal       |    |

|      | expansion between Si and Ge. Ge tries to contract faster than Si on      |    |

|      | cooling down from the annealing temperature (825-850°C)                  | 78 |

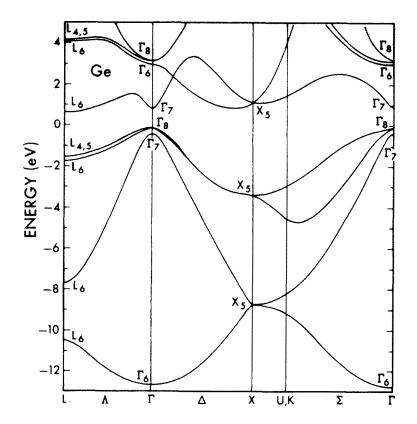

| 4.21 | Band structure of Ge calculated by Chelikowsky and Cohen [81]            | 78 |

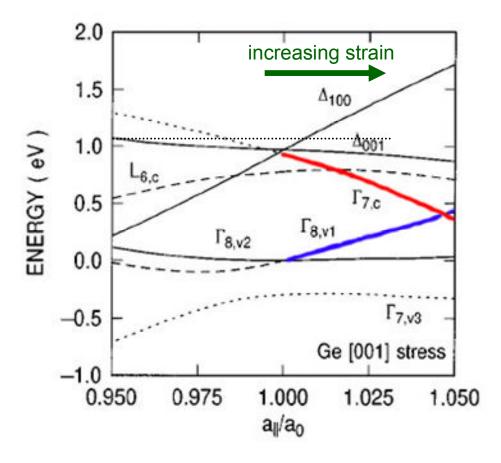

| 4.22 | Deformation of band structure of Ge with biaxial strain calculated       |    |

|      | by Fischetti [82]. The change in the conduction band minima at the       |    |

|      | zone center and the valence band maxima for light holes with             |    |

|      | increasing biaxial tensile strain are highlighted by red and blue,       |    |

|      | respectively                                                             | 79 |

| 4.23 | Illustration of the change in the bands with biaxial tensile strain in   |    |

|      | the Ge film. The minimum of the conduction band at the zone              |    |

|      | canter moves down while the maximum of the valence band for              |    |

|      | neavy and light notes move up. The direct band energy is reduced            |      |

|------|-----------------------------------------------------------------------------|------|

|      | due to tensile strain                                                       | . 80 |

| 4.24 | The change in the direct gap energy of Ge calculated by [79]                | . 80 |

| 4.25 | Measured responsivity vs wavelength of Ti-Ge-Ti MSM with                    |      |

|      | electrode width and spacing 5 µm                                            | . 81 |

| 4.26 | Experimental absorption coefficient vs photon energy for MHAH-              |      |

|      | grown Ge layers. $\alpha_{Ge}$ is extracted from measured responsivity      |      |

|      | correcting for surface reflections and assuming 90% internal                |      |

|      | quantum efficiency. The absorption curve for relaxed Ge is also             |      |

|      | plotted for reference purposes. A 47 nm red shift of the absorption         |      |

|      | edge is recorded due to tensile strain                                      | . 82 |

|      |                                                                             |      |

|      |                                                                             |      |

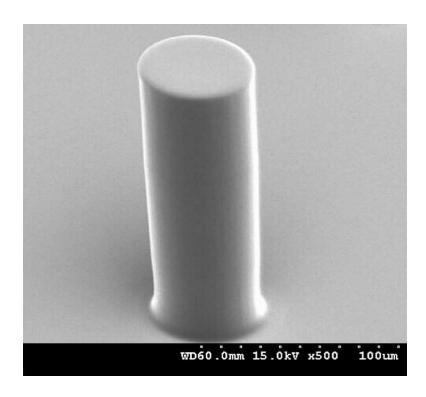

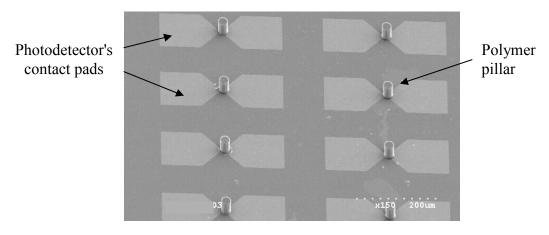

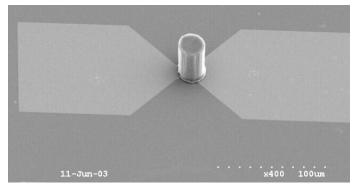

| 5.1  | SEM micrograph of a polymer pillar that is $\sim 180~\mu m$ tall and 55     |      |

|      | μm wide                                                                     | . 96 |

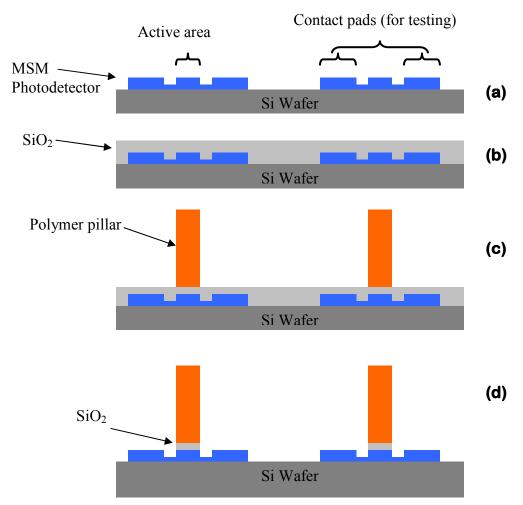

| 5.2  | A schematic of the process used to fabricate polymer pillars on             |      |

|      | MSM-PDs. (a) Wafer with prefabricated MSM-PDs. (b) SiO <sub>2</sub> is      |      |

|      | deposited on the wafer to enhance adhesion between the polymer              |      |

|      | film (subsequent step) and the substrate. (c) Polymer pillars are           |      |

|      | fabricated above the active area of the MSM-PDs. (d) Using the              |      |

|      | polymer pillars as an etch mask, the SiO <sub>2</sub> film was etched using |      |

|      | BOE. This process step exposed the contact pads of the detectors            |      |

|      | to facilitate electrical testing                                            | . 97 |

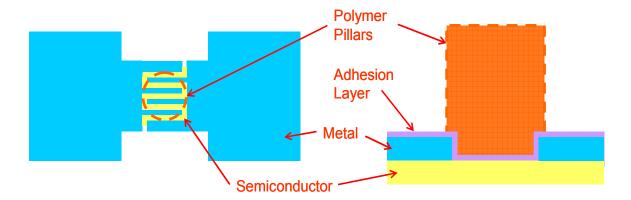

| 5.3  | Schematic illustration of the proposed integration scheme. The              |      |

|      | MSM photodetector is fabricated followed by the deposition of the           |      |

|      | polymer. Pillars of different size and geometry are defined using           |      |

|      | lithography                                                                 | . 98 |

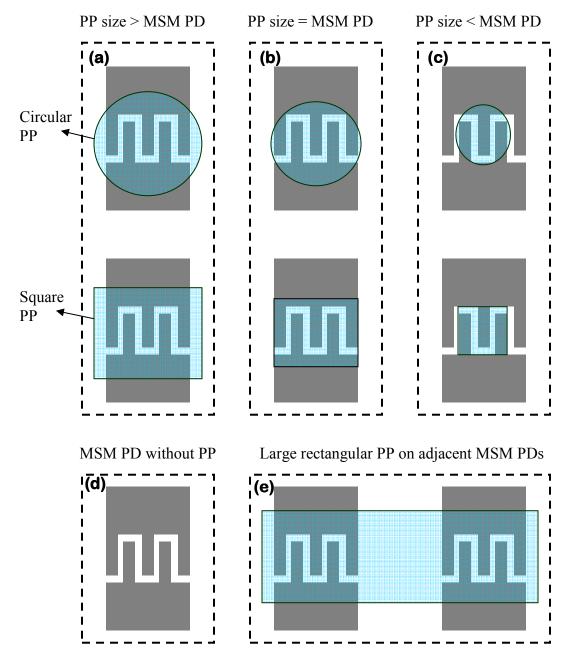

| 5.4  | Schematic illustrating how various size and shape polymer pillars           |      |

|      | (PP) were fabricated on identical MSM-PDs. Through                          |      |

|      | measurements, such a layout design will ultimately provide insight          |      |

|      | into how the polymer pillars affect the characteristics of the MSM-                 |     |

|------|-------------------------------------------------------------------------------------|-----|

|      | PDs                                                                                 | 99  |

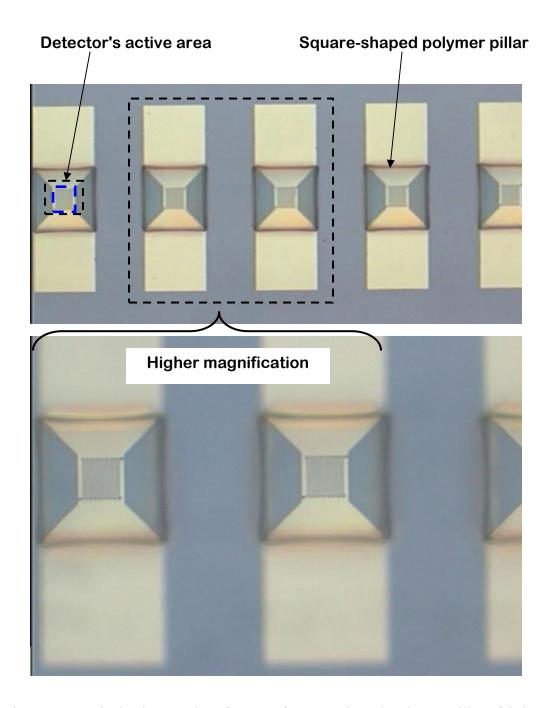

| 5.5  | SEM micrograph of a set of polymer pillars fabricated on Ti-Si-Ti                   |     |

|      | MSM-PDs. The large pads on either side of the active area are                       |     |

|      | used to facilitate electrical measurements                                          | 100 |

| 5.6  | A higher magnification SEM micrograph of previous figure                            |     |

|      | illustrating a polymer pillar on an MSM-PD                                          | 100 |

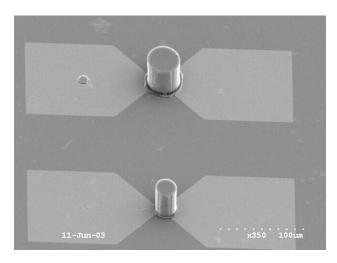

| 5.7  | SEM micrograph illustrating two polymer pillars with different                      |     |

|      | aspect ratios fabricated on two similar MSM-PDs                                     | 101 |

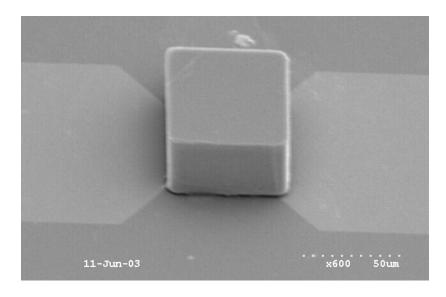

| 5.8  | SEM micrograph of a very low aspect ratio square-shaped polymer                     |     |

|      | pillar on a large MSM-PD.                                                           | 101 |

| 5.9  | Optical micrographs of a set of square-shaped polymer pillars                       |     |

|      | fabricated above the active area of MSM-PDs. The size of the                        |     |

|      | pillars is much larger than the size of the PDs                                     | 102 |

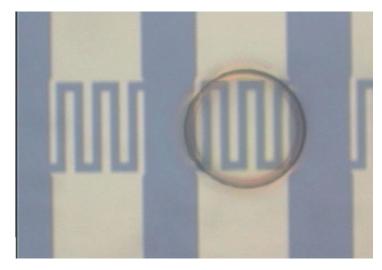

| 5.10 | Optical micrograph of a MSM-PD with and without a polymer                           |     |

|      | pillar. The cross-sectional area of the pillar is equal to the size of              |     |

|      | the active area                                                                     | 103 |

| 5.11 | Optical micrograph illustrating small diameter and high aspect                      |     |

|      | ratio circular polymer pillars fabricated above relatively small                    |     |

|      | MSM-PDs                                                                             | 103 |

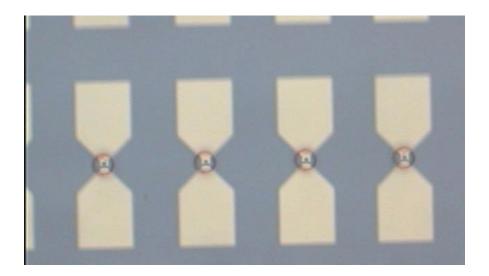

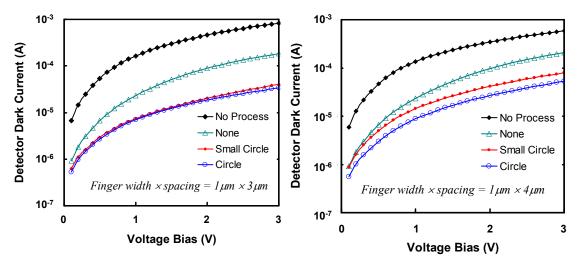

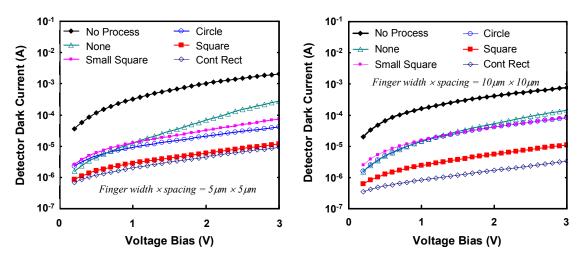

| 5.12 | Measured dark current as a function of bias for a set of Ti-Si-Ti                   |     |

|      | MSM-PDs with and without polymer pillars. The plots are for                         |     |

|      | detectors with a 1 $\mu m$ x 3 $\mu m$ and 1 $\mu m$ x 4 $\mu m$ finger width and   |     |

|      | spacing. The active area of the detectors is $1156 \ \mu m^2$                       | 104 |

| 5.13 | Measured dark current as a function of bias for a set of Ti-Si-Ti                   |     |

|      | MSM-PDs with and without polymer pillars. The plots are for                         |     |

|      | detectors with a 5 $\mu m$ x 5 $\mu m$ and 10 $\mu m$ x 10 $\mu m$ finger width and |     |

|      | spacing. The active area of the detectors is $10{,}000~\mu\text{m}^2$               | 105 |

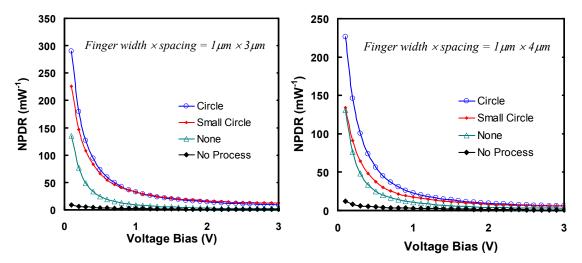

| 5.14 | Normalized photo-to-dark current ratio (NPDR) as a function of                      |     |

|      | bias for a set of Ti-Si-Ti MSM-PDs (Fig. 5.12) with and without                     |     |

|      | polymer pillars. The plots are for detectors with a 1 $\mu$ m x 3 $\mu$ m and       |     |

|      | 1 μm x 4 μm finger width and spacing. The active area of the                  |     |

|------|-------------------------------------------------------------------------------|-----|

|      | detectors is 1156 $\mu m^2$ . The measurements were made with a 790           |     |

|      | nm and 1-1.5 mW laser                                                         | 107 |

| 5.15 | Normalized photo-to-dark current ratio (NPDR) as a function of                |     |

|      | bias for a set of Ti-Si-Ti MSM-PDs (Fig. 5.13) with and without               |     |

|      | polymer pillars. The plots are for detectors with a 5 $\mu$ m x 5 $\mu$ m and |     |

|      | 10 μm x 10 μm finger width and spacing. The active area of the                |     |

|      | detectors is $10,000 \ \mu m^2$ . The measurements were made with a 790       |     |

|      | nm and 1-1.5 mW laser                                                         | 107 |

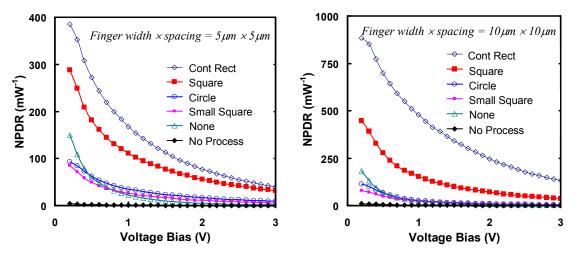

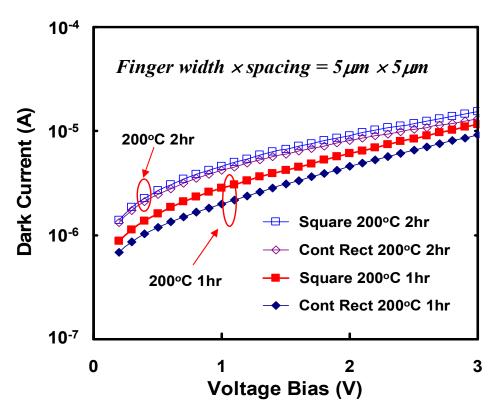

| 5.16 | Dark current as a function of bias voltage for a set of MSM-PD                |     |

|      | that have an active area of $10,000 \mu m^2$ and finger width and             |     |

|      | spacing of 5 μm x 5 μm                                                        | 108 |

| 5.17 | Dark current and NPDR as a function of bias voltage for a MSM-                |     |

|      | PD of the configuration shown in Fig. 5.4(e) that have an active              |     |

|      | area of 10,000 μm <sup>2</sup>                                                | 109 |

|      |                                                                               |     |

|      |                                                                               |     |

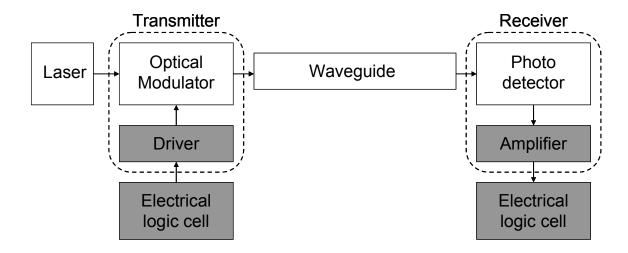

| 6.1  | A block diagram illustration of an optical link in which the light            |     |

|      | from a continuous wave laser is modulated and transmitted. The                |     |

|      | waveguide carries the optical signal to the receiver which is                 |     |

|      | converted to electrical current by the photodetector. The trans-              |     |

|      | impedance amplifier converts current to a voltage signal and the              |     |

|      | subsequent buffer stages amplify the voltage to the logic level               | 114 |

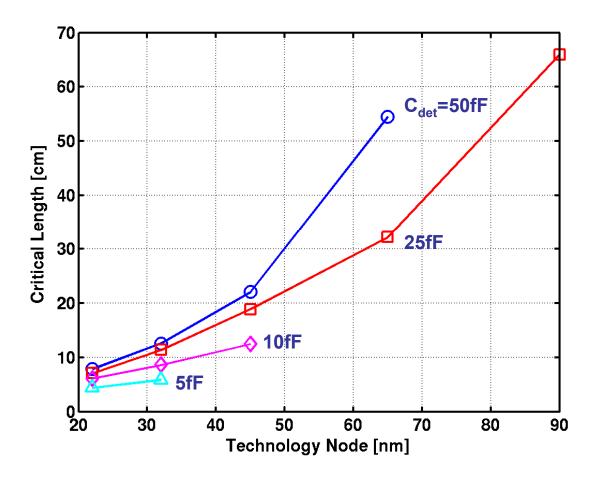

| 6.2  |                                                                               |     |

|      | plotting critical length as a function of technology scaling.                 |     |

|      | Technology scaling incorporates both transistor performance                   |     |

|      | improvement and higher bit rate demand. After Cho <i>et al.</i> [33]          | 115 |

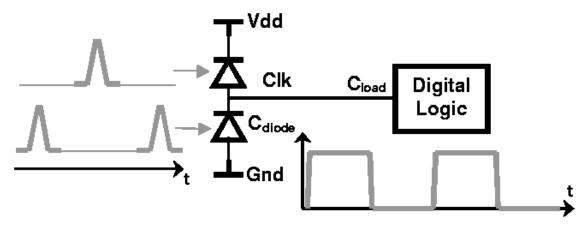

| 6.3  | Schematic view of the receiver-less direct clock injection. Two               | -10 |

| •••  | photodiodes are connected on top of each other in a <i>totem-pole</i>         |     |

|      | scheme. Light pulses delayed in time are incident on the diodes. At           |     |

|      |                                                                               |     |

|     | every cycle, the upper diode charges the load capacitor followed               |     |

|-----|--------------------------------------------------------------------------------|-----|

|     | by discharging by the lower one. After Debaes et al. [34]                      | 116 |

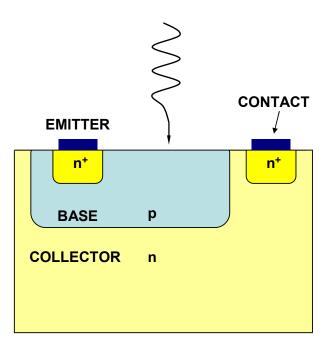

| 6.4 | Schematic illustration of a common phototransistor which is a                  |     |

|     | modified version of a classical bipolar transistor                             | 117 |

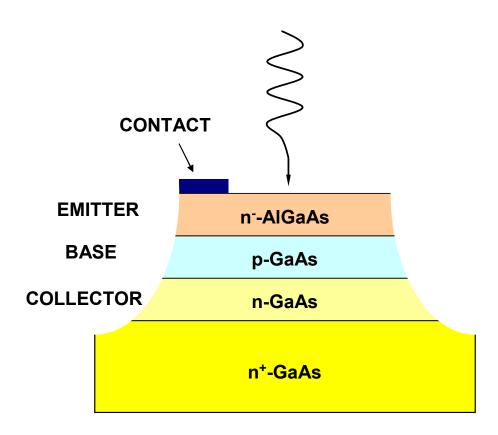

| 6.5 | A typical heterojunction phototransistor with a wide bandgap                   |     |

|     | emitter configuration. The emitter does not absorb the incident                |     |

|     | light due to high bandgap, hence increasing the efficiency in                  |     |

|     | addition to the improved emitter injection efficiency                          | 118 |

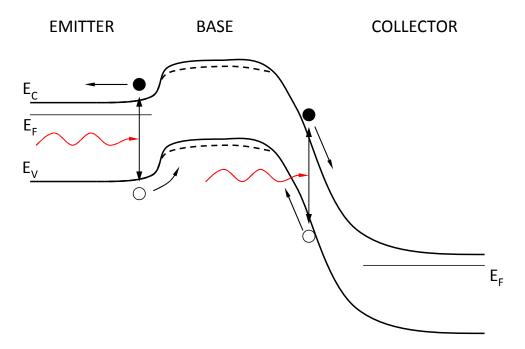

| 6.6 | Energy band diagram of a phototransistor. The dashed lines                     |     |

|     | indicate the change of the base potential caused by the                        |     |

|     | accumulation of photo-generated holes                                          | 119 |

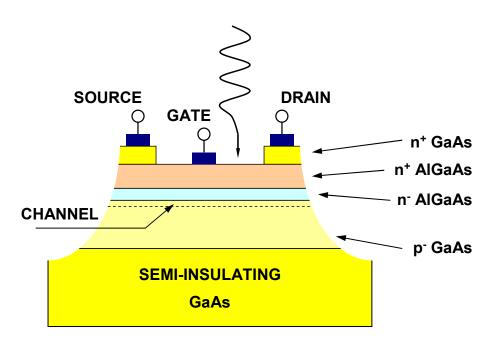

| 6.7 | Illustration of a typical photosensitive heterojunction field-effect           |     |

|     | transistor. The MESFET is configured as a modulation-doped                     |     |

|     | transistor                                                                     | 120 |

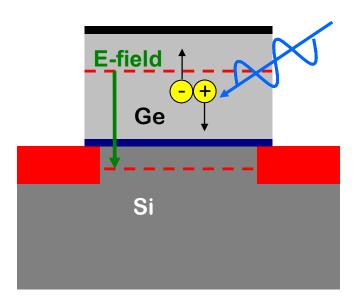

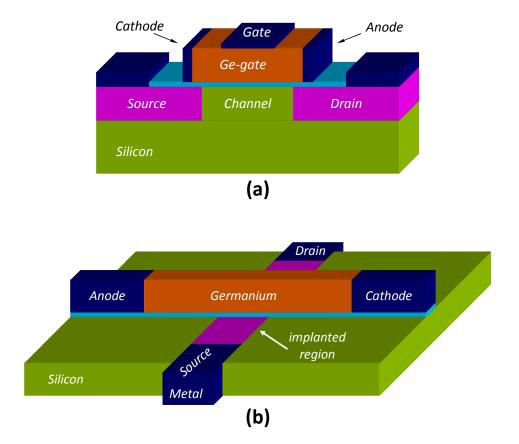

| 6.8 | Schematic of the optoelectronic MOSFET - cross section.                        |     |

|     | Source/drain and channel regions are formed in Si. Ge gate is                  |     |

|     | deposited and it is isolated from the channel by thermally grown               |     |

|     | SiO2. Light can be coupled by normal incidence or by a through                 |     |

|     | waveguide scheme. Light in the 1.3-1.55µm window is absorbed in                |     |

|     | Ge gate only. Due to large bandgap energy of Si, no absorption                 |     |

|     | takes place in the channel; hence the surrounding Si circuit is noise          |     |

|     | immune                                                                         | 121 |

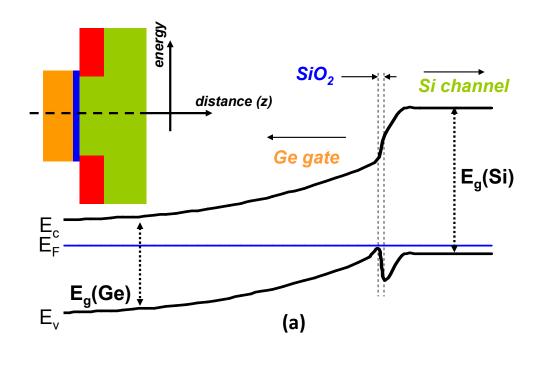

| 6.9 | (a) Energy band diagram of Ge-SiO <sub>2</sub> -Si stack under equilibrium.    |     |

|     | (b) Band bending under steady state illumination is shown with the             |     |

|     | dotted lines. Optically generated carriers accumulate at either side           |     |

|     | of the gate dielectric. This photo-excited charge modifies the                 |     |

|     | electric field across the stack. In the case illustrated here, holes           |     |

|     | accumulate at the Ge-SiO <sub>2</sub> interface, while the electrons are swept |     |

|     | towards SiO <sub>2</sub> -Si interface inducing a channel                      | 123 |

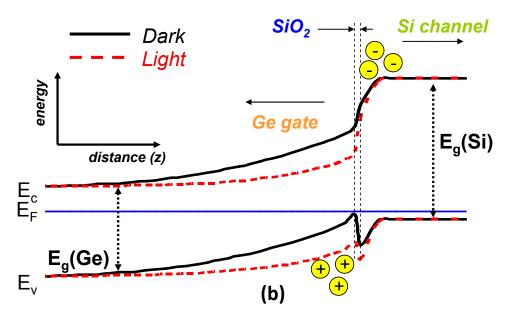

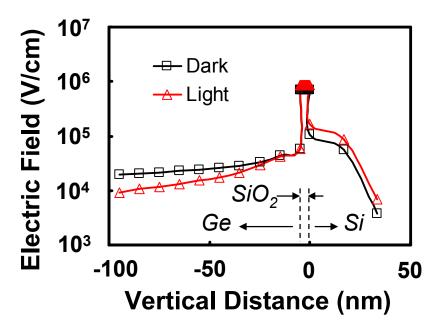

| 6.10 | Vertical electric field across the Ge-SiO <sub>2</sub> -Si stack with and without                          |       |

|------|------------------------------------------------------------------------------------------------------------|-------|

|      | light. Voltage distribution across the structure is modified by                                            |       |

|      | redistribution of optically generated carriers                                                             | . 124 |

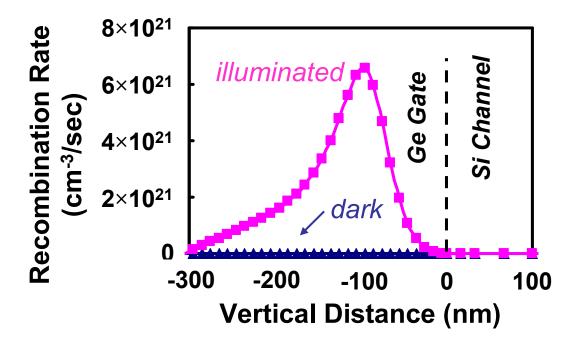

| 6.11 | Net recombination rate in the Ge-gate region under illumination.                                           |       |

|      | Recombination is negligible when there is no light. When the light                                         |       |

|      | turns off, excess carriers in the gate recombine which is one of the                                       |       |

|      | mechanisms responsible for device turn-off                                                                 | . 125 |

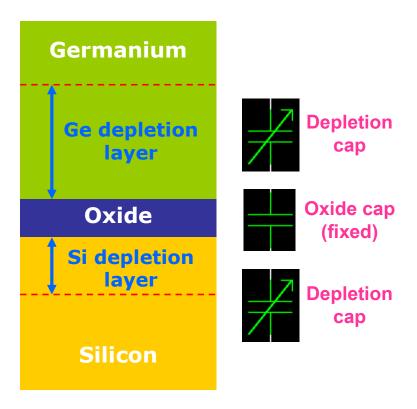

| 6.12 | The series combination of the oxide capacitor and the two                                                  |       |

|      | semiconductor depletion layer capacitances. The oxide capacitance                                          |       |

|      | is fixed while the Ge and Si depletion capacitance vary with the                                           |       |

|      | bias. The equivalent capacitance is dictated by the smallest among                                         |       |

|      | the three. Therefore, it is desirable to have the oxide capacitance                                        |       |

|      | much larger compared to the Ge capacitance                                                                 | . 126 |

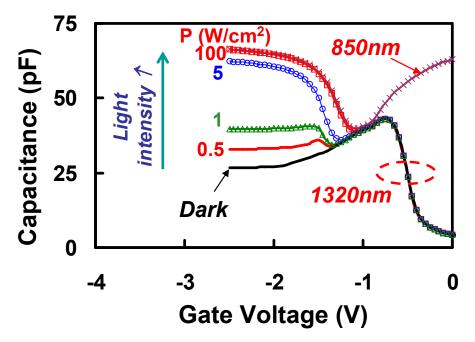

| 6.13 | Simulated $C_{\text{gate}}\text{-}V_{\text{gate}}$ with varying light intensity of Ge-SiO <sub>2</sub> -Si |       |

|      | stack. Only Ge depletion capacitance is modulated by 1320 nm                                               |       |

|      | light. Si also absorbs at 850 nm, hence Si depletion capacitance is                                        |       |

|      | also modulated with light at this wavelength                                                               | . 127 |

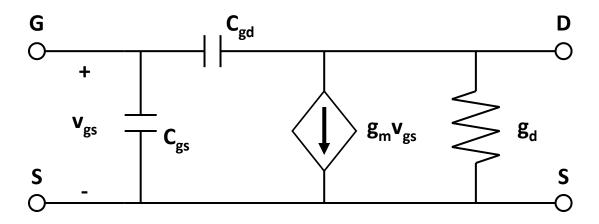

| 6.14 | Schematic illustration of the small signal ac equivalent circuit of a                                      |       |

|      | MOSFET. The MOSFET is modeled as a voltage controlled                                                      |       |

|      | current source. The gate voltage is amplified at the drain terminal                                        |       |

|      | by the transconductance and the drain conductance. Similarly, the                                          |       |

|      | drain current is an amplified version of the gate current due to the                                       |       |

|      | FET gain                                                                                                   | . 128 |

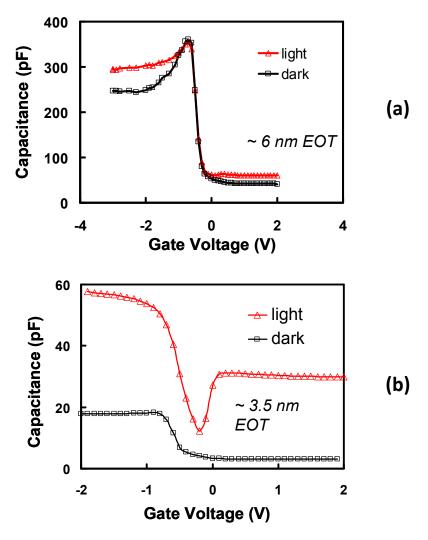

| 6.15 | Experimental high frequency (100kHz) $C_{\text{GATE}}$ - $V_{\text{GATE}}$ results. $SiO_2$                |       |

|      | thickness (a) 6 nm and (b) 3.5 nm. Due to experimental                                                     |       |

|      | difficulties, visible microscope light is used in measurements. Si                                         |       |

|      | also absorbs at this wavelength and hence Si depletion capacitance,                                        |       |

|      | dominant when V <sub>GATE</sub> >0, is also modulated                                                      | . 131 |

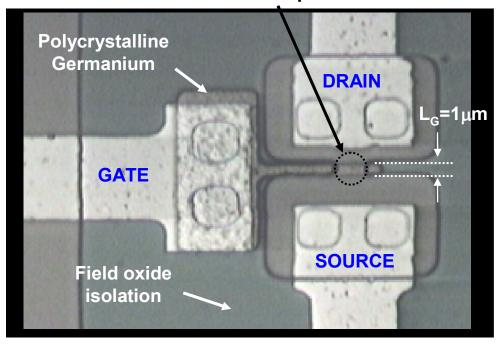

| 6.16 | Optical micrograph of the completed OE MOSFET with (a) 1 $\mu m$                                           |       |

|      | and (b) 100 µm gate length                                                                                 | . 135 |

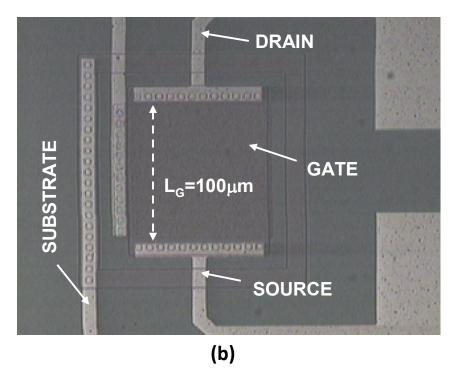

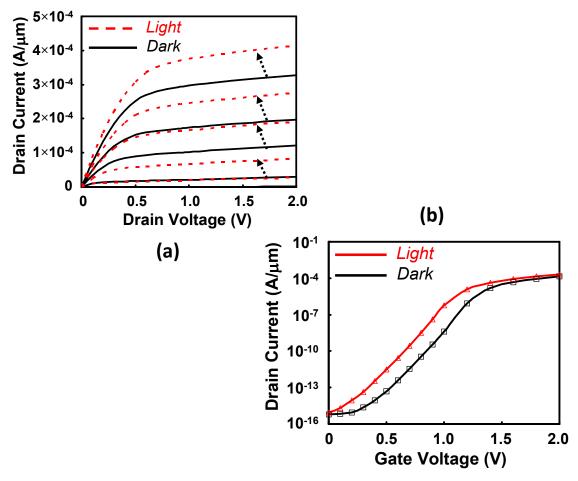

| 6.17 | (a) Simulated $I_{DRAIN}\mbox{-}V_{DRAIN}$ results of a $1\mu m$ gate length transistor                            |     |

|------|--------------------------------------------------------------------------------------------------------------------|-----|

|      | with n-doped Ge (10 <sup>16</sup> cm <sup>-3</sup> ) and p-doped Si (10 <sup>18</sup> cm <sup>-3</sup> ). Incident |     |

|      | light (1 $\mu W/\mu m^2$ in this case) constitutes a gate signal. (b) $I_{DRAIN}$                                  |     |

|      | $V_{\text{GATE}}$ characteristics of the same device. The curve is shifted due                                     |     |

|      | to the incident light                                                                                              | 136 |

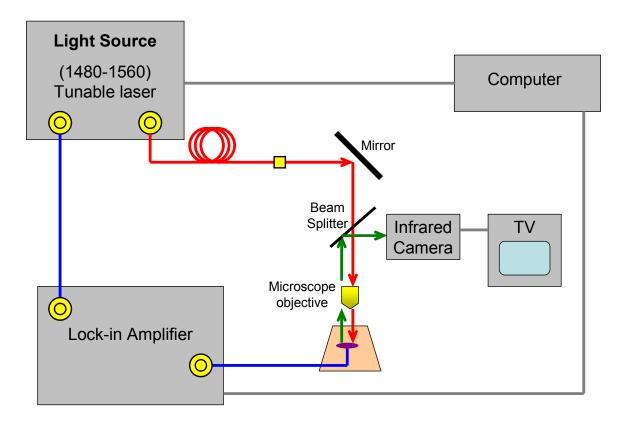

| 6.18 | Schematic of the experimental measurement setup                                                                    | 137 |

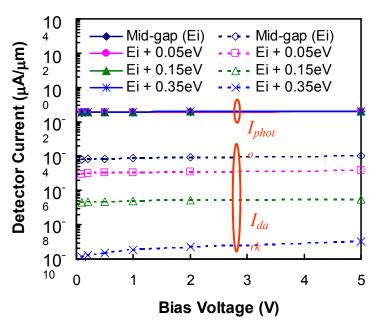

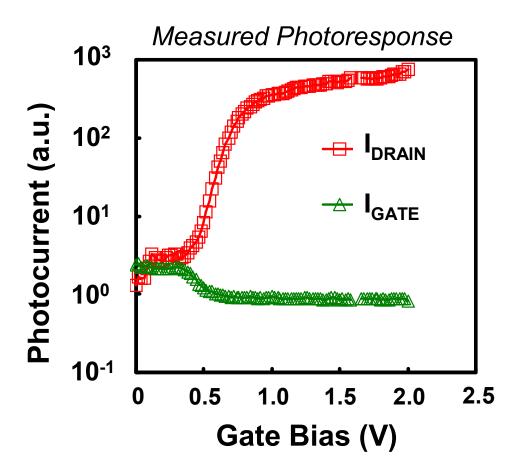

| 6.19 | Measured photocurrent at the gate and drain terminals when                                                         |     |

|      | $V_{GATE}$ = $V_{DRAIN}$ . The dc current is below measurement noise limit.                                        |     |

|      | The flow of optically generated carriers in the gate constitutes a                                                 |     |

|      | gate current, $I_{\text{GATE}}$ , which is amplified by the transconductance of                                    |     |

|      | the FET at the drain terminal, $I_{DRAIN}$ . Lock-in technique was used                                            |     |

|      | to precisely extract the optical currents                                                                          | 138 |

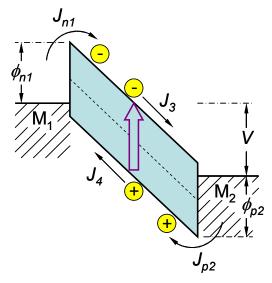

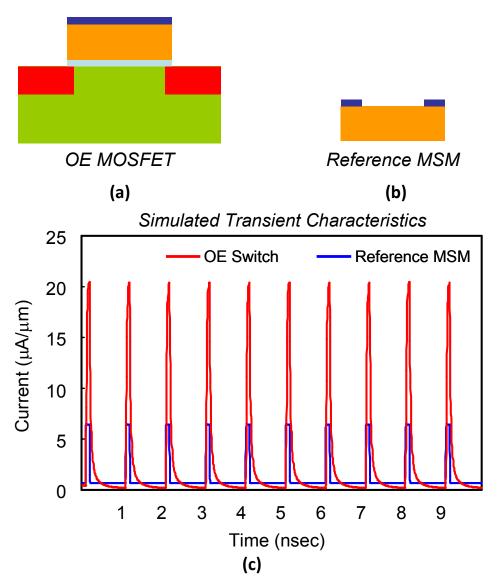

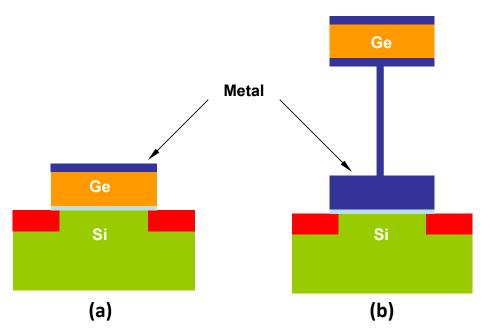

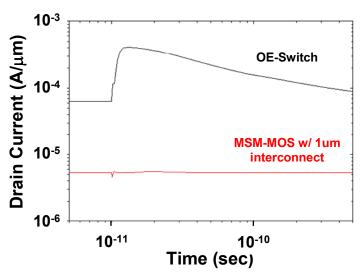

| 6.20 | Schematic illustration of (a) OE-MOSFET (b) traditional Ge MSM                                                     |     |

|      | photodetector. The slab of Ge is identical in both structures. (c)                                                 |     |

|      | Simulated transient response comparing the classical detector in                                                   |     |

|      | (b) and the proposed device in (a). The input is a pulse train, each                                               |     |

|      | pulse delivering 1 fJ opticalenergy                                                                                | 140 |

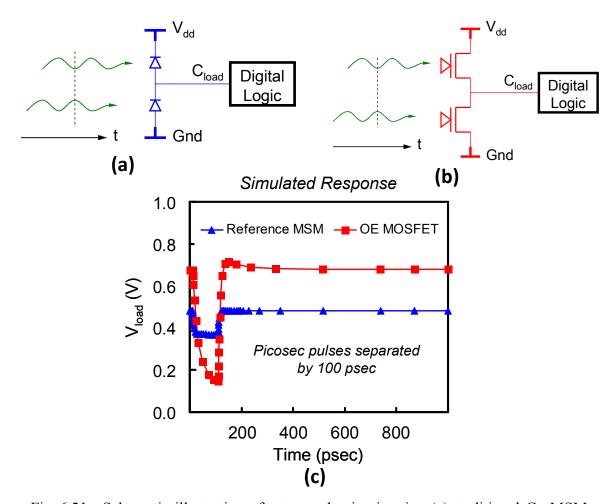

| 6.21 | Schematic illustration of totem pole circuit using (a) traditional Ge                                              |     |

|      | MSM photodetector (b) OE MOSFET. (c) Simulated transient                                                           |     |

|      | response. In each case, the input is two short optical pulses delayed                                              |     |

|      | by 100 psec and delivering $10^{-17}$ J optical energy. The OE                                                     |     |

|      | MOSFET provides $> 4 \times$ voltage swing with identical input optical                                            |     |

|      | energy, driving identical capacitors                                                                               | 141 |

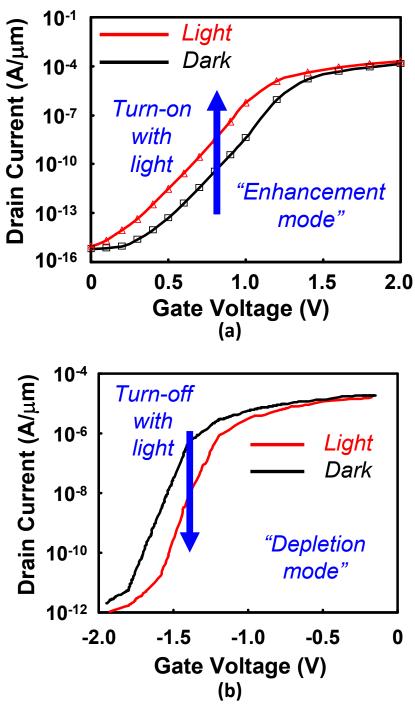

| 6.22 | (a) Simulated $I_{DRAIN}$ - $V_{GATE}$ show the effective gate signaling by                                        |     |

|      | incoming light. The device is normally off and turns on when                                                       |     |

|      | illuminated with light, hence "enhancement mode" switch. (b)                                                       |     |

|      | $I_{DRAIN}\text{-}V_{GATE}$ characteristics of a normally on device. When                                          |     |

|      | illuminated, the device turns off (depletion mode). Gate and                                                       |     |

|      | channel doping types are switched to achieve this behavior; p-                                                     |     |

|      | doped Ge (10 <sup>16</sup> cm <sup>-3</sup> ) and n-doped Si (10 <sup>18</sup> cm <sup>-3</sup> )                  | 143 |

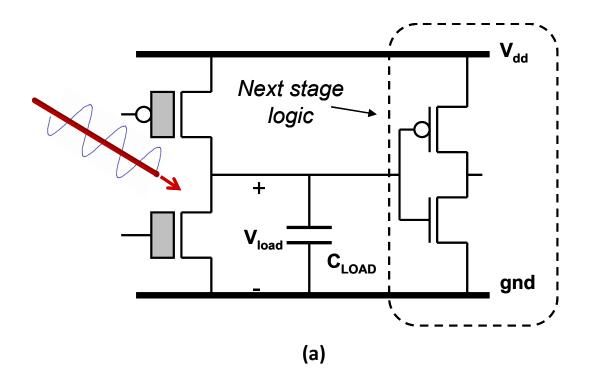

| 6.23 | (a) The complementary optical MOSFET pair connected as an             |     |

|------|-----------------------------------------------------------------------|-----|

|      | inverter. The next stage logic is resented with a load capacitor. The |     |

|      | capacitance is equal to that of a minimum sized inverter in 150 nm    |     |

|      | technology node. (b) The simulation mesh structure of the             |     |

|      | complementary pair forming an optically controlled electronic         |     |

|      | inverter                                                              | 145 |

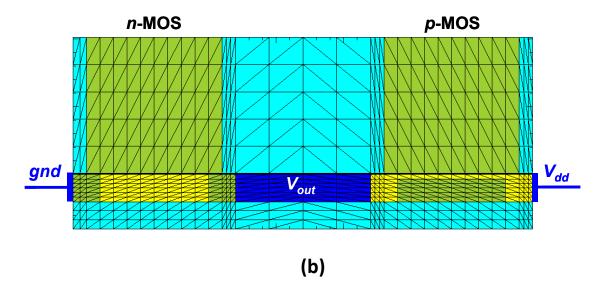

| 6.24 | Simulated transient response of the complementary optical             |     |

|      | MOSFET pair. The optically controlled electronic inverter is          |     |

|      | driving a minimum sized inverter as the next stage. Light pulse       |     |

|      | arrives at 10 psec. The output voltage is plotted vs time. It is      |     |

|      | possible to achieve very fast rail-to-rail swing even with no         |     |

|      | amplification stages                                                  | 146 |

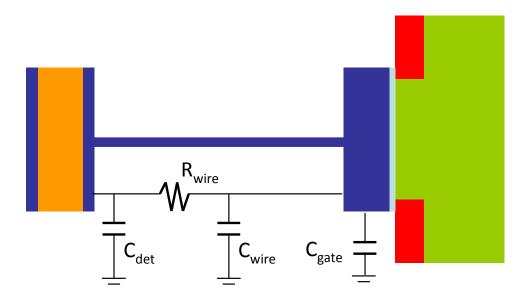

| 6.25 | (a) The OE MOSFET (b) Photodiode interconnected with a                |     |

|      | MOSFET                                                                | 147 |

| 6.26 | Photodiode interconnected with a MOSFET. The wire capacitance         |     |

|      | and resistance as well as the detector and gate capacitances are      |     |

|      | indicated                                                             | 148 |

| 6.27 | Transient simulation results comparing OE-switch with a               |     |

|      | photodiode directly connected to a MOSFET with 1 µm electrical        |     |

|      | interconnect. The wire capacitance is assumed to be 0.2 fF and the    |     |

|      | wire resistance is ignored                                            | 149 |

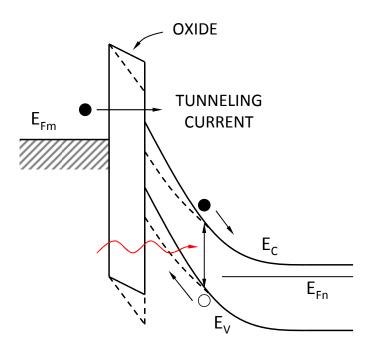

| 6.28 | Energy band diagram of the metal-insulator-semiconductor tunnel       |     |

|      | diode. Dashed lines indicate the response to light                    | 150 |

| 6.29 | Schematic illustration of (a) 2-D and (b) 3-D photo-FET. The          |     |

|      | switching speed is limited by the carrier transit time in the upper   |     |

|      | photodiode. A p-i-n or a planar MSM configuration can be used.        |     |

|      | Light can be coupled from the top or in a waveguide scheme            | 151 |

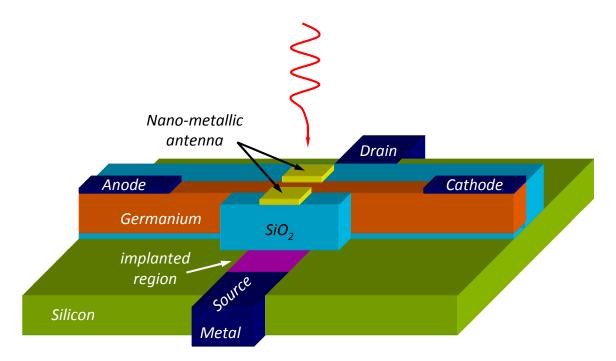

| 6.30 | Schematic illustration of integrated nano-metallic antenna with the   |     |

|      | OE switch. The plasmonic antenna can enhance the field around         |     |

|      | the absorbing gate region hence increasing the total absorbed         |     |

|      | optical power. Parts of the device are bisected and labeled ease of   |     |

|            | illustration. Anode and cathode collect the photo-generated carriers |     |

|------------|----------------------------------------------------------------------|-----|

|            | from the gate                                                        | 154 |

|            |                                                                      |     |

|            |                                                                      |     |

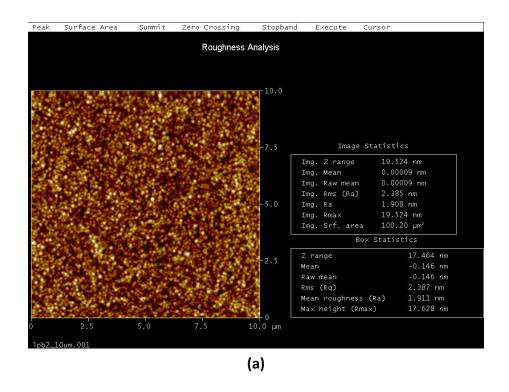

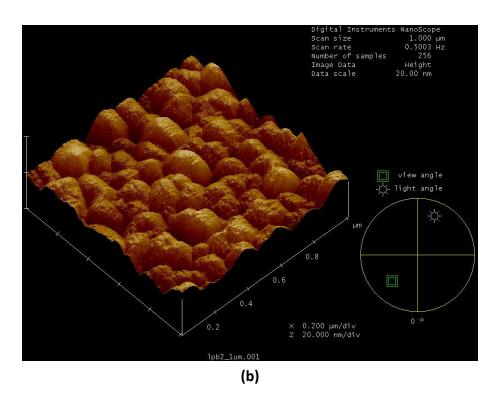

| A.1        | Typical (a) 10 μm and (b) 1 μm AFM surface scan of                   |     |

|            | polycrystalline Ge layers grown on Si                                | 171 |

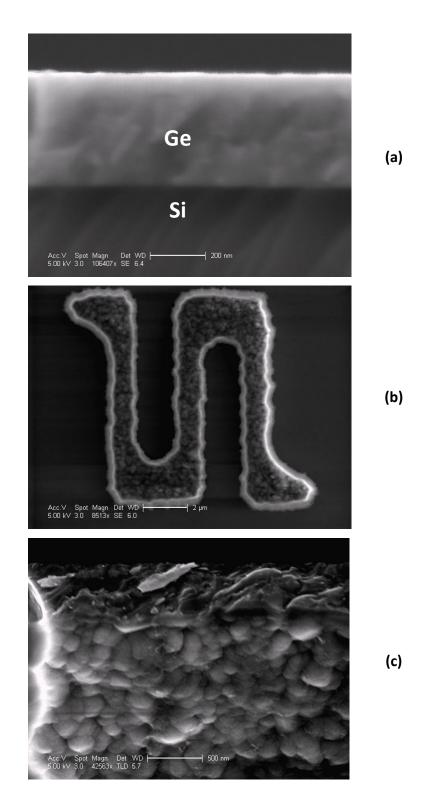

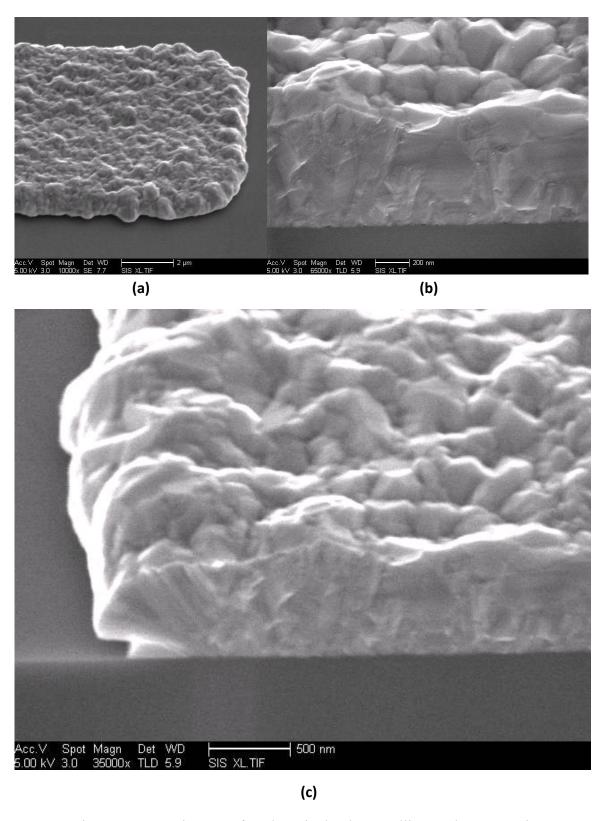

| <b>A.2</b> | SEM images of (a) amorphous Ge film on Si (b) and (c) granular       |     |

|            | structure of the layer after thermal crystallization                 | 172 |

| <b>A.3</b> | SEM images of as-deposited polycrystalline Ge layers on Si           | 173 |

| <b>A.4</b> | SEM image of a Si cap layer on polycrystalline Ge film deposited     |     |

|            | on Si                                                                | 174 |

**CHAPTER 1: INTRODUCTION**

Somewhere, something incredible is waiting to be known.

Carl Sagan

This dissertation describes our contributions to the integrated photonics, optical detection

technologies and optoelectronic transformation devices [1-25]. This introductory chapter

begins with a brief historical background and discussion of the motivation of this work.

The limitations of electrical wires and benefits of optical links are summarized. Finally,

the organization of the dissertation is presented.

1.1 MOTIVATION

Since their invention more than half a century ago, transistors have driven and dominated

the semiconductor industry. In 1965, five years after the first practical demonstration of

metal oxide semiconductor field effect transistor (MOSFET), Gordon Moore observed

that the number of transistors in an integrated circuit (IC) was doubling every two years

[26] as a result of a dramatic scaling of the feature sizes. While individual logic elements

have become significantly smaller and faster, computational speed is limited by the

communication between different parts of digital systems. This bottleneck is identified as

one of the grand challenges in the progress of integrated electronics [27].

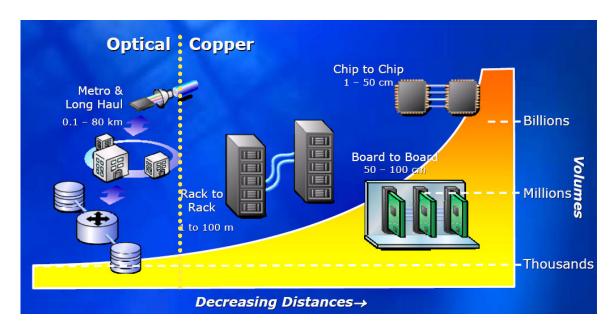

The chain of telecommunication systems from ultra-long distances in metro networks

down to chip scale communications versus the business volume of the corresponding

technology is illustrated in Fig. 1.1 [28]. Since the introduction of low-loss silica fibers,

optics has been dominating the long haul communications and it has consistently made its

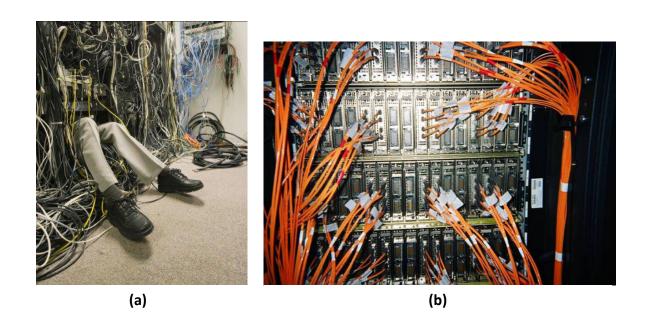

way down to shorter distances. Today, optics has moved deep into systems and already

reached into the server cabinet as depicted in Fig. 1.2 [29]. There are many physical

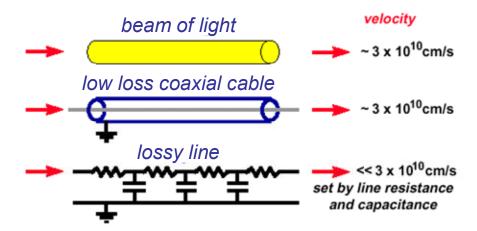

reasons for replacing electrical cables with optics [30-34]. Signals in both optical and

electrical links are carried by electromagnetic waves. Information in typical electrical

wires such as coaxial cables propagates almost at the velocity of light similar to that in

optical links as illustrated in Fig. 1.3 [34]. However, as the modulation frequencies

1

Fig. 1.1 The chain of communication systems versus the length of the interconnection and the business volume of the corresponding technology.

Fig. 1.2 A typical server cabinet with (a) electrical cables (b) optical links interconnecting between different sections.

increase, the traditional electrical wires are becoming increasingly resistive and the signals move at a slower rate due to dissipative wave propagation. Even the low-loss electrical wires suffer from skin effect, the phenomenon by which conduction takes place only in an increasingly thin layer near the surface of a conductor at higher frequencies. Signal distortion is becoming a significant problem in deeply scaled wires due to increasing copper resistivity and signal attenuation. Furthermore, electrical wires suffer from cross-talk due to electromagnetic interference. The cost of electrical lines has become an important issue. In other words, it is increasingly more expensive to run electrical wires at growing bitrates.

Fig. 1.3 Illustration of types of optical and electrical propagation and their velocities. (After [34])

An excellent review of the potential benefits offered by optical interconnections is presented in [34] based on the fundamental physical differences of the higher frequency, shorter wavelength and larger photon energy of optics compared to electrical interconnections. Optics has negligible propagation loss from large bandwidth signals because the carrier frequency of light is very high compared to any practical modulation frequency. On the other hand, electrical interconnections suffer from significant signal distortion and frequency dependent cross-talk at high modulation frequencies. Optics further enjoy unique benefits such as increased timing precision owing to short optical pulses and the ability to transmit multi-channels down a single optical link thanks to wavelength division multiplexing. Both of these advantages are quite common and easy

to produce in optics. Another substantial advantage of optics is the relative ease of guiding the optical wave. The transmitted signal can be confined into the material boundaries of the guiding medium owing to the small wavelength of the optical signals. The large photon energy of light provides voltage isolation between the transmitter and receiver. In addition, optics inherently offers an eloquent solution to the impedance matching crisis faced by electronics owing to the quantum nature of the physical processes [34-37]. While electronic devices have high impedance and low capacitance, the communication between such devices rely on low impedance and high capacitance transmission lines. Line drivers are employed to match the impedance which results in increased power dissipation and chip area at high operation frequencies. Thanks to the quantum nature of the optical impedance transformers, the classical field or voltage is irrelevant. For instance, in a photodiode, the number of electrons and hence the classical voltage that can be extracted is related to the number of photons, therefore the optical power.

#### 1.2 ORGANIZATION OF THE DISSERTATION

Chapter 2 is a brief introduction to advantages and challenges of optical interconnections. The challenges facing electrical wires particularly in chip-to-chip and on-chip communications are summarized. The architecture and operation of traditional optical interconnections are introduced with emphasis on the receiving end of the link.

Chapter 3 describes the dark current reduction mechanisms in metal-semiconductormetal photodetectors by using asymmetric workfunction and area metal electrodes. Each technique is also demonstrated experimentally on Si and Ge wafers.

Chapter 4 reports on the integration of high efficiency Ge-based photodetectors with Si. The challenge of obtaining high quality Ge layers on Si is briefly described with a summary of past research. The first part of this chapter introduces a new technique to grow Ge heteroepitaxially on Si and presents the characterization results of the layers. The second part explores photodetectors built using such layers and reports the experimental performance of the detectors.

Chapter 5 describes the integration of photodetectors with waveguides based on a robust polymer technology. The polymer waveguide technology which was developed elsewhere is briefly introduced. The experimental results of coupling light into photodetectors and influence of the polymer processing on detector performance are presented.

Chapter 6 presents the optoelectronic switch, a newly introduced optical-to-electronic transformer. This chapter begins with a historical background on phototransistors and FET based optical detectors. The first part of Chapter 6 discusses the structure and the operation of the switch. The principle of the device is explored by simulations and demonstrated by experiments. The second part of this chapter focuses on various applications and benefits of the switch as an optical to electronic conversion device.

Chapter 7 concludes with a brief summary of the key achievements of the dissertation, and briefly discusses future work.

#### REFERENCES

- 1. A. K. Okyay, C. O. Chui, and K. C. Saraswat, "Asymmetric Group IV MSM Photodetectors with Reduced Dark Currents," *IEEE CLEO/QELS 2003*, Paper CTuD4, Baltimore, MD, June 3-5, 2003.

- 2. C. O. Chui, A. K. Okyay, and K. C. Saraswat, "Effective Dark Current Suppression with Asymmetric MSM Photodetectors in Group IV Semiconductors," *IEEE Photon. Technol. Lett.*, **15**, 11, 1585-1587 (2003).

- 3. M. S. Bakir, C. O. Chui, A. K. Okyay, K. C. Saraswat, and J. D. Meindl, "Integration of Optical Polymer Pillars Chip I/O Interconnections with Si MSM Photodetectors," *IEEE Trans. Electron Devices*, **51**, 7, 1084-1090 (2004).

- K. C. Saraswat, C. O. Chui, T. Krishnamohan, A. K. Okyay, H. Kim and P. C. McIntyre, "Germanium for High Performance MOSFETs and Integrated Optical Interconnects," *The 2004 International Conference on Solid State Devices and Materials (SSDM) Technical Digest*, Tokyo, Japan, September 14-17, 2004.

- 5. K. C. Saraswat, C. O. Chui, Ammar Nayfeh, Hyoungsub Kim, A. K. Okyay and Paul McIntyre, "Ge Based High Performance Nanoscale MOSFETs and Integrated Optical Interconnects," *SEMICON West 2004*, STS:ISM, San Farancisco, July 12-16, 2004.

- 6. A. K. Okyay, C. O. Chui, M. S. Bakir, J. D. Meindl and K. C. Saraswat, "Integration of Polymer Pillar Optical Interconnects with Group IV MSM Photodetectors," *MRS* 2005 Spring Meeting, Symposium on Materials, Integration, and Technology for Monolithic Instruments, Paper D4.1, San Francisco, CA, March 28 April 1, 2005.

- 7. A. K. Okyay, C. O. Chui, and K. C. Saraswat, "A Novel Technique to Reduce Leakage in Metal-Semiconductor-Metal Photodetectors," *IEEE 63rd Annual Device Research Conference (DRC) Digest*, Santa Barbara, CA, June 20-22, 2005.

- 8. K. C. Saraswat, C. O. Chui, P. Kapur, T. Krishnamohan, A. Nayfeh, A. K. Okyay, and R. S. Shenoy, "Performance Limitations of Si CMOS and Alternatives for Nanoelectronics," *Int. J. High Speed Electron. and Sys.*, **16**, 1, 175-192 (2006).

- 9. A. K. Okyay, C. O. Chui, and K. C. Saraswat, "A Novel Technique to Reduce Leakage in Metal-Semiconductor-Metal Photodetectors," *Appl. Phys. Lett.*, **88**, 063506 (2006).

- 10. A. K. Okyay, A. Nayfeh, T. Yonehara, A. Marshall, P. C. McIntyre, and K. C. Saraswat, "Ge on Si Novel Heteroepitaxy for High Efficiency Near Infrared Photodetection," *IEEE CLEO/QELS* 2006, Paper CTuU5, Long Beach, CA, May 21-26, 2006.

- L. Tang, A. K. Okyay, J. A. Matteo, Y. Yuen, K. C. Saraswat, L. Hesselink, D. A. B. Miller, "C-shaped Nano-Aperture-Enhanced Germanium Photodetector," *NANO* 2006, Paper NThB5, Uncasville, CT, Apr 26-28, 2006.

- L. Tang, A. K. Okyay, J. A. Matteo, Y. Yuen, K. C. Saraswat, L. Hesselink, D. A. B. Miller, "C-shaped Nano-Aperture-Enhanced Germanium Photodetector," *Opt. Lett.*, 31, 10, 1519-1521 (2006).

- 13. A. K. Okyay, A. Nayfeh, T. Yonehara, A. Marshall, P. C. McIntyre, and K. C. Saraswat, "High Efficiency MSM Photodetectors on Heteroepitaxially Grown Ge on Si," *Opt. Lett.*, **31**, 17, 2565-2567 (2006).

- 14. A. K. Okyay, A. Nayfeh, N. Ozguven, T. Yonehara, A. Marshall, P. C. McIntyre, and K. C. Saraswat, "Strain Enhanced High Efficiency Germanium Photodetectors in the Near Infrared for Integration with Si," *IEEE LEOS 2006*, Paper WD2, Montreal, Canada, Oct 29 Nov 2, 2006.

- 15. A. K. Okyay, A. J. Pethe, D. Kuzum, S. Latif, D. A. B. Miller, and K. C. Saraswat, "Novel Si-based CMOS Optoelectronic Switching Device Operating in the Near Infrared," *OFC* 2007, Paper JWA38, Annaheim, California, USA, Mar 25 - Mar 29, 2007.

- 16. A. K. Okyay, A. J. Pethe, D. Kuzum, S. Latif, D. A. B. Miller, and K. C. Saraswat, "Novel SiGe Optoelectronic MOSFET," *Opt. Lett.*, **32**, 14 (2007).

- 17. A. K. Okyay, A. J. Pethe, D. Kuzum, S. Latif, D. A. B. Miller, and K. C. Saraswat, "Novel Si-based Optoelectronic Switching Device: Light to Latch," *IEEE CLEO/QELS* 2007, Paper CMP1, Baltimore, MD, May 6-11, 2007.

- L. Tang, E. Kocabas, S. Latif, A. K. Okyay, D. Ly-Gagnon, K. C. Saraswat, and D. A. B. Miller, "Near-Infrared Photodetector Enhanced by an Open-Sleeve Dipole Antenna," *IPNRA* 2007, Paper ITuD3, Salt Lake City, Utah, USA, Jul 8 Jul 11, 2007

- L. Tang, E. Kocabas, S. Latif, A. K. Okyay, D. Ly-Gagnon, K. C. Saraswat, and D. A. B. Miller, "Nanometre-Scale Germanium Photodetector Enhanced by a Near-Infrared Dipole Antenna," *submitted to Nature Photonics* (2007).

- 20. O. Fidaner, A. K. Okyay, J. E. Roth, R. K. Schaevitz, Y. H. Kuo, K. C. Saraswat, J. S. Harris, and D. A. B. Miller, "Ge/SiGe Quantum Well Waveguide Photodetectors on Silicon for the Near-Infrared," *submitted to IEEE Photon. Technol. Lett.* (2007).

- 21. A. K. Okyay, D. Kuzum, S. Latif, D. A. B. Miller, and K. C. Saraswat, "CMOS Compatible Silicon-Germanium Optoelectronic Switching Device: Bringing Light to Latch," *submitted to IEEE Trans. Electron Devices* (2007).

- 22. O. Fidaner, A. K. Okyay, J. E. Roth, Y. H. Kuo, K. C. Saraswat, J. S. Harris, and D. A. B. Miller, "Waveguide Electroabsorption Modulator on Si Employing Ge/SiGe Quantum Wells," *submitted to OSA FiO* (2007).

- 23. Yongho Choi, Leila Noriega, Ashkan Behnam, Pawan Kapur, Günhan Ertosun, A. K. Okyay, Zhuangchun Wu, Andrew G. Rinzler, Krishna C. Saraswat and Ant Ural, "Metal-semiconductor-metal photodetectors with transparent carbon nanotube film Schottky electrodes," *submitted to Appl. Phys. Lett.* (2007).

- 24. A. K. Okyay, A. Nayfeh, N. Ozguven, T. Yonehara, A. Marshall, P. C. McIntyre, and K. C. Saraswat, "Tensile strain enhanced high efficiency Ge optical detectors on Si," *in preparation, to be submitted to J. Lightwave Technol.*, (2007).

- 25. A. K. Okyay, and K. C. Saraswat, "Optical to electronic conversion at the nano-scale by a MOSFET based transformer," *in preparation, to be submitted to Appl. Phys. Lett.*, (2007).

- 26. G. E. Moore, "Cramming more components onto integrated circuits," *Electronics*, 38, 8, April 19, 1965.

- 27. [Internet resource] <a href="http://public.itrs.net/">http://public.itrs.net/</a>

- 28. J. Bautista, "Tera-Scale CPU Directions and Power-Performance I/O Bandwidth Issues," *MARCO Interconnect Focus Center*, Dec. 9, 2006.

- 29. A. Benner, "System Implications of Optical I/O," *MARCO Interconnect Focus Center*, Dec. 9, 2006.

- 30. J. W. Goodman, F. J. Leonberger, S. –Y. Kung, and R. A. Athale, "Optical interconnections for VLSI systems," *Proc. IEEE*, **72**, 850 (1984).

- 31. D. A. B. Miller, "Rationale and challenges for optical interconnects to electronic chips," *Proc. IEEE*, **88**, 728–749 (2000).

- 32. J. A. Davis, R. Venkatesan, A. Kaloyeros, M. Beylansky, S. J. Souri, K. Banerjee, K. C. Saraswat, A. Rahman, R. Reif, J. D. Meindl, "Interconnect limits on gigascale integration (GSI) in the 21st century," *Proc. IEEE*, 89, 305-324 (2001).

- 33. F. R. Feldman, S. C. Esener, C. C. Guest, and S. H. Lee, "Comparison between optical and electrical interconnects based on power and speed consideration," *Appl. Opt.*, **27**, 1972 (1988).

- 34. D. A. B. Miller, "Physical reasons for optical interconnection," *Int. J. Optoelectron*. **11**, 155-168 (1997).

- 35. D. A. B. Miller, "Optics for low-energy communication inside digital processors: quantum detectors, sources, and modulators as efficient impedance converters," *Opt. Lett.*, **14**, 2, 146-148 (1989).

- 36. V. V. Zhirnov, R. K. Cavin, J. A. Hutchny, and G. I. Bourianoff, "Limits to binary logic switch scaling a gedanken model," *Proc. IEEE*, **91**, 11, 1934-1939 (2003).

- 37. E. Yablanovitch, "Impedance Matching Crisis in Intra-Chip Communication," SRC Workshop, Asheville, 2005.

# CHAPTER 2: OPTICAL INTERCONNECTIONS: POTENTIALS AND CHALLENGES

This chapter gives a brief introduction to the critical directions and challenges optical interconnections. The problems facing electrical wires particularly in chip-to-chip and on-chip communications are summarized. The architecture and operation of traditional optical interconnections are introduced with emphasis on the receiving end of the link.

#### 2.1 INTRODUCTION

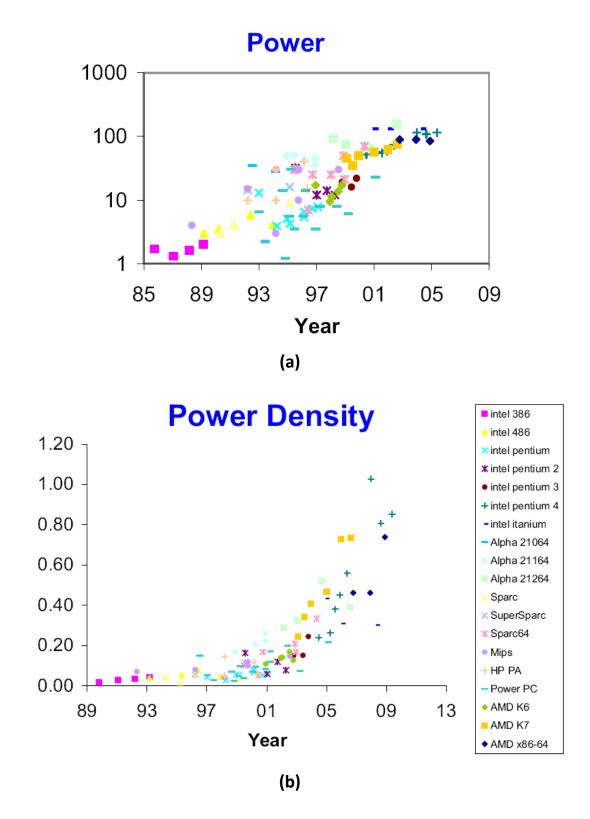

In the past decades, the number of functions per chip has grown exponentially as individual logic units became significantly faster and smaller in size. Today, all leading-edge microprocessors have transistor gate lengths and minimum line widths that are smaller than 100 nm. For the past 20 years, the total power dissipation on a chip has increased by two orders of magnitude from a couple of Watts to several 100s of Watts as shown in Fig. 2.1(a) [1]. The power density is rising at an even faster rate because the chip area is no longer increasing, Fig. 2.1(b). Electrical wires, which are efficient at short distances, begin to face fundamental limitations including excessive power dissipation, insufficient communication bandwidth, and signal latency [1-7]. Optical interconnects can provide a solution to the communications bottleneck by alleviating problems faced by electrical wires [8-14].

#### 2.2 INTER-CHIP INTERCONNECTS

Short distance links can be identified in three categories: (1) board-to-board, (2) chip-to-chip, and (3) on-chip. Optical interconnections are under active development for backplane applications [15,16]. The power dissipation of off-chip electrical and optical links vs. interconnect length are plotted in Fig. 2.2 for different technology nodes [17]. The critical length is defined as the length beyond which optics become more power efficient compared to their electrical counterparts. Fig. 2.2 shows that, as technology scales, optical links will become more power efficient at shorter distances. They are promising to increase the throughput and reduce cross-talk [12].

Fig. 2.1 (a) Total chip power vs. the year of introduction. (b) Chip power density vs. the year of introduction.

Fig. 2.2 Power dissipation of chip-to-chip interconnections vs. distance.

# 2.3 INTRA-CHIP INTERCONNECTS

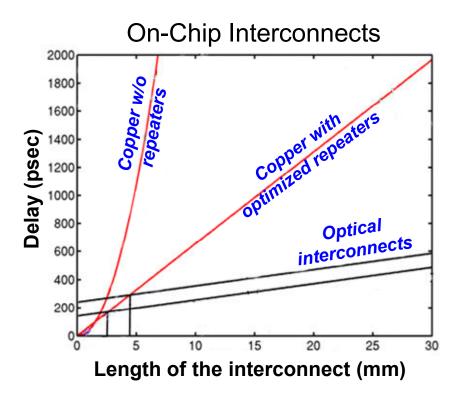

Recently, considerable attention is being paid to determine the feasibility of on-chip optical interconnects [9,13,14,18]. Modern on-chip electrical interconnections utilize copper wires surrounded by a low permittivity dielectric to propagate a signal. Global links on the chip that use long wires tend to exhibit high signal delays, and cross-talk noise. Fig. 2.3 plots the interconnect delay vs. length for on-chip links [9]. The electrical wire delay increases quadratically with distance because both line resistance and capacitance increase with the length of the wire. Long wires are broken down into shorter segments and signal repeaters are used to drive individual segments. This reduces the overall interconnect delay as it makes the delay linear with the interconnect length rather than quadratic. However, as the number of repeaters increase, so does the area and power penalty associated with the repeater circuitry.

Optics is promising to reduce overall interconnect power dissipation. Furthermore, it can increase timing precision by reducing the delay, skew and jitter. Moreover, optical interconnects do not suffer from electromagnetic interference.

Fig. 2.3 Delay of on-chip electrical and optical links vs. interconnect length.

# 2.4 ANATOMY OF OPTICAL INTERCONNECTS

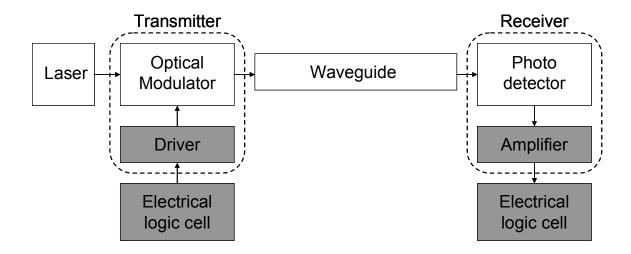

There are certain challenges for optics to meet in order to compete with electrical interconnections. Typical optical interconnects require high-speed and low power electronics as well as optical components. Fig. 2.4 illustrates the block diagram of a typical optical link in which light is generated by a continuous wave laser. The modulator is driven by electronic circuits such that it converts the electrical logic signal into an optical signal. The transmitted optical signal propagates in the waveguide to the receiving-end of the optical link. The photodetector converts the optical signal into electrical current which is then converted to electrical voltage by the transimpedance amplifier. The subsequent electronic circuitry amplifies the voltage to the logic level.

Fig. 2.4 Block diagram of a typical optical interconnect.

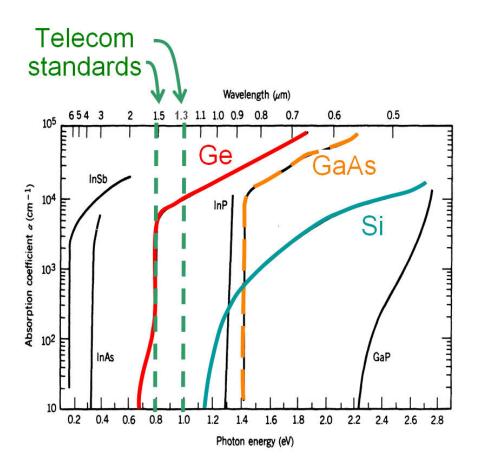

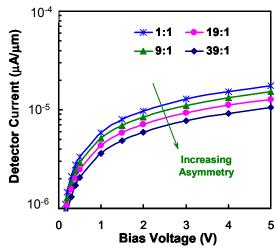

#### 2.5 MONOLITHIC INTEGRATION