# CLOCK SYNCHRONIZATION IN DISTRIBUTED SYSTEMS

MARTIN HORAUER

## DISSERTATION

## **Clock Synchronization in Distributed Systems**

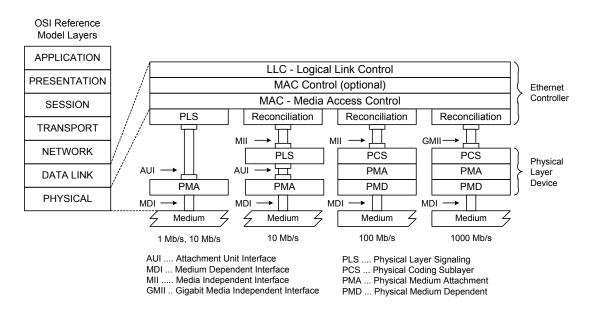

Architecture and Evaluation of Ethernet-based Network Interfaces with support for precision clock synchronization

ausgeführt zum Zwecke der Erlangung des akademischen Grades eines Doktors der technischen Wissenschaften unter der Leitung von

> UNIV.PROF. DR.TECHN. RICHARD EIER Institut für Computertechnik, E384

> > und

UNIV.PROF. DR.TECHN. ULRICH SCHMID Institut für Technische Informatik Embedded Computing Systems Group, E182/2

eingereicht an der Technischen Universität Wien Fakultät für Elektrotechnik und Informationstechnik

von

MARTIN HORAUER Matr.-Nr.: 8725430 Viehtriftgasse 4/2/8 A-1210 Wien

Wien, Februar 2004

#### **Martin Horauer:**

Clock Synchronization in Distributed Systems

Analysis and precision enhancement of existing clock synchronization mechanisms in distributed systems based solely on packet exchange via data links.

Analyse und Verbesserung der Präzision von bestehenden Mechanismen zur Uhrensynchronisation in einem verteilten System um mehr als eine Zehnerpotenz unter alleiniger Ausnutzung des Austausches von Datenpaketen über ein bestehendes Datennetzwerk.

Dissertation at the Department of Computer Technology, E384 at the University of Technology Vienna, Austria

This thesis evolved in the context of the research project SynUTC that has been supported by the Austrian Science Foundation (FWF) under grant P10244-ÖMA, the Austrian National Bank (OeNB) under grant 6454, the Austrian Federal Ministry of Science and Transport (BMWV) under contract Zl.601.577/2-iV/B/9/96, the START programme Y41-MAT as well as the Europractice initiative funded by the European Union.

The proposed concepts of this thesis are subject of an international patent submission (Patent Number: AT005327U1).

This thesis is dedicated to my father, who believed in me, put his hope in me, and never let me down.

## Kurzfassung

Die Synchronisation der einzelnen Uhren in den Rechner-Knoten ist ein elementares Service für ein verteiltes System. Durch Erhöhung der Genauigkeit wird dieses Service entscheidend verbessert welches dadurch neue Anwendungen ermöglicht. Ein Beispiel hierfür ist die Ortung von Notrufen, die von mobilen Telefonen aus getätigt werden. Die Genauigkeit der erreichbaren Ortung steht hier direkt in Relation zur erzielbaren Genauigkeit der Uhrensynchronisation. Gegenwärtig kann dies nur durch aufwendige Speziallösungen und der Verwendung von präzisen GPS Zeit-Empfängern realisiert werden. Aufgrund der erhöhten Kosten und der Anforderung, dass jeder GPS Empfänger mit einer Antenne mit freier Sicht auf den Himmel ausgestattet sein muss, wird die Anwendbarkeit derartiger Systeme jedoch oft stark eingeschränkt.

Der jüngst veröffentliche IEEE Standard 1588 für ein hochgenaues Protokoll zur Uhrensynchronisation für verteilte Messdatenerfassung, Regelung und Steuerung widmet sich genau dieser Problematik. Durch Aufrüstung bestehender Datennetzwerke mit Hardware-Erweiterungen zum abziehen und speichern der lokalen Uhrzeit an den Netzwerk-Schnittstellen und einem Software Protokoll-Stack gelingt es die "durchschnittlich" erreichbare Genauigkeit der Uhrensynchronisation in den Bereich unter eine  $\mu s$  zu bringen. Unabhängig von dem Standardisierungsprozess widmete sich das Forschungsprojekt SynUTC dieser Thematik. In diesem Forschungsprojekt wurden einige Prototypen gebaut und getestet sowie detaillierte theoretische Modelle entwickelt, die es erlauben die im schlechtesten Fall erreichbare Genauigkeit abzuschranken.

Basierend auf diesen Erkenntnissen und den Ergebnissen einschlägiger Fachliteratur wird in dieser Arbeit ein Konzept für die Architektur von Netzwerk Schnittstellen und Switches erarbeitet, das eine "im schlechtesten Fall garantierte Genauigkeit" der Uhrensynchronisation im Bereich von 100 *ns* ermöglicht. Dies wird durch transparentes Einfügen der lokalen Uhrzeit eines Knotens unmittelbar vor dem *Physical Layer* in eingehende und abgehende Datenpakete zur Uhrensynchronisation erreicht. Die lokale Uhrzeit eines Knotens wird in Hardware mit Hilfe eines hochauflösenden Addierers verwaltet, der es erlaubt sowohl den Uhrenstand als auch deren Rate kontinuierlich zu korrigieren. Die vorgestellte Architektur verbessert existierende Ansätze um mehr als eine Größenordnung ohne dabei die ursprüngliche Funktionalität des Netzwerkes zu verändern. Die Konzepte wurden an Hand eines ersten Prototypen funktional verifiziert und durch experimentelle Evaluation mit realen Messreihen untermauert und quantifiziert. Die vorgestellte Lösung ergänzt GPS basierte Verfahren zur Uhrensynchronisation, besonders dann wenn gesteigerte Anforderungen an Fehlertoleranz gegeben sind bzw. die Anbringung einer Antenne problematisch erscheint.

## Abstract

A system-wide global time base with known precision is of pivotal importance for the design and operation of distributed systems as well as an enabling technology for applications like location-based services. The increasing requirements of these driving applications and the large scale of the underlying systems demand clock synchronization down to the *ns*-range. To date, for many applications this cannot be established with present software synchronization strategies; specialized hardware support and the use of GPS-timing receivers is mandatory. The applicability of these solutions, however, is limited by the high cost for the additional, dedicated cabling and the antennas for the GPS receivers, which require clear-view of sky for proper operation.

Recently the IEEE approved the 1588 standard for a precision clock synchronization protocol for networked measurement and control systems. By equipping existing computer networks with moderate hardware extensions at the network interfaces and a standard protocol software stack, an average precision below the  $\mu$ s-range can be achieved. Independently from the balloting process and based on relevant scientific literature the research project SynUTC established a clock synchronization framework with sound theoretical concepts and well engineered hard- and software.

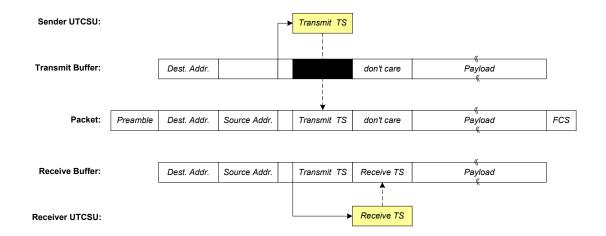

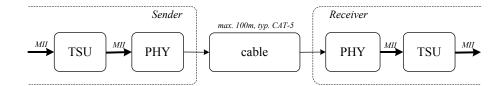

This thesis proposes an architecture for network interfaces and networked devices that will render a worst-case precision in the 100 ns-range possible. The proposed mechanism, which is applicable for any packet-oriented data network, inserts time information into data packets at the interface between the physical layer transceiver and the network controller upon packet transmission and reception, respectively. Local time is supplied by a high-resolution rate-adjustable adder-based clock, which also contains hardware support easing interval-based external clock synchronization, like maintaining time and accuracy intervals and interfaces to GPS receivers. This architecture allows an improvement of at least an order of magnitude over other existing solutions; it is accomplished by small modifications of existing commercial-off-the-shelf devices, without impairment of their original functionality. Part of the principle of operation is verified with a prototype implementation that was also used in conjunction with other devices for an experimental evaluation. The results of the presented experiments validate the proposed techniques and reveal actual values for the worst-case precision that might be achieved. The presented solution provides a synchronization that can otherwise be achieved only with the help of specialized GPS timing receivers, thus excellently complementing these solutions when increased fault-tolerance is required or when access to an antenna is not feasible.

## **Related Publications**

This thesis is based on and extends the work and results presented in the following papers and publications:

M. Horauer, Hardware Support for Clock Synchronization in Distributed Systems, Supplement of the 2001 International Conference on Dependable Systems and Networks, Göteborg, Sweden, 1-4 July 2001, pp. A-10 - A-13. (Best Student Paper)

M. Horauer, U. Schmid, K. Schossmaier, R. Höller and N. Kerö, **PSynUTC - Evalu**ation of a High Precision Time Synchronization Prototype System for Ethernet LANs, Proceedings of the 34<sup>th</sup> IEEE Precise Time and Time Interval Systems and Application Meeting (PTTI'02), Reston, Virginia, USA. December 2002.

M. Horauer and R. Höller, **Integration of high accurate Clock Synchronization into Ethernet-based Distributed Systems**, International Conference on Advances in Infrastructure for e-Business, e-Education, e-Science, and e-Medicine on the Internet, SSGRR 2002, Jan. 21 - 27, L'Aquila, Italy. (Serves as reference for the US Navy DoD 2003.2 SBIR Solicitation N03-200 "Automated On-Board and Off-Board Data Timing and Synchronization")

M. Horauer, N. Kerö and U. Schmid, A network interface for highly accurate clock synchronization, Proceedings Austrochip 2000, Oct. 2000, Graz Austria, ISBN 3-9501349-0-5.

R. Höller, G.Gridling, M. Horauer, N.Kerö, U.Schmid, and K. Schossmaier, **SynUTC - High Precision Time Synchronization over Ethernet Networks**, Proceedings of the 8<sup>th</sup> Workshop on Electronics for LHC Experiments, Colmar, France, 9-13 September, 2002.

U.Schmid, M.Horauer and N.Kerö, **How to Distribute GPS-Time over COTS-based LANs**, 31<sup>st</sup> Annual Precise Time and Time Interval (PTTI) Systems and Applications Meeting, Dana Point - California, December 7-9, 1999.

N. Kerö, U. Schmid, and M. Horauer, **Verfahren für die Synchronisation von Computeruhren in Netzwerken**, TR 183/1-105, Department of Automation, Vienna University of Technology, March 2000. (International Patent Submission: Patent No. AT005327U1)

The following publications are related but not covered in this thesis:

K. Schossmaier, U. Schmid, M. Horauer and D. Loy, **Specification and Implementation of the Universal Time Coordinated Synchronization Unit (UTCSU)**, Journal of Real-Time Systems, 1997 May, No. 3, Vol. 12, pp. 295–327.

M. Horauer, U. Schmid and K. Schossmaier, **NTI: A Network Time Interface M-Module for High-Accuracy Clock Synchronization**, Proceedings of the  $6^{th}$ International Workshop on Parallel and Distributed Real-Time Systems (WPDRTS), Orlando Florida USA, March 30 – April 3 1998.

N. Kerö, H. Muhr, G. Gaderer, R. Höller, T. Sauter and M.Horauer, **Embedded SynUTC and IEEE 1588 Clock Synchronization for Industrial Ethernet**, Workshop on IEEE-1588, Standard for a Precision Clock Synchronization Protocol for Networked Measurement and Control Systems, National Institute of Standards and Technology, Gaithersburg, Maryland USA, 24 September, 2003.

M. Horauer and D. Loy, **UTCLIENT - an ASIC Supporting Clock Synchronization in Distributed Real-Time Systems**, Proceedings of Austrochip '97, 1997 April, Linz Austria, pp. 290–296, ISBN 3 85320 826 6, Universitätsverlag Rudolf Trauner.

M. Horauer and D. Loy, **Hardware-unterstützte Uhrensynchronisation in verteilten Systemen**, Proceedings Austrochip 98 pp. 67–72, Wiener Neustadt, Austria, October 1998, ISBN 3-901578-03-X.

M. Horauer and D. Loy, Adder Synthesis, Proceedings of Austrochip '95, Graz Austria, pp. 81–87, 1995.

## Contents

| Kurzfassung |                      |                                            |         |     |     | i |  |   |  |     |   |     |

|-------------|----------------------|--------------------------------------------|---------|-----|-----|---|--|---|--|-----|---|-----|

| Ab          | ostrac               | t                                          |         |     |     |   |  |   |  |     |   | ii  |

| Re          | Related Publications |                                            |         |     |     |   |  |   |  |     |   | iii |

| 1           | Intro                | oduction                                   |         |     |     |   |  |   |  |     |   | 1   |

|             | 1.1                  | Clock Synchronization Strategies           |         |     |     |   |  |   |  |     |   | 1   |

|             | 1.2                  | Application Domain                         |         |     |     |   |  |   |  |     |   | 3   |

|             | 1.3                  | Outline                                    |         | ••• | ••• |   |  | • |  | ••• |   | 8   |

| 2           | State                | e of the Art of Clock Synchronization      |         |     |     |   |  |   |  |     |   | 10  |

|             | 2.1                  | System Modelling                           |         | ••• |     |   |  | • |  |     |   | 11  |

|             |                      | 2.1.1 Clocks and Processors                |         | ••• |     |   |  | • |  |     | • | 12  |

|             |                      | 2.1.2 Communication Subsystem              |         | ••• |     |   |  | • |  |     | • | 13  |

|             |                      | 2.1.3 Faults                               |         | ••• |     |   |  | • |  |     | • | 14  |

|             | 2.2                  | A taxonomy of clock synchronization algori | thms    | ••• |     |   |  | • |  |     |   | 15  |

|             |                      | 2.2.1 Structure of clock synchronization a | lgorith | ms  |     |   |  | • |  |     |   | 15  |

|             |                      | 2.2.2 Clock synchronization building bloc  | ks      | ••• |     |   |  | • |  |     |   | 16  |

|             | 2.3                  | Requirement analysis                       |         |     |     |   |  | • |  |     |   | 26  |

|             |                      | 2.3.1 Clock Properties                     |         |     |     |   |  | • |  |     |   | 26  |

|             |                      | 2.3.2 Clock Reading Error                  |         | ••• |     |   |  | • |  |     |   | 32  |

|             |                      | 2.3.3 Clock Granularity an Clock Rate Ad   |         |     |     |   |  |   |  |     |   | 34  |

|             |                      | 2.3.4 Coupling to an External Reference T  | Fime .  | ••• |     |   |  | • |  |     |   | 34  |

|             | 2.4                  | Summary                                    |         | ••• |     |   |  | • |  |     |   | 35  |

| 3           | Rela                 | ted Work                                   |         |     |     |   |  |   |  |     |   | 37  |

|             | 3.1                  | MARS - The Maintainable Real-Time System   | m       | ••• |     |   |  | • |  |     |   | 38  |

|             | 3.2                  | The Time-Triggered Protocol                |         | ••• |     |   |  |   |  |     |   | 40  |

|             | 3.3                  | The Network Time Interface                 |         |     |     |   |  |   |  |     |   | 43  |

|             | 3.4                  | IEEE Standard 1588                         |         |     |     |   |  | • |  |     |   | 45  |

|             | 3.5                  | Summary                                    |         |     |     |   |  |   |  |     |   | 47  |

| 4                          | Network interface architectures supporting tight clock synchronization |                                                                 |     |  |  |  |  |  |  |

|----------------------------|------------------------------------------------------------------------|-----------------------------------------------------------------|-----|--|--|--|--|--|--|

|                            | 4.1                                                                    | System Architecture                                             | 50  |  |  |  |  |  |  |

|                            | 4.2                                                                    | Network interface for End-systems                               | 54  |  |  |  |  |  |  |

|                            |                                                                        | 4.2.1 Clock synchronization support for Network Interface Cards | 55  |  |  |  |  |  |  |

|                            |                                                                        | 4.2.2 Prototype: MII-NTI                                        | 58  |  |  |  |  |  |  |

|                            | 4.3                                                                    |                                                                 | 60  |  |  |  |  |  |  |

|                            |                                                                        | I                                                               | 61  |  |  |  |  |  |  |

|                            |                                                                        |                                                                 | 62  |  |  |  |  |  |  |

|                            | 4.4                                                                    |                                                                 | 65  |  |  |  |  |  |  |

|                            |                                                                        | · · · · · · · · · · · · · · · · · · ·                           | 65  |  |  |  |  |  |  |

|                            |                                                                        |                                                                 | 69  |  |  |  |  |  |  |

|                            | 4.5                                                                    | Summary                                                         | 70  |  |  |  |  |  |  |

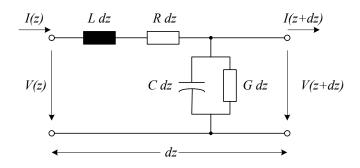

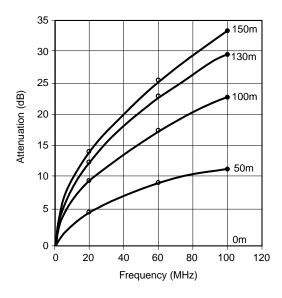

| 5                          | Dela                                                                   | ay variations of the Physical Layer                             | 72  |  |  |  |  |  |  |

|                            | 5.1                                                                    | Models of the physical communication link                       | 72  |  |  |  |  |  |  |

|                            |                                                                        |                                                                 | 72  |  |  |  |  |  |  |

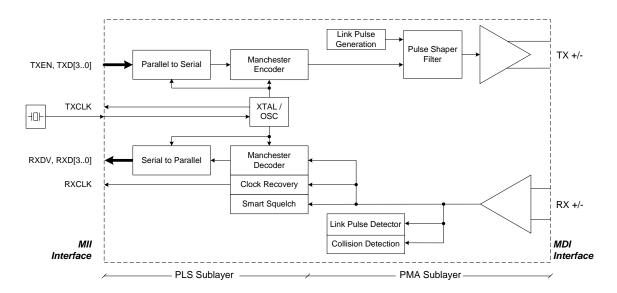

|                            |                                                                        | 5.1.2 10 Base-T Physical Layer Devices                          | 74  |  |  |  |  |  |  |

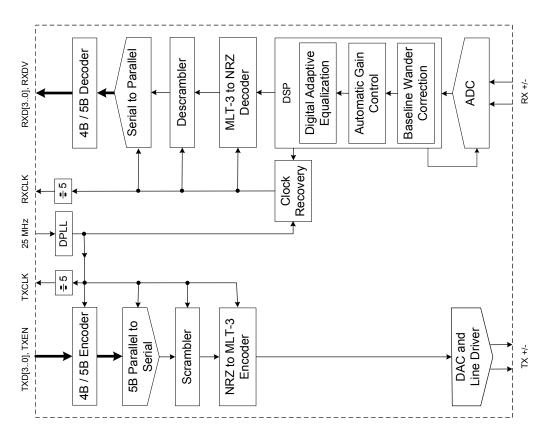

|                            |                                                                        | 5.1.3 100 Base-Tx Physical Layer Devices                        | 75  |  |  |  |  |  |  |

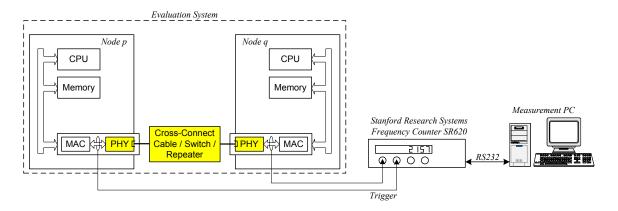

|                            | 5.2                                                                    | Evaluation                                                      | 79  |  |  |  |  |  |  |

|                            |                                                                        | 5.2.1 Evaluation System Hardware                                | 80  |  |  |  |  |  |  |

|                            |                                                                        |                                                                 | 80  |  |  |  |  |  |  |

|                            |                                                                        |                                                                 | 81  |  |  |  |  |  |  |

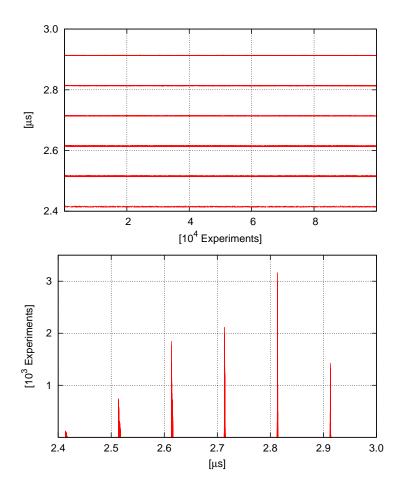

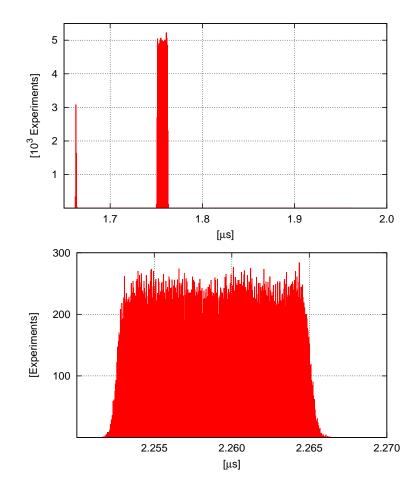

|                            | 5.3                                                                    |                                                                 | 83  |  |  |  |  |  |  |

|                            |                                                                        |                                                                 | 83  |  |  |  |  |  |  |

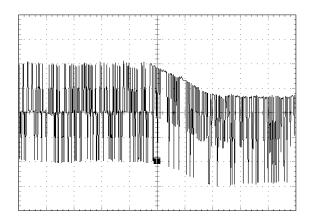

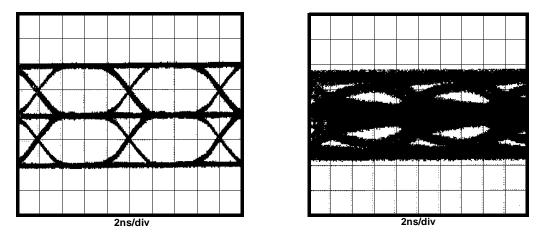

|                            |                                                                        |                                                                 | 95  |  |  |  |  |  |  |

|                            | 5.4                                                                    | Summary                                                         | 100 |  |  |  |  |  |  |

| 6                          | Con                                                                    | clusion and Future Work 1                                       | 103 |  |  |  |  |  |  |

| Bi                         | bliog                                                                  | raphy 1                                                         | 105 |  |  |  |  |  |  |

| Aj                         | ppend                                                                  | lix 1                                                           | 114 |  |  |  |  |  |  |

| Glossary and Abbreviations |                                                                        |                                                                 |     |  |  |  |  |  |  |

| Curriculum Vitae           |                                                                        |                                                                 |     |  |  |  |  |  |  |

## Introduction

Leslie Lamport's definition of a distributed system: "You know you have one when the crash of a computer you've never heard of stops you from getting any work done." [72]

A distributed system is a collection of autonomous computers linked by a computer network and supported by software that enables the collection to operate as an integrated facility. It is very easy to understand why these systems are popular. They allow the sharing of information and resources over a wide geographic spread and they are usually better than traditional centralized systems in terms of sharing, cost, growth and autonomy. In contrast, the above citation from Leslie Lamport states clearly that there are still some short-comings and weaknesses with existing implementations. The distributed nature of these systems has to cope with unreliable and insecure communications and independent failures. These problems become aggravated when the system is operating critical realtime applications such as aerospace systems, life support systems, nuclear power plants, drive-by-wire systems and computer-integrated manufacturing systems. Common to all these applications is the demand for maximum reliability and high performance from computer controllers, since a single controller failure in these applications can lead to disaster. Next to these an increasing number of distributed applications, such as process-control applications, transaction processing applications, or communication protocols, rely on autonomous computers that need to cooperate for initiation of actions or recording of events. Therefore, causal ordering is often required, a means that can be provided with the help of synchronized clocks so that every computer node has approximately the same view of time. In addition, when synchronized clocks are at hand the performance of a distributed system can be improved by reducing communication, see [59] for some practical uses. Other practical applications and uses will eventually emerge when tight clock synchronization becomes available at affordable costs. Therefore, the aim of this thesis is to analyze and underpin concepts for the improvement of existing hybrid clock synchronization mechanisms within a distributed system.

## **1.1 Clock Synchronization Strategies**

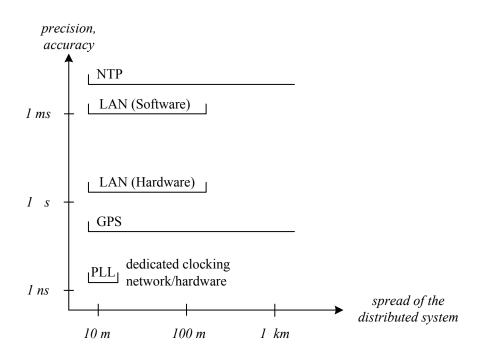

Clock synchronization may be achieved either by hardware or by software. A coarse classification of typical clock synchronization mechanisms is given in Fig. 1.1 depending on the required precision and the geographic spread of the distributed system.

- The Network Time Protocol (NTP) is a network protocol and a collection of algorithms for synchronizing computer clocks over packet networks and is mainly used throughout the Internet. Computers synchronize their local time to those on remote time-servers that are assumed to have the correct time, for details see [68] and [69]. Under some realistic conditions, maximum errors of approximately 20 ms were observed, cf. [105].

- For local area networks with soft real-time requirements synchronization in the range of some few *ms* is acceptable. Software clock synchronization algorithms use standard communication networks and send synchronization messages to get the clocks synchronized. Numerous solutions have been presented, analyzed and evaluated; see [82] or [100] for an overview and [114] for a comprehensive bibliography.

- When computer nodes are equipped with moderate hardware support, the software clock synchronization algorithms can yield synchronization tightness in the range of several μs. Such a mechanism was implemented in the MARS project, see [53], and a similar hybrid scheme of software synchronization with hardware assistance for homogeneous distributed systems although for a different network architecture can be found in [81].

Figure 1.1: Clock Synchronization classification

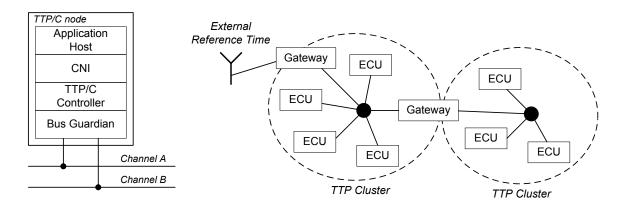

Our research project *Synchronized Universal Time Coordinated* (SynUTC) pursued the problem of how to establish an accurate common notion of time among the nodes of a distributed system relying on the same hybrid mechanism. The local clocks of every node are kept within a few  $\mu s$  of each other by solely exchanging dedicated network packets. By incorporating an external time source like a *Global Positioning System* (GPS) receiver the local time at every node is kept within a few  $\mu s$  of *Universal Time Coordinated* (UTC), the only official and legal standard time, as well. The recently established IEEE 1588 Standard that proposes a similar mechanism for tight clock synchronization also fits into this category, see [40].

- When every node can be equipped with a dedicated GPS Receiver clock synchronization in the range down to *100 ns* is possible, although such a pure coupling of common-of-the-shelf (COTS) receivers without additional means for clock validation is inadequate for safety critical applications as these devices exhibit some rare failures, see [29].

- Dedicated hardware support can yield synchronization accuracy down to several *ns*. These solutions require in general a dedicated clocking network along with appropriate synchronization hardware which operates similar to the phase-locked-loop technique. The additional cabling and hardware is only affordable for distributed nodes that are located within a few meters, as is the case, e.g., in multiprocessor systems [46].

The topics of this thesis address the problem of how to enhance the hybrid LAN-based clock synchronization architectures with moderate hardware support in order to enhance the achievable synchronization accuracy, in particular how to keep the nodes clocks within a distributed system bounded within some *ns* towards each other (= *precision*) and towards an external reference time (= *accuracy*), respectively. The presented work is very closely related to the newly established IEEE 1588 Standard and illustrates some deficiencies of this standard and how these could be overcome.

## **1.2 Application Domain**

Since clock synchronization is used throughout the spectrum of distributed systems starting from a single VLSI chip, and ranging up to a global network it is conceivable that the effect of even a slight improvement in the tightness of synchronization may be sweeping. For example, tighter synchronization of the transmitting and receiving endpoints of communication links can lead to better utilization and hence larger throughput of the communication network; better synchronization may imply shorter processing time for large databases. In order to state the benefits and usefulness of tighter clock synchronization in a distributed system more precisely, we present some examples that may benefit from such an enhanced solution. In particular, we give some examples that could be applied in such different domains as mobile communications or power systems in order to show the range of applicability.

**Location Services:** With the advent of mobile communications a huge marketplace has been created where stiff competition has caused mobile technology to improve rapidly. New services are constantly being introduced (e.g., short message service in *Global System for Mobile* (GSM)) to capture larger market shares.

In recent years it has become apparent that there is a large demand for mobile location services. The service could provide a range of functions, such as car navigation, fleet management, location charging (e.g., road pricing) or advertising and anti-theft devices. These services currently available use their own communication systems and radio frequency allocation — a pooled resource would be far more efficient and cost effective. In 1997 the U.S. Federal Communications Commission introduced a mandate to enforce all mobile

telephone networks to provide mobile locations for emergency services [13]. This mandate requires that cellular, personal communication services and specialized mobile radio service providers deploy a means of automatically locating emergency callers to within 125 m in 67 % of all measurements by October 31, 2001.

Unfortunately, there are a number of challenges to overcome to implement such a service. The accuracy of such a service is probably not as great as GPS, the satellite based location system — *differential-GPS* is accurate to some few meters. However, the mobile solution would be inexpensive by comparison. It does not require a direct line of sight communication and can penetrate buildings. It would, therefore, be aimed at a different market. The third generation mobile standard, *Universal Mobile Telecommunications System* (UMTS), has recently been developed by the European Telecommunications Standard Institute. There is currently much research and development being carried out with the collaboration of major mobile communications companies. In this way UMTS networks are designed with location estimation services in mind.

There are several methods that can be used to calculate an unknown mobile position from measurements based on signals from base stations of known position, see [84], [115] and [83] for an overview. These proposed location technologies fall into two broad categories: Network-based solutions and handset-based solutions.

Network-based Location Services:

- The *Signal Strength Analysis* works by measuring the signal strength of the mobile station at at least three base stations. This measurement is then directly related to the separation distances between the mobile and the base stations. The conversion from signal strength to distances and fading problems need to be overcome here in order to provide the required accuracies.

- The *Angle of Arrival* (AOA) technique relates the absolute angle of arrival of the signal of the mobile station at two or three base stations. This technique relies on antenna arrays which provide the direction finding capability to the receiver. This method has some impracticalities due to the size, alignment and array separation problems of the antenna array. Field trials in London, see [76], revealed some problems due to the achievable accuracy.

- The *Time of Arrival* (TOA) Technique is enforced by bouncing a signal back between the mobile and the base station in either direction. With the knowledge of the propagation time and the measurement of three such data sets to different base stations one can easily triangulate the mobile position. The required duplex signal transmission is one major drawback of this approach.

- *Time Difference of Arrival* (TDOA) measures the relative arrival time of the signal from the mobile at three base stations. Precise clock synchronization of the base stations will be required for this method.

Some of these network-based solution can be applied in the reverse direction for handsetbased methods as well, but due to size and reasons of practicality, only a modified scheme of TDOA is considered.

Handset-based Location Services:

• *GPS* chip-sets integrated into a mobile allow for direct location estimation in the range of 5 to 40 m accuracy since the US government removed the Selective

Availability mask in May 2000. The latter was used in the past to reduce the location estimation accuracy. In general, GPS now is the most popular radio navigation aide and has overtaken virtually all other forms of radio navigation because of its high accuracy, world wide availability, and low cost. Problems that need to be overcome with GPS handset-based solutions are the relative long time to first fix, and the requirement for a clear view of the sky.

- Network *Assisted GPS* uses fixed GPS receivers that are placed at regular intervals to fetch data that can complement the readings of the mobile GPS receiver. The assistance data makes it possible for the receiver to make timing measurements from the satellites without having to decode the actual messages and thus reduces greatly the time needed for a GPS receiver at the mobile to calculate the location. This solution reduces the time to first fix, the problem of the above solution but the requirement for a clear view of the sky is still pertinent, especially in urban locations.

- Enhanced Observed Time Difference (E-OTD) in GSM and Idle Period Downlink (IP-DL) in UMTS are TDOA variants for handset-based solutions. Here the mobile listens to bursts from multiple base stations and measures the time difference. These measurements are used to triangulate the actual mobile location. This requires that the base station positions are known and that the data sent from different sites is synchronized. The most common way of synchronizing the base stations is via the use of fixed GPS receivers. The calculation can then either be done in the mobile or at dedicated network nodes. The accuracy based on the achievable time synchronization is expected to be below 125 m, and unlike GPS these methods are not reliant on a clear view of the sky.

Hybrid techniques using more than one of the above techniques have been suggested in order to improve the location estimate accuracy. Currently TDOA variants are considered the leading candidates for any future location system. The precise synchronization of the base stations therefore will be provided with the help of GPS, since there seems to be no other solution at hand that can provide the required precision. In fact, the clock synchronization approach laid out in this thesis could be a promising alternative candidate to provide tight synchronization since the network infrastructure between the base stations is already present. A combination of both systems would very well complement each other and avoid spurious problems infrequently encountered with some GPS receivers, see [29].

**Fault location in Power Grids:** Another field of application is power distribution systems. Tight clock synchronization could be used to provide means for on-line fault detection and and estimation of the fault location [47]. Reliable provision of electrical power is of utmost importance for our daily human life. This in turn requires redundant, reliable power system components that can be easily maintained and exchanged, see [60]. Disregard of these criteria can have catastrophic consequences, as they were experienced after recent

power outages in the  $US^1$ , in Europe<sup>2</sup> and in New-Zealand<sup>3</sup>. Due to recent deregulations within the energy sector and poor environmental acceptance an improvement of reliability with the help of building-up additional power lines or other power system components is limited. A practical approach to improving the quality of power supply provision is to reduce the time between fault occurrence and resumption of operation. In case of an interruption the following steps need to be undertaken:

- 1. fast and reliable fault detection

- 2. selective switch-off of defect power system components

- 3. exact fault location

- 4. repair of defect power system components and resumption of operation

Fault-detection and selective switch-off are currently ensured with the help of present distance protection techniques. For fault location on-line and off-line methods are used where only current off-line methods provide exact location accuracy, especially when underground cables are considered.

On-Line fault location techniques:

- Methods relying on measurement of impedances are currently built-in into existing distance protection relays and provide a coarse estimation of the fault location. This information satisfies the needs for a selective switch-off of defect power system components immediately after the occurrence of a fault. The achievable precision for pin-pointing the fault location is in the range of 3 to 10 %, see [54], or [7], and is therefore insufficient for an exact fault location, especially when underground power cables are affected.

- Some other methods are based on travelling waves theory. A fault location technique that uses the propagation delays of the first wave that is emanated after a surge is affecting the cable is presented in [42]. They measure the time of arrival of this wave at both ends of the cable and calculate the fault location using the a priori known cable length. Field tests in Tokio revealed a location error within 1 % of the cable length. This method requires additional measurement cabling from both ends fed together in order to relate the time of arrival of the wave at both ends.

- A refinement of this method is proposed in [80] that uses measurement data at one terminal alone. The arrival time of the first wave and those of succeeding reflections are used to estimate the fault location. With the help of simulation a fault location in the range of 3 to 5 % was estimated.

<sup>&</sup>lt;sup>1</sup>A power outage during the months July till August 1996 affected millions of end customers in the south west of the United States and in northern Mexiko. More recently on Aug. 14<sup>th</sup> 2003 a power outage affected the entire north-east region of the United States and Canada including cities like New York City, Detroit, Ottawa and Toronto.

<sup>&</sup>lt;sup>2</sup>A power outage affected the end customers in Great Britain (Aug. 29, 2003) and a second one those in Italy (Sept. 28, 2003).

<sup>&</sup>lt;sup>3</sup>In February 1998 large districts of Auckland experienced a major power outage for several weeks after four central power cables broke down.

Off-Line fault location techniques:

Pulse methods, see [64] for an overview, are still generally used for fault location in underground cable systems when a fault is permanent. Depending on the kind of fault (high- or low-resistance, shunt or series fault, etc.) one of the following methods is usually selected:

- In the decay method, the voltage source has a high impedance in series with it and the voltage transient in the cable is measured. A high voltage is applied to the cable, inducing a breakdown at the fault. A transient is generated which travels back and forth between the fault site and the voltage source. The voltage transient is measured using a voltage-coupling device with a frequency response adequate to resolve both the edges and step portions of the voltage transient. The propagation of the transient is used to determine the fault location.

- In the current impulse method a surge generator applies a high-voltage step to the cable under test that induces a breakdown in the cable. The transient travels back and forth between the surge generator and the fault. The current transient is measured using a current transformer with a frequency response adequate to resolve only the edges of the current transient; this in turn is related to the fault distance, see [26].

- Time domain reflectometry takes advantage of the fact that impulses are reflected to some extent at cable discontinuities. When the impedance at the fault location approximates 0 or  $\infty$  a distinctive reflection will occur and thus allow for a good fault location. One flaw of this method is that high-impedance shunt faults are difficult to localize.

- Arc reflectometry enhances the time domain reflectometry method by temporarily converting a high-resistance fault into a short circuit. This is facilitated by applying a high-voltage surge to the cable that ignites an arc at the fault location. Time domain reflectometry is then used to determine the fault location.

- After the approximate position of the fault has been found using one of the above methods, some means of pinpointing the fault must be used. Common practice has been to apply repeated high-voltage surges to the cable and listen for the "thump". To date, this acoustic method is by far the most successful technique used to pinpoint the precise location of a fault. However, indiscriminate use of a surge generator can place sound insulation at risk.

The off-line fault location techniques make it possible to pinpoint cable faults to within a few meters. In order to accomplish this satisfying result the defect cable needs to be isolated from the power grid and a high voltage generator next to the measurement equipment must be connected.

In order to implement an on-line method that delivers exact fault location one could use a tight synchronized distributed system (c.f. [8] or [20]) combined with the proposed techniques in [80] and [42] in order to detect and timestamp the first wave emanated after a surge stresses a cable. This in turn would decrease the time required for fault location and could thus reduce the impacts impaired by harmful calamities.

A similar application domain is on-line monitoring of partial discharges emitted in the

cables of power distribution systems. Cavities in the isolation cause small surges that induce small travelling waves superimposed onto the supply voltage. As with faultlocation one could monitor these effects and deduce potential problems that may arise due to electrical stress or aging. This information in turn is useful for a maintenance schedule of the employed cabling. These and several other uses of synchronized clocks in power distribution systems have been proposed to increase the quality of service, see [28].

Although these are by now only some few practical applications that could benefit from a very tight clock synchronization, others in computer science and the area of measurement and instrumentation will eventually emerge when this enabling technology becomes widely available. In particular applications like multimedia, mobile computing or process control applications, e.g. in papermills, will benefit from this service.

### **1.3** Outline

This thesis is structured as follows:

Chapter 2 proposes a taxonomy adapted to several clock synchronization algorithms: deterministic and probabilistic, internal and external. This taxonomy makes it possible to classify existing clock synchronization algorithms according to their internal structure and several basic building blocks. The following analysis is used to identify the building blocks that require support by hardware in order to provide tighter synchronization. Furthermore, the key parameters are developed out of existing algorithms that will set the physical limits for the achievable tightness.

Chapter 3 differentiates related work under the prospect of these limiting parameters. We briefly illustrate the hardware support for clock synchronization as used in the MARS project and by our *Network Time Interface* (NTI) M-Module and depict the shortcomings of these approaches. Next we address clock synchronization as used in the time triggered architectures TTP and FlexRay. In these systems clock synchronization plays a fundamental role for future time-critical avionic and automotive systems. Finally, the new IEEE Standard 1588 is considered and analyzed under these terms.

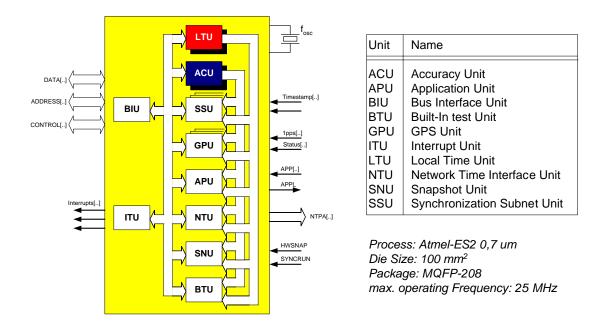

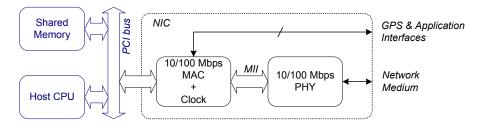

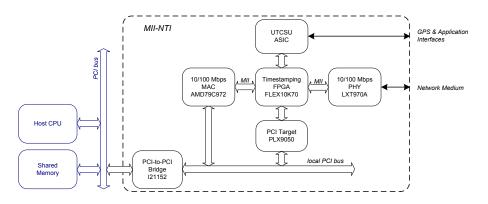

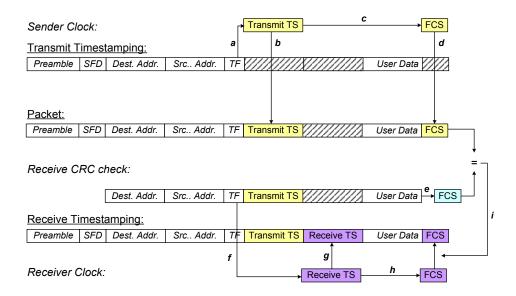

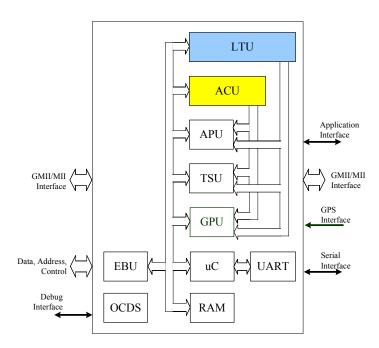

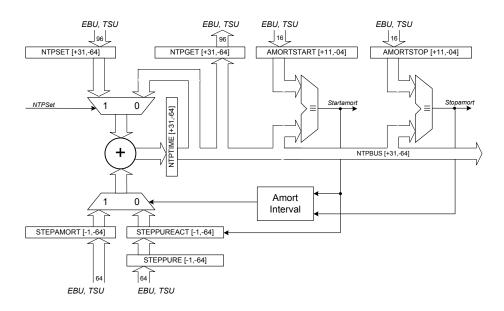

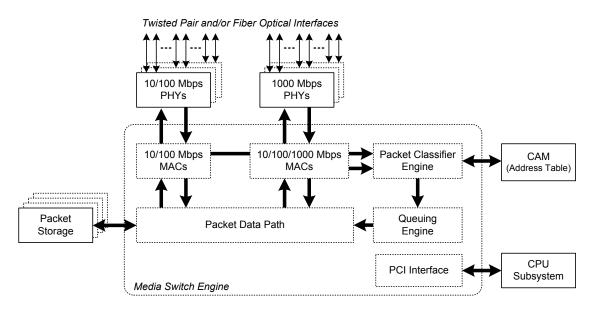

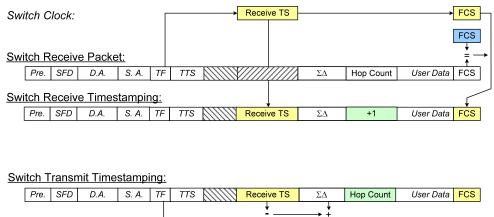

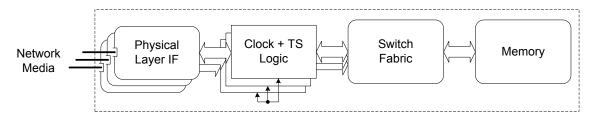

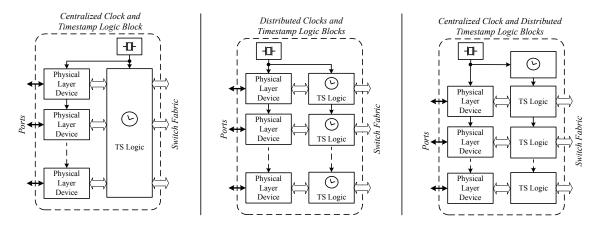

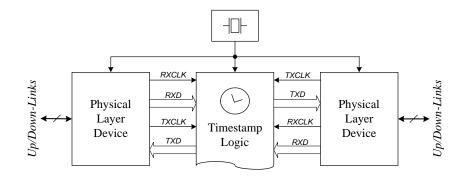

Chapter 4 introduces and discusses several hardware architectures to enable tight clock synchronization in modern popular switched Ethernet networks. In particular, network interfaces for end-systems and modifications of existing switch architectures are presented. The proposed approaches are analyzed under the prospects of how to achieve tight synchronization and how to keep modifications and influences on existing network hard+software low. Furthermore, this chapter briefly addresses enhancements for an integrated clock circuit, based on our UTCSU Asic, that is currently developed within the PSynUTC FIT-IT<sup>4</sup> project by the spin-off company Oregano Systems<sup>5</sup>.

Chapter 5 describes the measurement setup used for an experimental evaluation of the underlying parameters that limit the achievable clock precision. In particular, we address the jitter of the physical layer of switched Ethernet networks under various different end-to-end configurations. Next, we briefly illustrate the analysis process of the gathered measurement data before we finally present the results obtained from the conducted experiments.

A short summary concludes this thesis, providing directions for future related research

<sup>&</sup>lt;sup>4</sup>http://www.fit-it.at

<sup>&</sup>lt;sup>5</sup>http://www.oregano.at

issues. In particular, we give a summary of extensions to our approach in order to evolve an implementation that can lead to an industrial realization.

## State of the Art of Clock Synchronization

In centralized systems, mutual exclusion and inter task communication problems are generally solved using methods such as semaphores and monitors and highly rely on shared memory. This is not true for distributed systems where even the simplest thing such as determining whether event *A* happened before or after event *B* requires careful thought. In general, distributed systems have the following characteristics [72]:

- Multiple concurrent computation threads,

- interconnections for inter-thread communication and a

- global, shared state the individual computers cooperatively maintain.

To achieve a consistent global state it is necessary to address the issues of independent node failures and unreliable, insecure and costly communication. To that end, clock synchronization provides internal consistency of the clocks at the distributed nodes that eases the implementation of the before-mentioned issues. During the past few years, much research has been conducted towards a common view of time in fault-tolerant distributed systems. There are more than 60 papers listed in a 1993 bibliography [114] on clock synchronization in distributed systems. As a result, the proposed algorithms are relatively well understood. The increasing demand for ever tighter synchronization and some additional requirements, e.g., to synchronize with an external time standard, resulted in further research, see [86] for an overview.

This thesis proposes a mechanism for further enhancements of existing clock synchronization strategies. The presented approach exploits the limiting parameters of existing implementations. Therefore, a comparative study and an in-depth analysis of published algorithms seems appropriate.

Software clock synchronization algorithms use standard communication networks and send synchronization messages to get the clocks synchronized. They are more frequently used since a loose synchronization in the range of some *ms* is acceptable in most applications. All software clock synchronization algorithms proposed so far decompose themselves in *deterministic*, *probabilistic* and *statistical* algorithms. Deterministic algorithms, e.g. [78, 16, 24, 25, 27, 56, 63, 85, 87] assume an upper bound on transmission delays and guarantee a maximum difference between any two simultaneous clock readings. Probabilistic algorithms [2, 75, 18, 15, 78] guarantee a constant maximum deviation between synchronized clocks. In particular, a clock knows at anytime if it is synchronized or not with the other, but there is a non-zero probability that a clock will get out of synchronization when too many unmasked communication failures occur. Statistical algorithms

[113, 14, 58] assume that the expectation and standard deviation of the delay distributions are known. Clocks do not know how far apart they are from each others, but a statistical argument is made that at any time, any two clocks are within some constant maximum deviation with a certain probability.

Hybrid clock synchronization [53, 34] solutions based on software algorithms with moderate hardware support achieve reasonably tight synchronization and are still costeffective in comparison to pure hardware approaches. The embodied hardware support usually maintains the local clock, applies the required corrections and provides some facilities to ease the exchange of clock messages. The proposed clock synchronization method fits into this hybrid category and extends related work by providing a new way of incorporating clock messages into state-of-the-art network solutions.

Pure hardware-based clock synchronization [99, 106, 12] achieves very tight synchronization through the use of special synchronization hardware at each processor, and uses a separate network solely for clock signals. Due to cost, size and practicality reasons the additional network is in most cases only affordable when the system spread is within the range of a few meters. The primary application domain of this kind of synchronization strategy are parallel systems where a set of microprocessors needs to coordinate their actions. This thesis does not consider these specialized, costly mechanisms, instead it concentrates and exploits mechanisms of software based and hybrid clock synchronization.

The remainder of this chapter provides a classification and analysis of published clock synchronization algorithms. The aim herein is to devise a good understanding of the principles involved in order to extract the relevant parameters one needs to tackle to achieve tight synchronization. Similar surveys, but with a more general focus in mind, can be found in [93, 82, 100] and [1]. In [82], software and hardware clock synchronization algorithms are classified with regard to the clock correction scheme used. In contrast, the algorithms surveyed in [100] are listed according to the supported faults and the system synchrony (knowledge of upper bounds on communication latencies). A very thorough classification is given in [1] that aims to help the designer in choosing the most appropriate structure of algorithm and the best building blocks suited to his/her hardware architecture, failure model, quality of synchronized clocks and message cost induced.

A short section on system modelling defines relevant parameters and properties as used in most relevant papers on this topic. The following taxonomy tries to figure out the delimiting parameters for an achievable clock synchronization tightness. The results of this analysis are used to identify requirements and improvements for hardware support for tight clock synchronization.

## 2.1 System Modelling

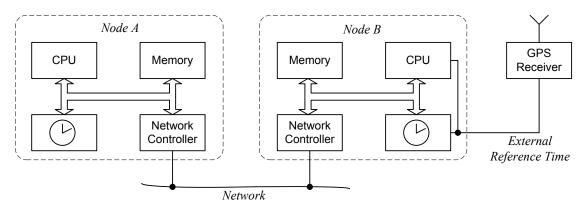

A comparative study of the impaired parameters of clock synchronization algorithms requires establishing a general system model. According to the analyzed algorithms we consider a set of distributed nodes interconnected by a communication network that can have different characteristics (broadcast or point-to-point, fully-connected or not). Every node hosts a *Central Processing Unit*, some kind of *Communications Controller*, a storage device in the form of a local memory and a local clock. In order to allow for a synchronization with real-time some nodes should be equipped with GPS (Global Positioning System) or other reference timing receivers in order to obtain the time signal broadcast by a standard source of time, as UTC (Universal Time Coordinated) the official time standard.

#### 2.1.1 Clocks and Processors

For an arbitrary node p, clock  $C_p$  generally consists of an oscillator  $O_p$  and a counting register that is incremented by the ticks of the oscillator. While clocks are discrete, having, non-zero granularity G, all algorithms assume that clocks run continuously, i.e.,  $C_p$  is assumed to be a monotonic real-valued function of real-time t.

**Clock Precision:** The paramount problem of distributed clock synchronization is to maintain the maximum clock state deviation between any two clocks at different correct nodes p and q at all real-times bounded by a value called *precision*  $\pi$

$$|C_p(t) - C_q(t)| \le \pi \quad \forall t \in T.$$

This problem referred to as *internal clock state synchronization* is usually at the core of all clock synchronization algorithms.

Accuracy: Synchronizing the clock  $C_p$  of one arbitrary node p of a distributed system with an external time standard, e.g. UTC, is denoted *external clock state synchronization*. It keeps the maximum deviation between corresponding clock states and real-times on a single correct clock bounded by a constant called *accuracy*  $\alpha$

$$|C_p(t)-t| \leq \alpha_p \quad \forall t \in T.$$

Accuracy becomes essential when the spatial diameter of the distributed system is very large or when the system needs to interact with other systems respectively. In both cases a common notion of time that is synchronized closely to the official time standard becomes crucial.

**Clock Drift:** It is commonly assumed that even correct oscillators exhibit some instabilities due to temperature changes, aging and other reasons. In general, the *oscillator drift*  $\rho$  is the systematic change in frequency with time of an oscillator. The manufacturer usually specifies a maximum  $\rho$  and hence bounds the instantaneous oscillator frequency f(t) by

$$(1-\rho) \le \frac{f(t)}{f} \le (1+\rho)$$

Direct coupling of an oscillator with the clock yields a clock rate of Sf(t) where the coupling factor S is the constant 1/f, i.e.  $C_p(t) = \frac{1}{f} \int_{0}^{t} f(t) dt$ . The maximum deviation between the clock rate and the ideal rate 1 is denoted by the *clock drift*  $\rho_p$ , formally

$$\left|\frac{dC_p(t)}{dt}-1\right| \leq \rho_p \quad \forall t \in T.$$

Thus a perfect clock has dC/dt = 1, a fast clock dC/dt > 1 and a slow clock dC/dt < 1. If two clocks are drifting in opposite direction, at a time  $\Delta t$  after they were synchronized, they may be as much as  $2\rho\Delta t$  apart. Thus, in order to guarantee that no two clocks ever differ by more than  $\Delta t$ , clocks must be synchronized at least every  $\Delta t/2\rho$  seconds.

**Consonance:** The maximum clock rate deviation between two different correct clocks in the distributed system at simultaneous real times is called *consonance*  $\gamma$  [95, 96], formally

$$\left|\frac{dC_p(t)}{dt} - \frac{dC_q(t)}{dt}\right| \le \gamma \quad \forall t \in T.$$

Maintaining consonance resp. drift of an ensemble of clocks refers to the problem of *external* resp. *internal clock rate synchronization* [96].

**Initial synchronization:** A sometimes neglected aspect is the problem of system start-up and node join and how initial synchronization is accomplished respectively. An assumption made by several algorithms makes it necessary that the nodes clocks are initially synchronized and that this initial synchronization is bounded by a given constant  $\beta$ , see [63] for example.

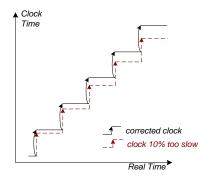

The clock synchronization algorithm executes on the local processor and takes the clock readings of the local and remote clocks as inputs. The required computation time should be small and bounded by some constant value in order to account for clock state and rate changes during this time span. The computed correction is afterwards applied to correct the local clock time. Most systems are equipped with a pure oscillator+counter based clock where synchronization of the local hardware clock is not possible at all. Rather, logical clocks are introduced. The value of a logical clock at real-time t is determined by adding an adjustment term to the local hardware clock  $C_p(t)$ . The adjustment term can be either a discrete value, changed at each re-synchronization [92, 101], or a linear function of time [92, 15, 91]. The discrete clock adjustment technique may cause a logical clock to instantaneously leap forward or be set back, and then continue to run at the speed of its underlying hardware clock. Such behavior cannot be tolerated by most distributed applications requiring clock synchronization, therefore a linear function of time for clock adjustment is often mandatory.

#### 2.1.2 Communication Subsystem

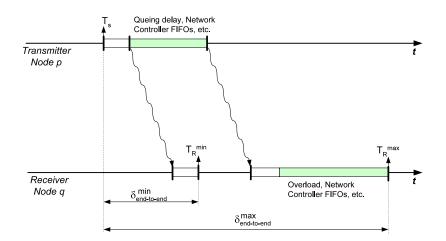

In distributed real-time systems, message delays may be more or less predictable depending on the type of network used and the assumptions made on the network load. Some algorithms assume that known lower and upper bounds to deliver (i.e. to send, transport and receive) a message between correct nodes exist. The mechanism to send, transport, and receive any message over a correct link from a correct node p to node q experiences a delay  $\Delta t'_{p,q}$  subject to the delay condition

$$\triangle t_{p,q} - \varepsilon_{p,q} \le \triangle t'_{p,q} \le \triangle t_{p,q} + \varepsilon_{p,q}$$

where  $\triangle t_{p,q}$  represents the deterministic part and  $\varepsilon_{p,q}$  the delivery uncertainty with  $\triangle t_{p,q} \ge \varepsilon_{p,q}$ . When this assumption holds, a deterministic clock synchronization algorithm can ensure that all correct logical clocks are within a maximum distance from each other.

In practice from the mechanisms involved in present communication subsystems one main limiting factor for clock precision and accuracy is  $\varepsilon$ . In fact, the work of [62] revealed that even *n* ideal clocks cannot be synchronized with a worst case precision less than

$$\varepsilon(1-\frac{1}{n})\tag{2.1}$$

in presence of a delivery uncertainty  $\varepsilon$ . Unfortunately, in a shared channel type network there are several steps involved in packet transmission/reception that could contribute to  $\varepsilon$ ,

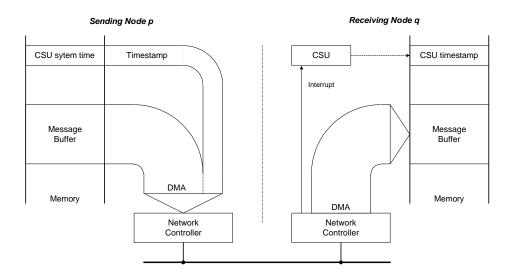

cf. [53] and [34, 89]. The following general steps illustrate a usual message transfer from node p to node q:

- (1) The CPU at node p assembles the packet (including a local timestamp) and notifies the Communication Subsystem.

- (2) The Communication Subsystem at node p in turn acquires the network medium and sends the resulting bit-stream.

- (3) The receiving communications module at node q pulls the bit-stream from the medium and notifies the CPU at node q via interrupt of the current packet reception.

- (4) The CPU at node *q* processes the received packet and marks the reception time by reading its local clock.

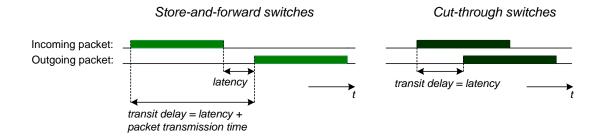

Although this scenario is by far idealized, it becomes apparent that  $\varepsilon$  is affected by several sources of indeterminism. The medium access uncertainty at (2) strongly depends on the access policy of the used bus system. The network delay  $(2 \rightarrow 3)$  may vary due to queuing delays at intermediate gateway nodes. The reception interrupt latency until the CPU processes the packet  $(3 \rightarrow 4)$  strongly depends on the CPU load.

#### 2.1.3 Faults

For development and analysis of distributed algorithms faults need to be considered since they may affect every single component (processor, communication links, clocks, etc.) of the system. A proper fault model  $\mathcal{F}$  needs to be specified in order to elaborate on system operating conditions when faults occur. Following is a list of types of processor, link and clock failures that have mostly been assumed throughout clock synchronization algorithms.

Concerning <u>clocks</u>, most of the algorithms assume uncontrolled failures (also called Byzantine or arbitrary failures). Other ones assume timing failures, a more restricted failure mode prohibiting conflicting information.

- **Clock Byzantine failure:** A local hardware clock commits a Byzantine failure when it gives inaccurate, untimely or conflicting information. This includes dual-faced clocks, which may give different values of time to different processors at the same real-time.

- **Clock timing failure:** A local hardware clock commits a timing failure if it does not meet the clock drift condition, i.e., is not p-bounded.

The failure semantics of processors assumed in published algorithms cover nearly all the kinds of failures ever identified. Processors may crash, commit performance failures, or more generally, commit Byzantine failures.

- **Processor crash failure:** A processor commits a crash failure if it behaves correctly and then stops executing forever (permanent failure).

- **Processor performance failure:** A processor commits a performance failure if it completes a step in more than the specified time.

**Processor Byzantine failure:** A processor commits a Byzantine failure if it returns incorrect or malicious data, see [57].

With regard to the <u>communications subsystem</u>, whatever its type (broadcast or point-topoint), the failure semantics are more restricted. A link may commit omission or performance failures but must never partition the network.

- **Link omission failure:** A link from a node p to a node q commits an omission failure on a message if the message is inserted into p's outgoing buffer but the link does not transport it into q's incoming buffer.

- **Link performance failure:** A link commits a performance failure if it transports some message in more time than specified. Clearly, this applies only to systems with known upper and lower bounds on transmission delays.

## 2.2 A taxonomy of clock synchronization algorithms

Having defined several parameters required for system modelling, this section is devoted to identifing common building blocks of clock synchronization algorithms. The proposed taxonomy relies on two orthogonal features: the internal structure and the basic building blocks from which most clock algorithms are built and thus follows and extends the presentation given in [1]. The internal structure represents the way synchronization messages are distributed and the role certain nodes play in synchronization. The building blocks correspond to successive steps executed by every clock synchronization algorithm and are kept generic in the sense that they apply to several different kinds of algorithms — deterministic, probabilistic and statistical; internal and external.

#### 2.2.1 Structure of clock synchronization algorithms

The structure of clock synchronization algorithms is discerned by the way how time is disseminated and how every node participates in the clock synchronization.

#### Asymmetric (Master-Slave) Structures

Throughout the internet time-servers are deployed and client nodes may synchronize to the time provided by these servers using the *Network Time Protocol*. A similar *master-slave* structure is employed by other synchronization strategies as described in [27, 15, 2] and may be classified as an *asymmetric* scheme. Usually one dedicated node is designed as master and provides the time to the other nodes designed as slaves. In some implementations, denoted as master-controlled schemes, the master acts as coordinator of the clock synchronization algorithm. It requests and collects the slaves clocks, estimates the required adjustments and sends back the corrected clock values. On the other hand, in slave-controlled schemes, the master provides only the reference time. Every slave asks for the reference time and after reception invokes the clock synchronization algorithm and re-synchronizes the local clock. The advantage of asymmetric schemes is their low cost in terms of number of messages exchanged. On the other hand, the most common drawback is given by the presence of the master, which represents a single point of failure. In addition, a single master can be swamped by a large numbers of synchronization messages, thus invalidating in some way communication delay assumptions. To overcome this

problem some extra mechanisms such as fault detection followed by the election of a new master, or duplication of masters are required.

#### **Symmetric Structures**

In symmetric schemes every node that participates in an active manner, executes the whole clock synchronization algorithm. Therefore every node disseminates its local clock value to all other nodes and, in turn, gathers the clock value from them. The received clock values in relation to the local clock are then used to compute a correction value. This adjustment term is afterwards applied to the local clock. Symmetric algorithms can be split in two classes, flooding-based and ring-based, depending on the virtual path taken for transmitting a message from one processor to every other one. In flooding-based symmetric algorithms (see e.g. [108, 16, 101, 63, 79]), each processor sends its messages to all outgoing links. Messages received on incoming links are relayed when a non-fully-connected network is used. The benefit of flooding-based techniques is their natural support for fault tolerance, i.e., they do not exhibit a single point of failure. However, they may require up to  $n^2$  messages to disseminate a message to all nodes in the system, with n being the number of nodes in the system. This large number of messages can be lowered to n if a broadcast network is used. The virtual ring scheme was designed in order to decrease the number of exchanged messages experienced in the flooding-based schemes, cf. [74]. In the ring scheme, all the processors in the system are gathered along a virtual ring. The number of messages is reduced by sending only one message along this cyclic path. As this message travels on the ring, each processor adds its own data to the message. Compared with flooding-based schemes, virtual ring schemes need a smaller number of message exchanges (only n messages per re-synchronization are used), but need extensions in order to support node failures.

#### **Hierarchical Structures**

Some clock synchronization algorithms consider a *hierarchical* clock synchronization strategy where the synchronization is spread at different levels. The operation at one distinct level may again be categorized either as asymmetric or symmetric. In addition, nodes may participate in the clock synchronization in a different manner. Passive nodes may synchronize their clocks but may not contribute to the overall synchronization in contrast to active nodes that will provide their time for other nodes as well. Primary nodes are either equipped with a better oscillator or may have access to an external time-source, e.g., a GPS receiver in contrast to secondary nodes. In general, not all clock synchronization algorithms impose a structure. This way they can be employed in both either asymmetric or symmetric schemes.

#### 2.2.2 Clock synchronization building blocks

Clock synchronization in a distributed system is composed of several fundamental building blocks:

- Re-Synchronization event detection

- Remote clock estimation technique

- Clock correction block

#### **Re-Synchronization event detection block**

A clock synchronization algorithm has to detect the instant at which it must resynchronize. Due to clock drift, clocks must be re-synchronized frequently to guarantee precision  $\pi$  and accuracy  $\alpha$ . Usually clock synchronization algorithms are roundbased, each round being devoted to the re-synchronization of all clocks. Thus this resynchronization event detection block becomes active periodically. The difficulty arises when dealing with the time at which rounds must start. One technique assumes initially approximately β-synchronized clocks, see e.g. [63, 56, 79, 91]. Some external means are usually required to provide this initial condition. Ensuring this setting a node considers the start of a new round k when its local clock reaches kP, where P is the round duration in local time, i.e., the time between two successive re-synchronization rounds. Intuitively, to keep clocks as closely synchronized as possible,  $\beta$  and P must be as small as possible. However, P cannot be arbitrarily small in order for any algorithm to work correctly, cf. [63] or [91]. Another technique uses message exchanges to invoke a synchronization round, see [101, 108] for examples. A node sends a message to all other nodes when its local clock reaches a predefined value. It starts a new synchronization round upon reception of a fixed number of such messages originating from other nodes. The number of expected messages depends on the maximum number of failures assumed. The message latencies thus directly influence the achievable precision, since rounds are triggered on message reception. By using broadcast networks, exhibiting a small variance of transmission delays, precision can be improved [108].

#### **Remote clock estimation technique**

When a new clock synchronization round initializes, every node tries to get some knowledge of the value of remote clocks. Due to variable communication delays and clock drifts only estimates can be acquired. It is essential for any clock synchronization strategy, that these estimates are closely related to the remote clock values since the clock readings form the input for the subsequent clock correction block. The *remote clock estimation technique* operates as follows: Each node sends its local clock value *T* encapsulated within a message to every other node. The receiving node uses the message contained therein to estimate the clock of the sender. This is possible when communication delays are bounded and clocks are initially synchronized. The receiver feeds the remote clock values and the corresponding local times at which messages are received to the clock correction block. Only clock messages received within an interval of length  $(1 + \rho)(\Delta t_{p,q} + \varepsilon_{p,q} + \beta)$  following the most recent re-synchronization event are considered. The value of the remote clock at node *q* belongs to the interval

$$[T + (1 - \rho)(\triangle t_{p,q} - \varepsilon_{p,q} - \beta), T + (1 + \rho)(\triangle t_{p,q} + \varepsilon_{p,q} + \beta)]$$

seen at node p, cf. [63]. When ignoring smaller order terms, the maximum difference of two remote estimates of different nodes when communication delays are bounded is given by

$$2(\varepsilon_{p,q}+\beta+\rho \triangle t_{p,q}).$$

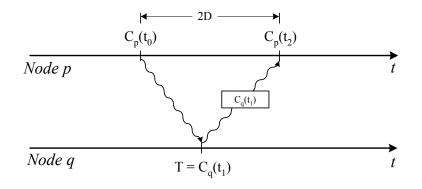

In the case where communication delays are not bounded and clocks are not initially synchronized a set of successive transmissions of timestamped synchronization messages are at hand. The clock correction block uses message delay statistics (expectation and deviation of transmission delays) for computation of a correction term. A remote clock estimation mechanism that can be used in the absence of an upper bound on communication delays has been introduced in [15]. Cristian's master-slave algorithm is based on a remote clock reading technique that allows estimating a remote clock to lie within a given interval and is used to achieve external clock synchronization. In order to obtain a remote clock reading from some node q a process p sends a

Figure 2.1: Remote Clock Reading

requesting message to node q at  $C_p(t_0)$  querying q's time. The remote node replies with a message that encapsulates its clock value  $T = C_q(t_1)$ . This message, in turn, is received at node p at its own local time  $C_p(t_2)$ . With the knowledge of the round trip delay 2D node p can estimate q's clock and bound the error it makes when reading q's clock. Since p's clock can drift from real-time by at most  $\rho$ , the round trip delay is not greater than  $(C_p(t_2) - C_p(t_0))(1 + \rho) = 2D(1 + \rho)$ . The one-way transmission delay for the reply message may hence be defined by a constant  $max := 2D(1+\rho) - min$  where  $min = \Delta t_{p,q} - \varepsilon_{p,q}$ accounts for the minimum transmission delay. These two bounds can now be used to approximate q's clock at time  $C_p(t_2)$  since q's clock value increases by  $min(1 - \rho)$  at the least and by  $max(1 + \rho)$  at the most, respectively. Hence q's clock value T estimated at node p at  $C_p(t_2)$  lies in the interval:

$$C_a^p(t_2) \in [T + min(1-\rho), T + max(1+\rho)]$$

Since node *p* has no means of knowing exactly where the clock of node *q* lies within the above interval it estimates the value with a function  $C_q^p(T,D)$  that for e.g. chooses the midpoint of this interval. The inherent maximum error made therein is given by

$$2D(1+\rho)^2 - 2(\triangle t_{p,q} - \varepsilon_{p,q}) \sim 2D(1+2\rho) - 2(\triangle t_{p,q} - \varepsilon_{p,q}).$$

If node p wants to achieve a reading error smaller than a certain specified maximum error, it must discard any reading attempt for which it measures an actual round trip delay 2D > 2U with 2U denoting the *timeout delay* necessary for achieving the required reading precision.

#### **Clock correction block**

The local and remote clock readings serve as input to a suitable clock correction algorithm. The latter calculates clock correction terms that are applied succinctly to the clocks. Algorithms presented in scientific literature can be categorized into several categories:

- **Clock State Correction:** A clock at every node maintains local time and hence allows us to tell when a particular event occurs or how long a duration takes. Most clock synchronization algorithms in general, and clock correction functions in particular, aim at keeping clock states together as well as the deviation towards real-time bounded. Viewed under this aspect most algorithms presented in scientific literature can be categorized into

- internal

- and internal and external clock synchronization.

Further categorization is due to the implementation of the clock correction algorithm as

- deterministic,

- probabilistic and

- statistical.

- **Clock Rate Correction:** Clock synchronization can be viewed either in terms of clock speeds or by considering the instantaneous clock rate v(t) = dC(t)/dt. The goals here are to keep the deviation between the clock rate and the ideal rate 1 and the clock rates between two different nodes at simultaneous real-times bounded.

The remainder of this subsection informally describes the principles of a selected set of clock synchronization algorithms and lists the precision and accuracy they achieve<sup>1</sup>. The aim herein is to give a short introduction and to allow extraction of a set of parameters that need improvements through appropriate hardware support.

#### **Deterministic clock synchronization:**

Most clock correction blocks implemented in round based algorithms use the notion of a *convergence function* (CV) introduced in [94]. These algorithms can be generically described as follows: At the end of a synchronization round every process reads the clocks of all processes and then adjusts its clock value for the next round by applying a convergence function to the clock readings of the current round. A synchronization algorithm that can be obtained from the above generic algorithm by instantiating some concrete function for the abstract notion of a convergence function will be termed a *convergence function based algorithm*. Convergence functions use the set of remote clock estimates to compute a new clock value. For this, special averaging techniques are at hand; in addition, they usually provide a mechanism for tolerating erroneous clock readings as well. The most prominent and promising convergence functions are briefly listed below along with a short informal description.

#### CV-functions for internal clock synchronization:

• In the interactive convergence algorithm, see [56], each process reads the value of every process's clock and sets its own clock to the average of these values — except when it reads a clock value differing from its own by more than  $\Delta \approx \pi + \varepsilon$ ,

<sup>&</sup>lt;sup>1</sup>The symbols and notation used for several parameters follows the definitions given in Sec. 2.1 rather than those of the literature, to ease comparisons and reasoning.

then it replaces that value by its own clock's value when forming the average. The achievable worst case precision of this algorithm is given by:

$$max(\frac{n}{n-3m}(2\varepsilon + \rho(P+2\frac{(n-m)S}{n})), \beta + \rho P)$$

with S denoting the final seconds of the interval P, n being the total number of processes and m the number of faulty ones.

• The master-slave clock synchronization implemented in TEMPO, the distributed service that synchronizes the clocks of Berkeley UNIX 4.3 BSD, is described in [27]. A master time daemon measures the time difference between the clock of the machine on which it runs as well as those of all other machines. The master computes the network time as the average of the times provided by non-faulty clocks. A clock is considered faulty if its value is more than a small specified interval away from the values of the clocks of the majority of the other machines. The master then sends to all slave time demons —also to those with faulty clocks— the correction that should be performed on the clock of its machine. Since the correction can be negative, in order to preserve the monotonicity, TEMPO implements the correction by slowing down (or speeding up) the clock rates.

When the master time demon synchronizes every P seconds all non-faulty clocks are within range:

$$4(D-2min(T_{pa}^{min},T_{ap}^{min}))+2\rho P$$

with  $T_{pq}^{min}$  and  $T_{qp}^{min}$  denoting the minimal possible transmission times from nodes p to q and from q to p respectively.

The *fault-tolerant midpoint function* proposed in [63] synchronizes an ensemble of 3F + 1 nodes where at most F of these are faulty. The algorithm executes in a series of rounds; each round is started when a clock reaches a certain predefined value. Meanwhile, for a bounded amount of time, it collects clock messages from all other nodes. Then every node invokes the fault tolerant midpoint function that returns the midpoint of the range of clock values received from all other nodes after the f highest and f lowest values have been discarded: FTM(p,θ) := mid(sort(θ)(F), sort(θ)(N - F - 1)). An analysis of the algorithm presented in [24] shows that the maximum deviation between correct clocks is 4.5Λ + 4ρr<sub>max</sub> considering initial synchrony, with 2Λ accounting for the clock reading error, ρ the clock drift and r<sub>max</sub> the maximum (real-time) duration of a round.