# Diffusion Barrier Cladding in Si/SiGe Resonant Interband Tunneling Diodes and Their Patterned Growth on PMOS Source/Drain Regions

Niu Jin, Sung-Yong Chung, Anthony T. Rice, Student Member, IEEE, Paul R. Berger, Senior Member, IEEE, Phillip E. Thompson, Senior Member, IEEE, Cristian Rivas, Roger Lake, Senior Member, IEEE, Stephen Sudirgo, Student Member, IEEE, Jeremy J. Kempisty, Branislav Curanovic, Student Member, IEEE, Sean L. Rommel, Member, IEEE, Karl D. Hirschman, Member, IEEE, Santosh K. Kurinec, Senior Member, IEEE, Peter H. Chi, and David S. Simons

Abstract—Si/SiGe resonant interband tunnel diodes (RITDs) employing  $\delta$ -doping spikes that demonstrate negative differential resistance (NDR) at room temperature are presented. Efforts have focused on improving the tunnel diode peak-to-valley current ratio (PVCR) figure-of-merit, as well as addressing issues of manufacturability and CMOS integration. Thin SiGe layers sandwiching the B  $\delta$ -doping spike used to suppress B out-diffusion are discussed. A room-temperature PVCR of 3.6 was measured with a peak current density of 0.3 kA/cm<sup>2</sup>. Results clearly show that by introducing SiGe layers to clad the B  $\delta$ -doping layer, B diffusion is suppressed during post-growth annealing, which raises the thermal budget. A higher RTA temperature appears to be more effective in reducing defects and results in a lower valley current and higher PVCR. RITDs grown by selective area molecular beam epitaxy (MBE) have been realized inside of low-temperature oxide openings, with performance comparable with RITDs grown on bulk substrates.

Index Terms—CMOS compatibilty, dopant diffusion, Ge-Si alloys, low-temperature oxide, molecular beam epitaxy, negative differential resistance, patterned growth, rapid thermal annealing, resonant interband tunneling diodes, silicon.

# I. INTRODUCTION

Since the development of the Esaki diode in 1958 based on interband tunneling [1], the tunnel diode has been an additional option for the circuit designer, with its unusual negative differential resistance (NDR) property. Its folded current–voltage (I-V) characteristic facilitates such circuit elements as simple latches by the serial connection of two

Manuscript received August 29, 2002; revised April 25, 2003. This work at Ohio State was supported by the national Science Foundation under Grants ECS-0196208 and ECS-0196054. The work at NRL was supported by the Office of Naval Research. The review of this paper was arranged by Editor G. Snider.

- N. Jin, S.-Y. Chung, and A. T. Rice are with the Department of Electrical Engineering, The Ohio State University, Columbus, OH 43210 USA.

- P. R. Berger is with the Department of Electrical Engineering and the Department of Physics, The Ohio State University, Smith Laboratory, Columbus, OH 43210 USA (e-mail: pberger@ieee.org).

- P. E. Thompson is with the Naval Research Laboratory, Washington, DC 20375-5347 USA.

- C. Rivas and R. Lake are with the University of California, Riverside, CA 92521-0425 USA.

- S. Sudirgo, J. J. Kempisty, B. Curanovic, S. L. Rommel, K. D. Hirschman, and S. K. Kurinec are with Microelectronic Engineering, Rochester Institute of Technology, Rochester, NY 14623 USA.

- P. H. Chi and D. S. Simons are with the National Institute of Standards and Technology, Gaithersburg, MD 20899 USA.

Digital Object Identifier 10.1109/TED.2003.815375

tunnel diodes [2]. Furthermore, the tunneling phenomenon is a majority carrier effect and is not governed by conventional transit time effects, but due to a lack of robust manufacturing techniques and compatibility with Si CMOS processing, the discrete Esaki tunnel diode has become relegated to niche applications, such as local oscillators and frequency locking circuits.

The development of the resonant tunneling diode (RTD) in 1974 based upon intraband tunneling using double barriers [3] provided an alternative pathway, using electron confinement within the conduction band through bandgap engineering, by harnessing advancements in epitaxial growth techniques in the late 1960s and early 1970s. This approach works well for the III–V compound semiconductor material systems, where significant conduction band offsets are possible.

The union of tunnel diodes and transistors into monolithic circuits has demonstrated new circuit architectures that i) reduce component count, ii) speed circuit switching, and iii) reduce power consumption. The end result is more computational power per unit area than a transistor-only circuit topology. Some circuit examples that have been demonstrated using III–V RTDs are ultra-low power refresh-free tunnel diode SRAM circuits [4] and compact A/D converters [5]. This approach will become increasingly attractive to the CMOS community if a viable Si-based tunnel diode can be added in a simple manner after the high-temperature CMOS steps were concluded [6]. Adding an Si-based tunnel diode is viewed as one potential avenue by the CMOS community to extend the technology roadmap [7], [8].

Until recently, a viable Si-based tunnel diode for integration with CMOS has eluded investigation. Some of the first attempts explored Si-based RTDs. For intraband tunneling, the natural heterojunction system is Si/SiGe, but due to a small conduction band offset between Si and Ge, the achievable electron confinement reported is below 150 meV with the use of thick relaxed SiGe buffer layers to engineer the strain energy to place the Si wells and Si barriers under compressive strain. Initial reports on Si-based RTD's demonstrated a peak-to-valley current ratio (PVCR) of 1.2 at room temperature [9]. Nevertheless, some recent progress is advancing the state-of-the art in Si/SiGe RTDs with PVCRs reported up to 2.9 [10].

Research on alternative Si-based RTDs is seeking a suitable wide bandgap barrier that is also compatible with crystalline

Si wells, but this presents a daunting epitaxial growth problem. Some Si-based RTD structures used SiO<sub>2</sub> [11], [12] or Al<sub>2</sub>O<sub>3</sub> [13] barriers, but severe constraints on epitaxial overgrowth of a thin (<5 nm) crystalline Si quantum well atop the amorphous oxide barrier as well as the Si/oxide interface roughness have hampered progress [14]. A more promising avenue amongst recent Si-based RTD investigations is exploring alternative barriers such as CaF<sub>2</sub> that do permit epitaxial overgrowth of crystalline Si, but epitaxial growth of the CaF<sub>2</sub> is on  $\langle 111 \rangle$  Si substrates, which are not CMOS compatible [15], [16].

An interesting approach that is gaining attention is a paradigm shift back to an Esaki-like interband tunnel diode. This effectively replaces the challenging epitaxy found in the Si-based RTDs with a new challenge of achieving degenerate doping during a near-equilibrium epitaxial growth technique. The discrete Esaki tunnel diodes of the 1960s using alloying techniques have set benchmarks for Si Esaki diodes with room-temperature PVCR as high as 4.0 [17] and Ge Esaki diodes with PVCR of 8.3 [18]. A modern version of the Esaki diode using spin-on glass dopant diffusion has reported PVCRs up to 2.2 that could be more promising for monolithic integration [19]. It should be noted that a PVCR beyond 3 does not increase the speed index significantly [20]. In addition, a significant advantage for interband tunnel diodes is that both elastic and inelastic scattering can contribute to valley current in an intraband tunnel diode, but only inelastic scattering can contribute to the valley current of an interband tunnel diode [20].

The first successful epitaxially grown Si-based interband tunnel diode was shown by Jorke *et al.* with a PVCR of 2 at room temperature by inserting a thin i-layer between the  $p^+$ - $n^+$  emitter-base junction [21], but this fine work was largely overlooked by the scientific community, as the context of the overall paper was upon bipolar junction transistors (BJTs).

Another interband tunnel diode structure was proposed by Sweeny and Xu [22] using  $\delta$ -doping to create confined states in the valence and conduction bands on the p-side and n-side of a p-n junction, respectively. This creates an interband resonance tunneling condition between the states. This class of tunnel diodes was aptly named the resonant interband tunnel diode (RITD) class. An initial attempt at creating an epitaxially grown Si-based RITD using  $\delta$ -doping injectors showed some bistability but no room-temperature NDR [23].

More fundamental to the success of a Si-based interband tunnel diode are the processing steps that are used that anticipate dopant segregation and diffusion during epitaxial growth and processing and minimize their detrimental effects. Eventually, dopant segregation effects [24] were overcome by the far-from-equilibrium technique of low-temperature molecular beam epitaxy (LT-MBE) [25], [26] to effectively create the first Si-based RITD [27]. This Si/SiGe RITD combined several key points: i)  $\delta$ -doping injectors, ii) a composite *i*-layer inserted as a spacer layer between the  $\delta$ -doped injectors to minimize interdiffusion, iii) LT-MBE to suppress segregation and diffusion, and iv) a short post-growth rapid thermal anneal (RTA) heat treatment to reduce point defects created during the LT-MBE process that elevate the excess current. Using this modified approach resulted in initial reports of room-temperature PVCR in Si-based RITDs using  $\delta$ -doping at 1.54 with a peak current density of 3.2 kA/cm<sup>2</sup> [26] but quickly leaped to over 2 at a peak current density of 22 kA/cm<sup>2</sup> when the substrate temperature during MBE growth was further reduced [28]. A variety of alternative Si/SiGe RITDs have been demonstrated as well as some that are Si-only [28]–[30] and both polarity "n-on-p" [27]–[31] and "p-on-n" RITDs [32] as well as vertically-stacked p-n-p RITDs that exhibit symmetrical NDR about the origin for simple latches [33]. Measured peak current densities have been engineered between 0.2 A/cm<sup>2</sup> and 32 kA/cm<sup>2</sup> using Sb as the n-type dopant [27]–[33]. Antimony is greatly affected by segregation [24] during growth and a switch to P as the n-type dopant has been shown to elevate PVCR [34], [35].

These four basic points have now led other research groups to reproduce these results using other MBE growth reactors [34]–[36] and have even lead to PVCRs up to 6 at room temperature in an Si-based interband tunnel diode [35].

Further refinements to the basic RITD structure continue to maximize PVCR and integrate these structures with Si CMOS processing. To maximize the PVCR, a higher peak current density and a lower valley current density are desired. For a Si-based RITD, the peak current density is determined by the electron tunneling probability through the tunneling barrier, which depends on the dopant profile of both sides of the p-n junction. Sharper dopant profiles will lead to higher tunneling current and, thus, higher peak current density. Valley current density becomes elevated by the defects within the tunneling barrier created during the LT-MBE growth process. LT-MBE is needed to minimize dopant diffusion and segregation during epitaxy. Post-growth annealing can reduce the point defect density, thus lowering the valley current density. However, this also unfavorably broadens the dopant profiles, especially B, which is a fast interstitial diffuser, and thus, the peak current density can also be reduced if overannealed. Given that SiGe can act as an effective diffusion barrier for B in a Si matrix [37], structures with SiGe layers cladding the B  $\delta$ -doping layer were grown in order to preserve the sharp B profile during high temperature post-growth annealing to reduce the point defect density. Table I summarizes the results of prior Si-based tunnel diodes in chronological order.

Preliminary attempts at integration of tunnel diodes with Si CMOS began with a hybrid approach using epitaxial lift-off and a pick-and-place technique of selectively pasting III–V RTDs onto large bond pads connected to a CMOS circuit [38]. This was effective in demonstrating the proof of principle, but due to large parasitics capacitances amounting to an aggregate capacitance of 1740 fF, which was 1681 fF higher than desired, the circuit performance gains over all-CMOS circuits were not realized. A true monolithic integration of Si-based Si/CaF<sub>2</sub> RTDs with Si CMOS is just beginning [39].

In this manner, the aim of this work is to raise the thermal budget of the RITDs in order to maximize the PVCR and relax monolithic integration constraints. In addition, preliminary results for selectively grown tunnel diodes onto CMOS wafers are reported.

# II. EXPERIMENTAL

Epitaxial growth was achieved in an MBE growth system using elemental Si and Ge sources heated by electron-beams. The structures were grown on 76 mm B-doped ( $\rho=0.015$

TABLE I

COMPARISON OF PERFORMANCE, PEAK-TO-VALLEY CURRENT RATIO (PVCR) AND PEAK CURRENT DENSITY (Jp), OF Si-BASED TUNNEL DIODES

REALIZED BY EPITAXIAL GROWTH TECHNIQUES IN CHRONOLOGICAL ORDER

| Device<br>Configuration | PVCR                | Jp (A/cm2) | References                   |

|-------------------------|---------------------|------------|------------------------------|

| Si Esaki                | 3.80                | 1,000      | Franks et al. (1965) [17]    |

| Ge Esaki                | 8.30                |            | Germanium Power Devices [18] |

| Si/SiGe RTD             | 1.20                | 400        | Ismail et al. (1991) [9]     |

| Si Esaki                | 2.00                | 900        | Jorke et al. (1993) [21]     |

| Si/SiGe RITD            | 1.54                | 3,200      | Rommel et al. (1998) [28]    |

| Si/SiGe RITD            | 2.05                | 22,000     | Rommel et al. (1999) [29]    |

| Si-only RITD            | 1.41                | 10,800     | Thompson et al. (1999) [30]  |

| Si-only RITD            | 2.05                | 2,300      | Thompson et al. (1999) [31]  |

| Si/SiGe RITD            | 4.20                | 3,000      | Duschl et al. (1999) [34]    |

| Si/SiGe RITD            | 6.00                | 1,500      | Duschl et al. (2000) [35]    |

| CaF2/CdF2 RTD           | $7.6 \times 10^{5}$ | 63         | Watanabe et al. (2000) [15]  |

| CaF2/Si/CaF2 RTD        | 6.30                | N/A        | Watanabe et al. (2000) [16]  |

| Si/SiGe RTD             | 2.90                | 4,300      | See et al. (2001) [10]       |

| Si/SiO2 RTD             | 1.80                | 0.002      | Ishikawa et al. (2001) [11]  |

| Si/Al2O4 RTD            | 3.0-4.5             | N/A        | Shahjahan et al. (2002) [13] |

| Si Esaki                | 2.00                | 100        | Wang et al. (2002) [19]      |

| Si/SiGe RITD            | 3.60                | 300        | This Work                    |

$\Omega$ ·cm $-0.04~\Omega$ ·cm) Si (100) wafers. Prior to device fabrication, portions of the wafers were heat treated using a forming gas ambient (H<sub>2</sub>/N<sub>2</sub>) in an RTA at various temperatures for 1 min. A Ti/Au backside contact was thermally evaporated on all of the samples. Then, Ti/Au dots with a range of diameters were patterned on the surface of the wafers via standard contact lithography. A buffered oxide etch was used prior to metallization to remove the native oxide. Using the Ti/Au dots as a self-aligned mask, HF/HNO $_3$  wet etching was performed to define the diode mesa.

The I-V characteristics were measured using a probe station with a needle probe to make contact to the top of the mesa and the chuck to make contact to the backside contact. A semiconductor parameter analyzer was used to sweep the voltage and measure the resulting device currents.

# III. RESULTS AND DISCUSSIONS

# A. SiGe Diffusion Barriers Cladding the B $\delta$ -Doping Injector

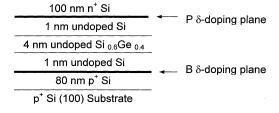

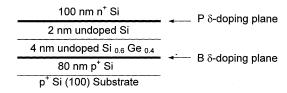

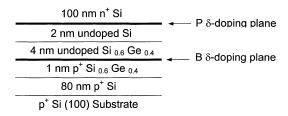

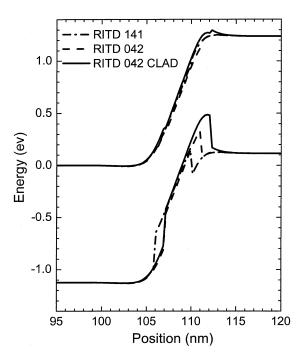

Three structures were designed to study the effect of the SiGe cladding layer. All structures maintained the fundamental tunnel barrier thickness of 6 nm, as measured between the two  $\delta$ -doping layers, which to first order determines the tunneling distance. RITD141, which is the control device, employed a symmetrical 1 nm Si/4 nm Si<sub>0.6</sub>Ge<sub>0.4</sub>/1 nm Si (1/4/1) spacer, as shown in Fig. 1, which is similar to many past structures studied by the authors. Fig. 2 shows RITD042 with an asymmetrical 0 nm Si/4 nm Si<sub>0.6</sub>Ge<sub>0.4</sub>/2 nm Si (0/4/2) spacer, resembling the modification provided by Duschl *et al.* [34], [35]. Note that the SiGe layer was directly grown atop the B  $\delta$ -layer without the thin Si offset layer. Fig. 3 shows RITD042clad, which is the

Fig. 1. Schematic diagram of RITD141, which is a (1/4/1) RITD that uses a 1-nm Si/4 nm Si<sub>0.6</sub> Ge<sub>0.4</sub>/1 nm Si undoped spacer configuration.

Fig. 2. Schematic diagram of RITD042, which is a (0/4/2) RITD that uses a 4–nm  $\rm Si_{0.6}Ge_{0.4}/2$  nm Si undoped spacer configuration. Note that the SiGe layer was directly grown atop the B  $\delta$ -layer without the thin 1–nm Si offset layer.

same as RITD042, except that a 1-nm Si $_{0.6}$ Ge $_{0.4}$  cladding layer was also grown below the B  $\delta$ -layer and outside the tunneling spacer. In this structure, the B  $\delta$ -layer was essentially clad by thin SiGe on both sides. It should be stressed that all structures maintained the same fundamental tunnel barrier thickness of 6 nm, as measured between the two  $\delta$ -doping layers, to facilitate easy comparison of the results. For all these three structures, the nominal n-type and p-type bulk doping levels in the injectors are 5  $\times$  10<sup>19</sup> cm $^{-3}$ , whereas the nominal n-type and p-type  $\delta$ -doping levels are 1  $\times$  10<sup>14</sup> cm $^{-2}$ .

Fig. 3. Schematic diagram of RITD042clad, which is a RITD (0/4/2) with cladding layer that uses a 4–nm Si $_{0.6}$ Ge $_{0.4}$ /2 nm Si undoped spacer configuration like RITD042 but with an additional SiGe cladding layer outside the active  $\delta$ -to- $\delta$  spacing. As a result, the B  $\delta$ -layer was essentially clad by thin SiGe on both sides.

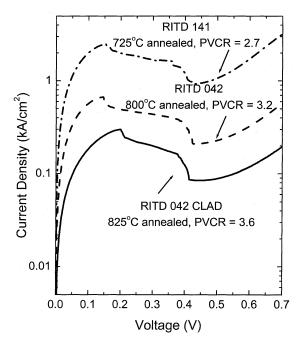

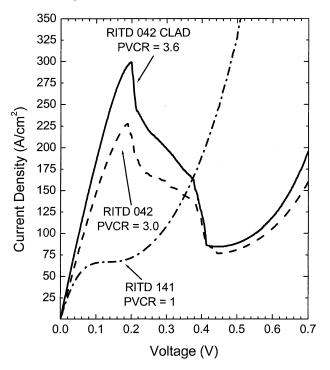

Fig. 4. Measured room-temperature I-V characteristics of the three RITD structures showing the highest PVCR for each structure. RITD141 showed a PVCR of 2.7 with a peak current density of 2.5 kA/cm². RITD042 showed a PVCR of 3.2 with a peak current density of  $0.7 \, \text{kA/cm}^2$ . RITD042clad showed a PVCR of 3.6 with a peak current density of  $0.3 \, \text{kA/cm}^2$ . Note that the optimized annealing temperatures are different for each structure, but the duration was held at 1 min each. Estimated relative uncertainties are  $\pm 2\%$  in current density and  $\pm 1\%$  in voltage.

Fig. 4 shows the I-V characteristics of these three structures with the highest PVCR. RITD141 demonstrates a PVCR of 2.7 with 1-min annealing at 725 °C. RITD042 obtained a PVCR of 3.2 using 1-min annealing at 800 °C, whereas RITD042clad further improved its PVCR to 3.6 with 1-min annealing at 825 °C. The peak current density was reduced with the higher anneal temperatures. It is evident that RITD042clad exhibited superior PCVR performance over structures RITD141 and RITD042 and also withstood a much higher annealing temperature. To gain insight to why the I-V characteristics of the three structures are so different, further investigation of the dopant interdiffusion was performed, both experimentally and through theoretical calculations.

Atomic concentration profiles were obtained from RITD042, which was annealed at 800 °C for 1 min, by secondary ion mass spectrometry (SIMS) using a high-performance magnetic sector secondary ion mass spectrometer. The net impact energy of the

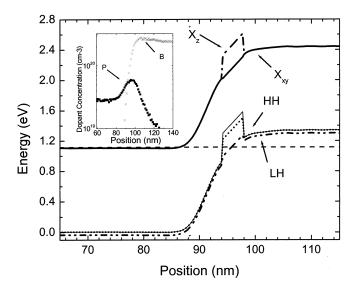

Fig. 5. Calculated band diagram using self-consistent Thomas-Fermi calculations of the electrostatic potential using a semiclassical density-of-states and measured SIMS data of RITD042 annealed at 800  $\,^{\circ}$ C for 1 min. Illustrated in the band diagram are the heavy hole (HH), and light hole (LH) bands in the valence band and the  $X_z$  and  $X_{xy}$  valleys of the conduction band.

primary beam—3 keV  $O_2^+$ —was selected in order to minimize profile broadening by ion beam mixing. Depth scales were obtained from stylus profilometry ( $\pm 3\%$  uncertainty). The atomic carrier concentrations of B and Sb were calibrated with implant standards ( $\pm 10\%$  uncertainty).

The band diagram, which is shown in Fig. 5, was calculated based on the SIMS data. These are self-consistent Thomas–Fermi calculations of the electrostatic potential using a semiclassical density of states. Due to limitations in SIMS depth resolution at the nanometer dimension, this presents a worst-case scenario for the band diagram. The resulting band diagram suggests RITD042 should work quite well. There exists significant overlap of the bands; see Fig. 5. Modeling of Structures RITD141 and RITD042clad, which are not shown, revealed band diagrams with no serious difference to RITD042. Therefore, the differences amongst the three structures should be reflected more due to changes in the out-diffusion of dopants that arise during the annealing steps as a result of their structural differences than the intrinsic structural differences.

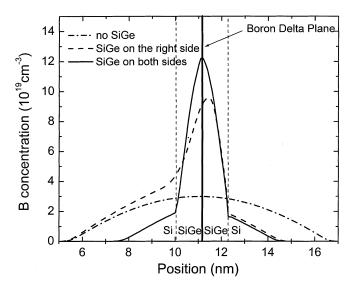

To approach the interdiffusion from a different angle, a commercial software package [40] was employed to predict the dopant displacement during the post-growth RTA anneal. Fig. 6 illustrates the effect of adding the SiGe cladding layer adjacent to the B  $\delta$ -doping layer on the B out-diffusion. An assumption was made that the diffusion starts with the as-grown B  $\delta$ -doping layer having a rectangular shape with a lateral 0.2–nm waist. Cases such as no SiGe cladding layer, SiGe cladding layer on the right side of the  $\delta$ -doping layer, and SiGe cladding layers on both sides are simulated. Note that not all of the curves in Fig. 6 correspond to the three structures studied here. However, the results in Fig. 6 clearly show that B out-diffusion is suppressed by SiGe cladding layers on both sides.

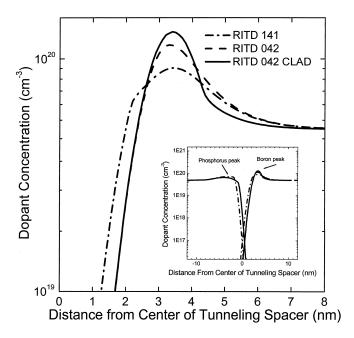

Fig. 7 shows the simulated Boron profile of RITD141, RITD042, and RITD042clad when subjected to a 1-min anneal at 800  $^{\circ}$ C. RITD042clad, which has SiGe cladding layers on both sides of the B  $\delta$ -layer, shows the sharpest B peak as

Fig. 6. Simulated B  $\delta$ -doping layer diffusion i) with no SiGe cladding layer, ii) SiGe cladding layer on the right side of the  $\delta$ -doping layer, and iii) SiGe cladding layers on both sides of the B profile, respectively. The as-grown  $\delta$ -doping spike is assumed to be  $10^{21}$  cm<sup>-3</sup> spread over a 1-nm lateral width.

Fig. 7. Modeled B-dopant profile of structures RITD141, RITD042, and RITD042clad by simulating a 1-min RTA anneal at 800 °C. Note that RITD042clad with SiGe cladding layers on both sides maintains the sharpest B peak.

expected. The Boron profiles with Phosphorus profiles of these three structures are shown in the inset of Fig. 7.

Fig. 8 shows the band diagram calculated using the modeled interdiffusion profiles shown in Fig. 7. Here, a strong shift in the band diagrams is visible for the three structures modeled. This is consistent with the large changes in tunnel diode PVCR for the three different structures. The authors believe the true doping profile and corresponding RITD band diagram lies between the result shown in Fig. 5, based on direct SIMS measurements, and the modeled doping profile in Fig. 7 and its associated band diagram shown in Fig. 8.

Fig. 8. Calculated band diagram using self-consistent Thomas-Fermi calculations of the electrostatic potential using a semi-classsical density-of-states of the three RITD structures shown in Fig. 7. For clarity, not all band valleys are presented.

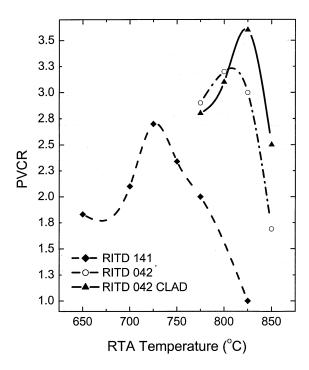

To fully understand the influence that B out-diffusion has on tunnel diode performance, the diodes were subjected to a range of anneal temperatures; see Fig. 9. Post-growth RTA processing has been shown to reduce point defects that contribute to elevated valley current but deleteriously broaden the B  $\delta$ -doping [27]. Consequently, an optimal RTA temperature exists that maximizes PVCR, which is clearly shown in Fig. 9. Note that the optimal annealing temperatures for these three structures are different, and RITD042CLAD shows the highest optimal annealing temperature, while RITD141 shows the lowest optimal annealing temperature. These results illustrate that insertion of the SiGe cladding layers suppresses B out-diffusion so that higher RTA temperatures can be employed to more effectively reduce point defects while minimizing the B diffusion to ensure a high peak current density. There is a 100 °C difference between the best PVCR from RITD141 and the best PVCR from RITD042clad, indicating that RITD042clad can withstand a higher thermal budget. Consequently, RITD042clad demonstrates the highest PVCR among these three structures.

The effect of the SiGe cladding layer can also be demonstrated by Fig. 10, which shows a comparison of the isothermal I-V characteristics of these three structures all annealed at 825 °C for 1 min. All three of these structures show similar valley current density indicating equivalent point defect removal, whereas RITD042clad shows the highest peak current density, due to the least amount of B out-diffusion.

# B. Patterned Growth Atop PMOS Source/Drain Implants for Monolithic Integration With CMOS

Integration of Si-based tunnel diodes with CMOS will require some modifications to the existing CMOS fabrication steps. To minimize the impact and limit the number of steps

Fig. 9. Comparison of the PVCR versus annealing temperature is shown for the three different structures studied. Note that RITD042clad shows both the highest optimal annealing temperature and the highest PVCR, which is consistent with the diffusion modeling. The lines are joins of the data points to assist the reader. Estimated relative uncertainties are  $\pm 2\%$  in current density and  $\pm 1\%$  in voltage.

Fig. 10. I-V characteristics of structures RITD141, RITD042, and RITD042clad are compared with all having undergone the same RTA heat treatment at 825  $\,^{\circ}$ C for 1 min. Note that the valley currents are nearly coincident, indicating each has an equivalent removal of point defects, but room-temperature PVCR is different in the three different structures. Estimated uncertainties are  $\pm 3\%$  in PVCR and  $\pm 5$   $\,^{\circ}$ C in RTA temperature.

in the process, integration will most likely occur by growing the Si-based tunnel diode onto pre-existing CMOS circuitry

Fig. 11. Measured I-V characteristics of a patterned grown RITD042clad structure through an oxide opening of a fully processed CMOS wafer. Estimated relative uncertainties are  $\pm 2\%$  in current density and  $\pm 1\%$  in voltage.

following all high-temperature CMOS processing but prior to CMOS metallization and interconnect metallizations. We have used patterned growth through oxide openings and onto implanted regions to validate the ability to place RITDs atop PMOS source and drain implant regions. The effect of residual implant damage on the RITD characteristic is being investigated in a separate study.

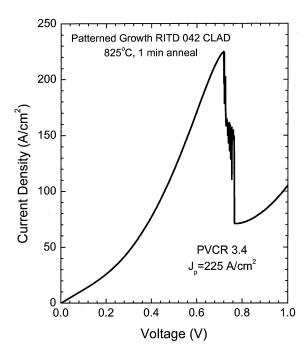

The influence of patterned growth was investigated by growing tunnel diodes through openings in a low-temperature oxide (LTO) deposited by chemical vapor deposition (CVD) at 425 °C. Windows of varying size were patterned in 300 nm of LTO grown on a p<sup>+</sup> Si substrate. RITD042CLAD was then replicated on this sample, using identical growth conditions. The epitaxial layer covered the entire wafer and was crystalline in the openings and amorphous atop the SiO2. The wafers then underwent RTA heat treatments similar to those performed on the discrete RITDs discussed earlier. The RITD mesa in the LTO opening was then patterned and etched with an SF<sub>6</sub> reactive ion etching plasma. The MBE layer grown atop the oxide was removed at this point; consequently, approximately 50 nm of the original LTO was unintentionally removed. A second LTO layer of 300 nm was then deposited and patterned for contact cuts to the devices. Al/Si was sputter deposited over the sample with a thickness of 600 nm, patterned, and wet etched to form contacts. The metal was sintered in a tube furnace under N<sub>2</sub>/H<sub>2</sub> ambient at 420 °C for 20 min.

The resulting device I-V characteristics are shown in Fig. 11. Patterned growth devices fabricated on a bulk p+ substrate exhibited a PVCR of 3.4 and a peak current density of 225 A/cm<sup>2</sup>. This is virtually identical to the PVCR of RITDs fabricated on a bulk sample. However, the observed peak voltage is shifted higher due to an increased series resistance observed in these devices either due to elevated ohmic contact resistance or due

to a depletion/accumulation layer at the regrown interface [41], [42]. This will be studied further.

#### IV. CONCLUSIONS

By introducing thin SiGe layers cladding the B  $\delta$ -doping layer, B out-diffusion is likely suppressed during post-growth annealing, which raises the thermal budget. A room-temperature PVCR of 3.6 was measured with a peak current density of 0.3 kA/cm². A higher RTA temperature appears to be more effective in reducing defects and results in a lower valley current and higher PVCR. Patterned growth of RITDs inside LTO openings also exhibited PVCR as high as 3.4 and showed little performance degradation compared with bulk-grown RITDs.

#### ACKNOWLEDGMENT

The authors would like to thank K. Hobart, A. Seabaugh, and G. Pomrenke for technical discussions and encouragement.

### REFERENCES

- L. Esaki, "New phenomenon in narrow Germanium p-n junctions," *Phys. Rev.*, vol. 109, p. 603, 1958.

- [2] E. Goto, K. Mutara, K. Nakazawa, T. Moto-Oka, Y. Matsuoka, Y. Ishibashi, T. Soma, and E. Wada, "Esaki diode high-speed logical circuits," *IRE Trans. Electron. Comput.*, vol. EC-9, pp. 25–29, 1960.

- [3] L. L. Chang, L. Esaki, and R. Tsu, "Resonant tunneling in semiconductor double barriers," Appl. Phys. Lett., vol. 24, pp. 593–595, 1974.

- [4] J. P. A. van der Wagt, A. C. Seabaugh, and E. A. Beam, III, "RTD/HFET low standby power SRAM gain cell," *IEEE Electron Dev. Lett.*, vol. 19, pp. 7–9, Jan. 1998.

- [5] T. P. E. Broekaert, B. Brar, J. P. A. van der Wagt, A. C. Seabaugh, T. S. Moise, F. J. Morris, E. A. Beam, III, and G. A. Frazier, "A monolithic 4-bit 2-Gsps resonant tunneling analog-to-digital converter," *IEEE J. Solid State Circuits*, vol. 33, pp. 1342–1349, Sept. 1998.

- [6] A. Seabaugh, X. Deng, T. Blake, B. Brar, T. Broekaert, R. Lake, F. Morris, and G. Frazier, "Transistors and tunnel diodes for analog/mixed-signal circuits and embedded memory," in *Int. Elect. Dev. Meeting Tech. Dig.*, 1998, pp. 429–432.

- [7] R. Compañó, L. Molenkamp, and D. J. Paul. (1999) Technology roadmap for nanoelectronics. Eur. Commission IST Programme Future Emerging Technol.. [Online], pp. 19–21. Available: ftp://ftp.cordis.lu/pub/esprit/docs/melnarm.pdf

- [8] "International technology roadmap for semiconductors,", http://public.itrs.net/Files/2001ITRS/Home.htm, p. 41, 2001.

- [9] K. Ismail, B. S. Meyerson, and P. J. Wang, "Electron resonant tunneling in Si/SiGe double barrier diodes," *Appl. Phys. Lett.*, vol. 59, pp. 973–975, 1991.

- [10] P. See, D. J. Paul, S. Mantl, I. V. Zozoulenko, and K.-F. Berggren, "High performance Si/Si<sub>1-x</sub>Ge<sub>x</sub> resonant tunneling diodes," *IEEE Electron. Dev. Lett.*, vol. 22, pp. 182–184, Apr. 2001.

- [11] Y. Ishikawa, T. Ishihara, M. Iwasaki, and M. Tabe, "Negative differential conductance due to resonant tunneling through SiO<sub>2</sub>/single-crystalline-Si double barrier structure," *Elect. Lett.*, vol. 37, pp. 1200–1201, 2001.

- [12] R. Lake, B. Brar, G. D. Wilk, A. Seabaugh, and G. Klimeck, "Resonant tunneling in disordered materials such as SiO<sub>2</sub>/Si/SiO<sub>2</sub>," *Compound Semi.*, vol. 1997, pp. 617–620, 1998.

- [13] M. Shahjahan, Y. Koji, K. Sawada, and M. Ishida, "Fabrication of resonance tunnel diode by gamma-Al<sub>2</sub>O<sub>3</sub>/Si multiple heterostructures," *Jpn. J. Appl. Phys.*, pt. 1, vol. 41, pp. 2602–2605, 2002.

- [14] T. Sandu, R. Lake, and W. P. Kirk, "The effect of interface quality on Si/SiO<sub>2</sub> resonant tunnel diodes," *Superlattices Microstructures*, vol. 30, pp. 201–204, 2001.

- [15] M. Watanabe, T. Funayama, T. Teraji, and N. Sakamaki, "CaF<sub>2</sub>/CdF<sub>2</sub> double-barrier resonant tunneling diode with high room-temperature peak-to-valley ratio," *Jpn. J. Appl. Phys.*, pt. 2, vol. 39, pp. L716–L719, 2000.

- [16] M. Watanabe, Y. Iketani, and M. Asada, "Epitaxial growth and electrical characteristics of CaF<sub>2</sub>/Si/CaF<sub>2</sub> resonant tunneling diode structures grown on Si(111) 1 degrees-off substrate," *Jpn. J. Appl. Phys.*, pt. 2, vol. 39, pp. L964–L967, 2000.

- [17] V. M. Franks, K. F. Hulme, and J. R. Morgan, "An alloy process for making high current density Si tunnel diode junctions," *Solid-State Electron.*, vol. 8, pp. 343–344, 1965. N. Holonyak, Jr. (private communication).

- [18] Germanium Power Devices Corp., , Andover, MA, 1996.

- [19] J. Wang, D. Wheeler, Y. Yan, J. Zhao, S. Howard, and A. Seabaugh, "Si tunnel diodes formed by proximity rapid thermal diffusion," in IEEE Lester Eastman Conf. High-Performance Devices, Newark, DE, 2002.

- [20] A. Seabaugh and R. Lake, "Tunnel diodes," Encyl. Appl. Phys., vol. 22, pp. 335–359, 1998.

- [21] H. Jorke, H. Kibbel, K. Strohm, and E. Kasper, "Forward-bias characteristics of Si bipolar junctions grown by molecular-beam epitaxy at low-temperatures," *Appl. Phys. Lett.*, vol. 63, pp. 2408–2410, 1993.

- [22] M. Sweeny and J. Xu, "Resonant interband tunnel diodes," Appl. Phys. Lett., vol. 54, pp. 546–548, 1989.

- [23] X. Zhu, X. Zheng, M. Pak, M. O. Tanner, and K. L. Wang, "A Si bistable diode utilizing interband tunneling junctions," *Appl. Phys. Lett.*, vol. 71, pp. 2190–2192, 1997.

- [24] K. D. Hobart, D. J. Godbey, M. E. Twigg, M. Fatemi, P. E. Thompson, and D. S. Simons, "Surface segregation and structure of Sb-doped Si(100) films grown at low temperature by molecular beam epitaxy," *Surf. Sci.*, vol. 334, pp. 29–38, 1995.

- [25] D. J. Eaglesham, H.-J. Gossmann, and M. Cerullo, "Limiting thickness h<sub>epi</sub> for epitaxial-growth and room-temperature Si growth on Si(100)," *Phys. Rev. Lett.*, vol. 65, pp. 1227–1230, 1990.

- [26] H. J. Gossmann, F. C. Unterwald, and H. S. Luftman, "Doping of Si thin-films by low-temperature molecular beam epitaxy," *J. Appl. Phys.*, vol. 73, pp. 8237–8241, 1993.

- [27] S. L. Rommel, T. E. Dillon, M. W. Dashiell, H. Feng, J. Kolodzey, P. R. Berger, P. E. Thompson, K. D. Hobart, R. Lake, A. C. Seabaugh, G. Klimeck, and D. K. Blanks, "Room temperature operation of epitaxially grown Si/Si<sub>0.5</sub> Ge<sub>0.5</sub>/Si resonant interband tunneling diodes," *Appl. Phys. Lett.*, vol. 73, pp. 2191–2193, 1998.

- [28] S. L. Rommel, T. E. Dillon, P. R. Berger, R. Lake, P. E. Thompson, K. D. Hobart, A. C. Seabaugh, and D. S. Simons, "Si-Based interband tunneling devices for high-speed logic and low power memory applications," in *Late News Int. Elect. Dev. Meet. Tech. Dig.*, 1998, pp. 1035–1037.

- [29] S. L. Rommel, T. E. Dillon, P. R. Berger, P. E. Thompson, K. D. Hobart, R. Lake, and A. C. Seabaugh, "Epitaxially grown Si resonant interband tunnel diodes exhibiting high current densities," *IEEE Electron Dev. Lett.*, vol. 20, pp. 329–331, July 1999.

- [30] P. E. Thompson, K. D. Hobart, M. Twigg, G. Jernigan, T. E. Dillon, S. L. Rommel, P. R. Berger, D. S. Simons, P. H. Chi, R. Lake, and A. C. Seabaugh, "Si resonant interband tunnel diodes grown by low temperature molecular beam epitaxy," *Appl. Phys. Lett.*, vol. 75, pp. 1308–1310, 1999.

- [31] P. E. Thompson, K. D. Hobart, M. E. Twigg, S. L. Rommel, N. Jin, P. R. Berger, R. Lake, A. C. Seabaugh, P. H. Chi, and D. S. Simons, "Epitaxial Si-based tunnel diodes," *Thin Solid Films*, vol. 380, pp. 145–150, 2000.

- [32] K. D. Hobart, P. E. Thompson, S. L. Rommel, T. É. Dillon, and P. R. Berger, "A P-on-N Si interband tunnel diode grown by molecular beam epitaxy," *J. Vac. Sci. Technol. B*, vol. 19, pp. 290–293, 2001.

- [33] N. Jin, P. R. Berger, S. L. Rommel, P. E. Thompson, and K. D. Hobart, "A PNP Si resonant interband tunnel diode with symmetrical NDR," *Elect. Lett.*, vol. 37, pp. 1412–1414, 2001.

- [34] R. Duschl, O. G. Schmidt, E. Kasper, and K. Eberl, "High room temperature peak-to-valley current ratio in Si-based Esaki diodes," *Elect. Lett.*, vol. 35, pp. 1111–1112, 1999.

- [35] R. Duschl and K. Eberl, "Physics and applications of Si/SiGe/Si resonant interband tunneling diodes," *Thin Solid Films*, vol. 380, pp. 151–153, 2000

- [36] M. W. Dashiell, R. T. Troeger, S. L. Rommel, T. N. Adam, P. R. Berger, J. Kolodzey, A. C. Seabaugh, and R. Lake, "Current voltage characteristics of high current density silicon Esaki diodes grown by molecular beam epitaxy and the influence of thermal annealing," *IEEE Trans. Electron Dev.*, vol. 47, pp. 1707–1714, Sept. 2000.

- [37] P. Kuo, J. L. Hoyt, J. F. Gibbons, J. E. Turner, and D. Lefforge, "Effects of strain on boron diffusion in Si and Si<sub>1-x</sub>Ge<sub>x</sub>," *Appl. Phys. Lett.*, vol. 66, pp. 580–582, 1995.

- [38] J. I. Bergman, J. Chang, Y. Joo, B. Matinpour, J. Laskar, N. M. Jokerst, M. A. Brooke, B. Brar, and E. Beam, "RTD/CMOS nanoelectronic circuits: Thin-film InP-based resonant tunneling diodes integrated with CMOS circuits," *IEEE Electron Dev. Lett.*, vol. 20, pp. 119–122, Mar. 1999.

- [39] T. Terayama, H. Sekine, and K. Tsutsui, "Fluoride resonant tunneling diodes co-integrated with Si-MOSFETs," *Jpn. J. Appl. Phys.*, pt. 1, vol. 41, pp. 2598–2601, 2002.

- [40] ATHENA Process Simulation Software. Santa Clara, CA: Silvaco Int..

- [41] D. Biswas, P. R. Berger, and P. K. Bhattacharya, "Recombination velocity at molecular beam epitaxial GaAs regrown interfaces," *J. Appl. Phys.*, vol. 65, pp. 2571–2573, 1989.

- [42] D. Biswas, P. R. Berger, U. Das, J. E. Oh, and P. K. Bhattacharya, "Investigation of the interface region produced by molecular beam epitaxial regrowth," *J. Elect. Mater.*, vol. 18, pp. 137–142, 1989.

**Niu Jin** received both the B.E. and M.E. degrees in materials science and engineering from Hefei University of Technology, Hefei, China, in 1995 and 1998, respectively. He received the M.S. degree in electrical engineering from The Ohio State University, Columbus, in 2001, where he is currently pursuing the Ph.D. degree, working on the development of Si-based RITDs with and integration with CMOS/HBT.

**Sung-Yong Chung** received the B.S. degree in metallurgical engineering from the Korea University, Seoul, Korea, in 1999 and the M.S. degree in electrical engineering from The Ohio State University, Columbus, in 2002, where he is currently pursuing the Ph.D. degree.

His research interests include RF circuits and TSRAM memory cells using device level design and fabrication with tunnel diodes and HBTs based on the Si/SiGe material system. Device processes and materials characterization of resonant interband tunnel diodes (RITD) and heterojunction bipolar transistors are also included in his research interests.

**Anthony T. Rice** (S'01) received the B.S. degree in electrical and computer engineering from The Ohio State University (OSU), Columbus, in 2000 and the M.S. degree in electrical engineering from OSU in 2003.

His research included the development of Si-based RITDs for integration into CMOS circuits, specifically the TSRAM memory cell.

**Paul R. Berger** (S'84–M'91–SM'97) received the B.S.E. degree in engineering physics in 1985 and the M.S.E. and Ph.D. degrees in electrical engineering in 1987 and 1990, respectively, all from the University of Michigan, Ann Arbor, where he worked on MBE strained layer growth, optoelectronic devices, and OEICs.

From 1990 to 1992, he was with Bell Laboratories, Murray Hill, NJ, working on optoelectronic devices and OEICs. He has been an Assistant Professor (from 1992 to 1997) and an Associate Professor (from 1997 to 2000) of electrical and computer engineering with the University of Delaware, Newark. In 1999, he spent a sabbatical leave at the Max-Planck Institute for Polymer Research, Mainz, Germany, and Cambridge Display Technology, Ltd., Cambridge, U.K. In 2000, he joined The Ohio State University, Columbus, as an Associate Professor. He currently is a Professor in both the Electrical and Computer Engineering and Physics Departments. He has co-authored over 70 archival refereed journal articles, over 60 invited and regular conference presentations, four book sections and been issued four U. S. patents with 13 more pending. Currently, he is actively working on nanoelectronic devices and fabrication processes; Si-based tunneling devices; polymer-based photonics and electronics; optoelectronic devices and integrated circuits; and semiconductor materials, fabrication, and growth.

Dr. Berger was a recipient of the 1996 National Science Foundation's Faculty Early Career Development Award. In 1998, he received the DARPA ULTRA Sustained Excellence Award. He was a co-organizer of the SRC sponsored Si Tunnel Diode and CMOS/HBT Integration Workshop in Washington, DC. He has been on the Program Committee of the International Electron Devices Meeting and SPIE conferences. He is a member of the Optical Society of America and the Materials Research Society.

**Phillip E. Thompson** (SM'96) received the Ph.D. degree in physics from the University of Delaware, Newark, in 1975.

He is the Head of the Si MBE Growth and Characterization Section, Code 6812, of the Electronics Science and Technology Division, Naval Research Laboratory (NRL), Washington, DC. He joined NRL in 1981 as a Research Physicist. He has over 22 years experience in electronic materials, including 15 years in MBE growth. He has over 180 publications and presentations. He holds four patents and has one pending.

Dr. Thompson received two NRL Tech Transfer Awards and the DARPA ULTRA Sustained Excellence Award in 1998. He is a member of APS.

Cristian Rivas, photograph and biograpy not available at time of publication.

**Roger Lake** (SM'01) received the Ph.D. degree in electrical engineering from Purdue University, West Lafayette, IN, in 1992.

He joined the Nanoelectronics Branch of Central Research Labs, Texas Instruments, Dallas, TX, in 1993 to develop the theory for the Nanotechnology Engineering Program, which became known as NEMO. In 1997, the Nanoelectronics Branch was acquired by Raytheon, where he worked on a number of different materials and devices: Si/SiGe tunnel diodes, InGaAs/InAlAs HEMTs for high-speed ADCs and low-power memory, InAs/AlSb and InGaAs/InAs/AlAs RTDs for ADC, TSRAM, and terahertz applications. Currently, he is with the Electrical Engineering Department, the University of California, Riverside, working on full-band, three-dimensional modeling of Si/SiGe quantum confined structures, high-frequency response of RTDs, molecular electronics, and quantum computing.

**Stephen Sudirgo** (S'02) received both the B.S. and M.S. degrees in microelectronic engineering from Rochester Institute of Technology (RIT), Rochester, NY, in 2000 and 2003, respectively. His M.S. thesis work consisted of integration studies of tunnel devices with CMOS. He is currently pursuing the Ph.D. degree in microsystems engineering at RIT.

He joined Fairchild Semiconductor, South Portland, MN, in winter 1998 and Lucent Technologies, Reading, PA, in winter of 1999 as a co-op engineer. His research interests include novel semiconductor devices, photonics, and microoptics.

**Jeremy J. Kempisty** received the B.S. degree in microelectronic engineering from Rochester Institute of Engineering in 2001.

He is currently an Implant Engineer with IBM, East Fishkill, NY.

**Branislav Curanovic** (S'02) received the B.S. degree in microelectronic engineering from Rochester Institute of Technology (RIT), Rochester, NY, in 2003, where he is currently pursuing the M.S. degree in microelectronic engineering.

He participated in this study as an NSF funded REU student in 2002. He was with Advanced Micro Devices, Austin, TX, in summer 2000 and 2001 as a co-op engineer in yield management and defect reduction. His research interests include novel solid-state devices and processes.

**Sean L. Rommel** (M'00) received both the B.S.E. and Ph.D. degrees in electrical engineering from the University of Delaware, Newark, in 1996 and 2000, respectively. His Ph.D. dissertation developed a process for the realization of Si-based tunnel diodes that could be integrated into a CMOS or BJT fabrication line.

From June 2000 to May 2002, he was a postdoctoral research associate at the Micro and Nano Technology Laboratory, University of Illinois at Urbana Champaign, where he specialized in the use of inductively coupled plasma-reactive ion etching and electron beam lithography for the fabrication of low-loss InP-based waveguides for ring resonators. Since July 2002, he has been an assistant professor with the Rochester Institute of Technology, Rochester, NY. His research interests include the development and integration of emerging device technologies into CMOS/BJT fabrication lines and photonic integrated circuits.

Dr. Rommel is a member of EDS, LEOS, and the American Vacuum Society. He is the recipient of the 1997 George W. Laird Merit Fellowship, the 2000 Excellence in Teaching Award, and the 2000 Allan P. Colburn Prize in Engineering and Mathematical Sciences for best dissertation.

**Karl D. Hirschman** (M'93–S'93–M'96) received the B.S. degree in microelectronic engineering in 1990 and the M.S. degree in electrical engineering in 1992 from the Rochester Institute of Technology (RIT), Rochester, NY. He received the Ph.D. degree in electrical engineering in 2000 from the University of Rochester

He has been with the RIT faculty since 1993. Previously, he was with the Advanced Semiconductor Technology Center (ASTC), IBM, East Fishkill, NY, as a process development engineer in advanced bipolar, CMOS, and DRAM technologies. He is currently an associate professor with the Microelectronic Engineering Department, where he also serves as the Director of the RIT Semiconductor and Microsystems Fabrication Laboratory (SMFL). His research interests include silicon-based optoelectronics, tunneling transport devices, and the integration of novel device structures in silicon technology. Dr. Hirschman has published over 30 technical papers in refereed journals and conference proceedings.

Dr. Hirschman is an active member in the IEEE EDS and MRS and has served as an officer of the Rochester IEEE EDS local chapter for the last nine years. He coordinates the IEEE Annual EDS Activities in Western NY Conference and is also on the steering committee of the IEEE/SEMI Advanced Semiconductor Manufacturing Conference.

Santosh K. Kurinec (M'89–SM'90) received the Ph.D. degree in physics from University of Delhi, Delhi, India, in 1980.

Currently, she is a Professor and Department Head of Microelectronic Engineering at Rochester Institute of Technology (RIT), Rochester, NY. Prior to joining RIT in 1988, she was an Assistant Professor of Electrical Engineering at Florida State University/Florida A&M University College of Engineering, Tallahassee. She was a post-doctoral research associate at the Department of Materials Science and Engineering, University of Florida, Gainesville, from 1985 to 1986, where she did research on thin metal film composites. Her current research activities include advanced integrated circuit materials and processes, tunnel devices, magnetic thin films, luminescent materials and devices, dielectric thin films, and microelectronic metallization. She has nearly 50 research publications, several book chapters, and a U.S. patent on high-resolution color phosphor screens.

Dr. Kurinec is a member of the Materials Research Society.

**Peter H. Chi** received the M.S. degree in physics from the Rensselaer Polytechnic Institute, Troy, NY, in 1984.

He is a physicist with the Surface and Microanalysis Science Division, Chemical Science and Technology Laboratory, National Institute of Standards and Technology (NIST), Gaithersburg, MD. He has worked in secondary ion mass spectrometry (SIMS) at the National Bureau of Standards (now NIST). His current research interest is concentrated on using primary cluster ion beams to study the secondary ion yield enhancements of metal elements and on performing high-precision measurements of ion implants in various semiconductor materials using SIMS.

**David S. Simons** received the Ph.D. degree in solid-state physics from the University of Illinois at Urbana-Champaign in 1973.

He is a research physicist and former group leader of the Analytical Microscopy Group, Surface and Microanalysis Science Division, Chemical Science and Technology Laboratory, National Institute of Standards and Technology, Gaithersburg, MD. He served a post-doctoral research appointment in the Materials Research Lab at the University of Illinois and was a chemist in the mass spectrometry group at the General Electric Knolls Atomic Power Laboratory, Schenectady, NY, before moving to the National Bureau of Standards (now NIST) in 1979. He has specialized in the applications of secondary ion mass spectrometry to microelectronic materials and to particle analysis.