# A General Framework for Analysing System Properties in Platform-Based Embedded System Designs

Samarjit Chakraborty Simon Künzli Lothar Thiele Computer Engineering and Networks Laboratory Swiss Federal Institute of Technology (ETH) Zurich, Switzerland

#### Abstract

We present a framework (Real-Time Calculus) for analysing various system properties pertaining to timing analysis, loads on various components and on-chip buffer memory requirements of heterogeneous platform-based architectures, in a single coherent way. Many previous analysis techniques from the real-time systems domain, which are based on standard event models, turn out to be special cases of our framework. We illustrate this using various realistic examples.

### 1 Introduction

The complexity of today's systems-on-chip (SoC) designs, coupled with issues like short time-to-market and low cost, have led to new design paradigms such as platformbased design [6]. These are based on the concept of *reuse* at several levels of abstraction, where designers rely on the use of intellectual property blocks or cores from some library (such as the IBM Blue Logic Core Library [5]), or on cores provided by a third-party vendor. Since such cores are already predesigned and verified, see [1], a designer can now concentrate on the overall system rather than the individual components, and also reduce the number of steps required to translate a system-level design into a final product.

Analysing such system platforms to verify timing and other system properties pose a major challenge because they depend on the interfaces and properties (such as arbitration schemes on buses) of the different cores, and also on the RTOS and other components of the software platform. The problem gets aggravated in the context of embedded systems because of their generally heterogeneous architecture, where different scheduling and resource sharing strategies are used on the different buses and processors.

The analysis involves verifying timing properties, identifying possible bottlenecks that might exist at a bus or a processor, and also estimate values of on-chip memory requirement, off-chip memory bandwidth, etc. However, currently there are almost no tools or methods which enable this in an easy and efficient manner. Existing approaches rely on simulation (for example VCC [13] and Seamless [10]), and hence suffer from the problems of high running time, incomplete coverage and failure to identify corner cases.

Most of the work on the formal analysis of such systems exists in a disjoint form and do not offer a single unified framework for analysing system-level designs, especially in the presence of heterogeneity. It is only recently that some work in this direction is being done—for example, [7] analyses response times for static-priority process scheduling combined with TDMA bus protocol. But the goal of a general approach to analysing different system properties (including timing behaviour) of an arbitrarily complex and heterogeneous platform architecture still remains elusive.

Relation to previous work. To address this problem, a general approach to timing analysis for heterogeneous systems was recently presented in [8] and [9]. It is based on identifying architectural components for which analysis methods are already known in the literature, and then combining these to obtain a compositional description of the complex system-level timing behaviour. The main drawback of this approach is that it can only accommodate standard event models like purely periodic, periodic with jitter, periodic with bursts, and sporadic. In practice, the event streams involved in a system usually do not conform to any of these standard models. But while analysing such systems, these streams are approximated by some standard model which minimizes the error. This introduces several modeling complexities, and when worst case bounds for a system are required, such approximations using standard event models give overly conservative bounds.

The analysis framework (Real-Time Calculus) that we present in this paper is based on an event model which can accurately capture the characteristics of any arbitrary event stream. Given the trace of an event stream, it is possible to extract a number of parameters which represent the abstract timing characteristics of the stream in our model. We show that this framework can be used to analyse complex and heterogeneous platform architecture and answer questions related to timing properties, on-chip memory requirements, and the load on different architectural components in a single coherent manner. Further, the results obtained by applying different scheduling strategies such as static priority, proportional share, time division multiplexing, and earliest deadline first on standard event models like periodic, periodic with jitter, sporadic, etc, turn out to be special cases of the results that can be obtained in our framework. The work in [8] and [9] is based on composing different *analysis domains* where each analysis domain is restricted to only standard event models. Our work extends and generalizes the concepts presented in [8, 9] and is not restricted to timing analysis, but can also address other system properties in an uniform way such as the memory demand and resource loads.

New results. The underlying theory behind our framework (Real-Time Calculus) was originally developed in the context of performance evaluation of network processor architectures [11, 12]. However, there were two major shortcomings of the work presented in [11] and [12]: (i) it was not shown how the framework compares with the theoretical results from the real-time systems area, (ii) how closely do the performance evaluation results match those obtained by simulation. As already pointed out in [14], without a clarification concerning the above two issues, the applicability of the framework can not be fully established. In relation to the results in [11, 12], the work in this paper addresses the issue (i). Firstly, it shows that the framework is not only restricted to analysing network processor architectures, but is applicable to the more general domain of heterogeneous embedded system designs. Secondly, as already mentioned, it shows that many of the results based on standard event models from the real-time systems area can also be obtained within our framework. The second issue mentioned above, i.e. (ii), is addressed in detail in [3] and [4]. Although the basic framework presented here is the same as in [11, 12], the mathematical bounds used to deduce timing properties of event streams being processed by an architecture, or those used to compute the loads on various architectural components are tighter compared to our previous results. The results in [11, 12] are concerned with event streams that have a fixed starting time (say t = 0). The new results pertain to event streams which span over  $t = -\infty$  to  $t = +\infty$  and therefore accurately capture event models like periodic, sporadic, etc., which do not have any specific starting time.

# 2 Event and Resource Models in Real-Time Calculus

In this section we describe the underlying event model which forms the basis of our framework and also a means of modeling the processing capability of resources which process incoming event streams.

**Event models.** For a given event stream, let R[s, t) denote the number of events that arrive in the time interval [s, t).

Further, assume that the number of events arriving within any interval of time is bounded above by a right-continuous, non-negative, subadditive function called the *upper arrival curve*, denoted by  $\alpha^u$ . Similarly, a lower bound on the number of events arriving is given by a *lower arrival curve*  $\alpha^l$ .  $R, \alpha^u$  and  $\alpha^l$  are related by the following inequality

$$\alpha^{l}(t-s) \le R[s,t) \le \alpha^{u}(t-s), \ \forall s < t$$

where  $\alpha^l(0) = \alpha^u(0) = 0$ .

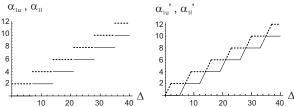

Therefore,  $\alpha^l(\Delta)$  and  $\alpha^u(\Delta)$  can be interpreted as the minimum and maximum number of events arriving within *any* time interval of length  $\Delta$ , respectively. Standard event models can be represented in our model by an appropriate choice of  $\alpha^l$  and  $\alpha^u$ . For example, a periodic event stream with period p can be represented by an  $\alpha^l$  and  $\alpha^u$ , both of which are staircase functions of step width p and height 1, with  $\alpha^l(\Delta) = 0$  for all  $0 \leq \Delta < p$  and  $\alpha^u(\Delta) = 1$  for all  $0 < \Delta \leq p$ . This is because within any time interval of length less than p, the minimum number of events that can be seen is zero, and within any time interval of length  $p^+$ , the minimum number of events that can be seen within any time interval of length  $p^+$  is one and two respectively.

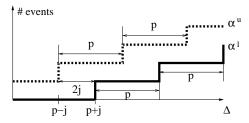

Following the same reasoning, the class of event streams with period p and jitter j can be represented by an upper and a lower arrival curve of the form shown in Figure 1. Given any particular instance of such a periodic with jitter event stream, the corresponding upper and lower arrival curves would lie within the arrival curves shown in Figure 1, and therefore these curves represent the upper and lower bounds on the maximum and minimum number of events that can arrive within any time interval for any event stream with period p and jitter j. Alternatively, given the upper and the lower arrival curves of the class of event streams *periodic* with jitter, then it is possible to uniquely determine the period and the jitter values. Note that in Figure 1, if j = 0 then the upper and the lower arrival curves coincide and represent a purely periodic event stream with period p. Formally, these results can be stated as follows:

The upper and the lower arrival curves representing the entire class of event streams with period p and jitter j are unique.

Similar representations in terms of the upper and the lower arrival curves can be given for standard (abstract) event models like sporadic and periodic with bursts, or for other event streams with a known analytical behavior. At the same time, given any finite length arbitrary event trace (from measurements or from simulation) and a real number  $\Delta$ , it is possible to determine the values of  $\alpha^{l}(\Delta)$  and  $\alpha^{u}(\Delta)$  corresponding to the event trace, by sliding a window of length  $\Delta$  over the trace and recording the minimum and maximum number of events lying within the window

**Figure 1.** The upper and lower arrival curves of the class of event streams with period p and jitter j.

respectively. The upper and the lower arrival curves corresponding to the trace can be determined by following this procedure for different values of  $\Delta$ .

**Processing capability.** Similar to the upper and lower arrival curves, we use  $\beta^u$  and  $\beta^l$  to denote upper and lower service curves of a resource with the following interpretation. If C[s,t) denotes the number of processing or communication units (might be in terms of processor cycles, time units, bytes, ...) available from the resource over the time interval [s,t), then the following inequality holds:  $\beta^l(t-s) \leq C[s,t) \leq \beta^u(t-s), \forall s < t$ . Hence,  $\beta^u(\Delta)$  and  $\beta^l(\Delta)$  give an upper and lower bound on the resource capability over any time interval of length  $\Delta$ . Again, these curves can be determined using data sheets of the used resources, e.g. busses or processing units, by using analytically derived properties or by using measurements.

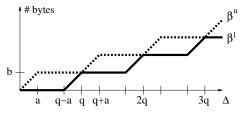

For example, in case of an unloaded processor, both resource curves may be equal and represented as straight lines, i.e.  $\beta^u(\Delta) = \beta^l(\Delta) = \Delta$ . A more complicated example is a time division multiplex bus with the period q. Within this period, a time units are available for the respective communication channel at a fixed offset and b bytes can be communicated within the available a time units. The corresponding curves are shown in Figure 2.

# **3** Analysing System Properties

# 3.1 Single Resource

**Processing a single stream.** An event stream entering a resource (such as a processor on which some processing function is implemented, or a communication resource such as a bus) gets processed (or transmitted in the case of a communication resource), thereby generating an outgoing event stream which might enter another resource for further processing. As a result, the processing capability (such as the processor or bus bandwidth) of the resource, as specified by its upper and lower service curves gets modified. In this section we formalize this notion and state the formulas for deriving the *outgoing arrival curves* and the *remaining service curves* from a specification of the incoming arrival curves and the original service curves.

Given an event stream which is specified by its arrival curves  $\alpha^l$  and  $\alpha^u$  and a resource which processes this event

**Figure 2.** The upper and lower service curves for a TDMA bus.

stream and its processing capability being specified by its service curves  $\beta^l$  and  $\beta^u$ . Let  $\alpha^{l'}$  and  $\alpha^{u'}$  denote the outgoing arrival curve of the (processed) event stream and  $\beta^{l'}$ and  $\beta^{u'}$  denote the remaining service curves of the resource. Then these curves are related by the following expressions:

$$\alpha^{l'}(\Delta) = \min\{\inf_{0 \le \mu \le \Delta} \{\sup_{\lambda \ge 0} \{\alpha^{l}(\mu + \lambda) - \beta^{u}(\lambda)\}\}$$

$$+\beta^{l}(\Delta-\mu)\},\beta^{l}(\Delta)\}$$

(1)

$${}^{u'}(\Delta) = \min\{\sup_{\lambda \ge 0} \{\inf_{0 \le \mu < \lambda + \Delta} \{\alpha^u(\mu) +$$

$$+\beta^{u}(\lambda+\Delta-\mu)\}-\beta^{l}(\lambda)\},\beta^{u}(\Delta)\} (2)$$

$$\beta^{l'}(\Delta) = \sup_{0 \le \lambda \le \Delta} \{\beta^l(\lambda) - \alpha^u(\lambda)\}$$

(3)

$$\beta^{u'}(\Delta) = \max\{\inf_{\lambda \ge \Delta} \{\beta^u(\lambda) - \alpha^l(\lambda)\}, 0\}$$

(4)

These results are based on generalizing ideas from network calculus as applied to the domain of communication networks (see [2] for details), and hold specifically for infinite event streams that span over time  $t = -\infty$  to  $t = +\infty$ . For modeling finite length event traces, the relations used in [11, 12] may be used.

**Processing Multiple Streams.** When multiple event streams enter a resource, the processing capability of the resource is shared between these streams according to some scheduling strategy. The characteristics of each of the outgoing streams and the remaining processing capability of the resource would depend on the scheduling strategy used. As an example, we derive these formulas for the case of static priority scheduling.

Let us assume that there are n event streams entering a resource whose processing capability is bounded by the service curves  $\beta^l$  and  $\beta^u$ . Each event stream i is constrained by the arrival curves  $\bar{\alpha}_i^l$  and  $\bar{\alpha}_i^u$  and let the streams be ordered according to their priorities, i.e. stream 1 has the highest priority and stream n the lowest. For each event stream i, let  $w_i$  be its per event processing requirement on the resource. From now on, we will assume  $w_i$  to be defined in time units, i.e. the resource takes  $w_i$  time units to process each event of the stream i. To take these different processing requirements into account, we scale  $\bar{\alpha}_i^l$  and  $\bar{\alpha}_i^u$  appropriately before using Equations (1–4). Hence we have,

$$\alpha_i^u = w_i \bar{\alpha}_i^u, \qquad \alpha_i^l = w_i \bar{\alpha}_i^l, \qquad i = 1, \dots, n \tag{5}$$

$\alpha$

Similarly, each outgoing processed event stream has to be scaled back as follows:

$$\overline{\alpha}_{i}^{u'} = \lceil \alpha_{i}^{u'}/w_i \rceil, \quad \overline{\alpha}_{i}^{l'} = \lfloor \alpha_{i}^{l'}/w_i \rfloor, \quad i = 1, \dots, n$$

(6)

In the case of static priority scheduling, the resource processes the event streams in the order of decreasing priority, and the resulting arrival and service curves are computed using Equations (1–4). For the event stream 1, the service curves of the unloaded resource serve as an input. For the *i*th event stream, the input service curve is equal to the remaining service curve after processing the (i - 1)th stream, for  $i \ge 2$ . This can be formally stated as follows:  $\beta_1^u = \beta^u$ ,  $\beta_1^l = \beta^l$ ,  $\beta_i^u = \beta_{i-1}^{u'}$ ,  $\beta_i^l = \beta_{i-1}^{l'}$ ,  $i = 2, \ldots, n$ , where  $\beta_{i-1}^{u'}$  and  $\beta_{i-1}^{l'}$  for  $i = 2, \ldots, n$  are determined from  $\beta_{i-1}^u$ ,  $\beta_{i-1}^l$ ,  $\alpha_{i-1}^u$  and  $\alpha_{i-1}^l$  by applying Equations (3) and (4). Lastly, the remaining service curve after processing all the event streams is given as follows:  $\beta^{u'} = \beta_n^{u'}$ ,  $\beta^{l'} = \beta_n^{l'}$ . This can be used to process other event streams, possibly using a different scheduling discipline, in a hierarchical manner.

### 3.2 Multiple Resources

Our view of a platform architecture with multiple resources is the following: Event streams flow through a network of resources based on the order in which they need to be processed. This model of an architecture can be represented as a scheduling network. The nodes of this network represent event processing functions that are implemented on the various resources. The inputs to each such node are the arrival curves of an event stream that is to be processed, and the service curve of the resource, representing the processing capability available to the function that is being implemented on the resource. The outputs describe the resulting arrival curves of the processed event streams and the remaining service curves of the (partially) used resource. These arrival and service curves then serve as inputs to other nodes of the scheduling network. Properties of the event streams like periodicity, jitter, bursts, etc change as the stream flows from one resource to the next, and these are captured in the arrival curves. Note that "resources" in our framework refer to both communication (such as buses) and computation (such as processors) resources. The exact construction of the scheduling network for an architecture depends on the scheduling policies on the different architectural components, an example of which is shown in the next section.

Let  $\alpha^l$  and  $\alpha^u$  be the lower and upper arrival curves of an event stream entering a node of a scheduling network whose input service curves are given by  $\beta^l$  and  $\beta^u$ . Then the maximum delay (or response time) experienced by an event at the resource represented by the service curves, and the maximum number of backlogged events from the stream

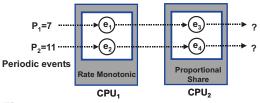

Figure 3. The system described in Example 2.

that waiting to be processed can be given by the following inequalities:

$$delay \leq \sup_{t \geq 0} \left\{ \inf\{\tau \geq 0 : \alpha^u(t) \leq \beta^l(t+\tau)\} \right\}$$

(7)

$$backlog \leq \sup_{t \geq 0} \{ \alpha^u(t) - \beta^l(t) \}$$

(8)

For a physical interpretation of these inequalities we refer the reader to [2]. From inequalities (7) and (8), it is possible to compute the overall response time and backlog of an event stream by summing its delay and backlog values at the different nodes (of the scheduling network) through which the stream passes. A possibility to get closer bounds for a given event stream by aggregating the service curves for all nodes that process this event stream is described in [3, 12].

Lastly, if  $\beta^u$  and  ${\beta^l}'$  are the initial upper service curve and the final lower (remaining) service curves of a resource, then its long term maximum utilization can be given by

$$utilization = \lim_{\Delta \to \infty} \frac{\beta^u(\Delta) - \beta^{l'}(\Delta)}{\beta^u(\Delta)}$$

This can, for example, be used to identify potential bottlenecks that exist in a platform architecture.

#### 4 Generalizing Standard Event Models

We now give two examples to show that in the case of heterogeneous system architectures, results from classical scheduling theory, that can be used to analyse standard event models (like periodic, sporadic, etc.), can also be derived within our framework. The work in [9] considered a number of examples of heterogeneous platform architectures involving standard event models and different scheduling strategies and answered various questions related to timing analysis using a compositional approach. By the use of some examples, it will be shown that similar and more general questions can be answered using the new unifying approach described in this paper.

**Example 1** Consider a periodic event stream entering a resource which requires a maximum of  $e_{max}$  and a minimum of  $e_{min}$  time units to process an event. The outgoing (processed) event stream is still periodic, but has a jitter equal to  $e_{max} - e_{min}$ .

Let  $t_0$  be some sufficiently small time instance where all events that arrived before  $t_0$  have been processed. Let

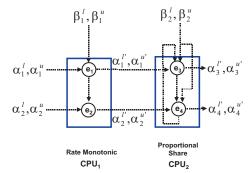

**Figure 4.** The scheduling network for the system described in Example 2.

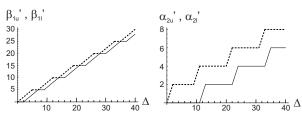

**Figure 5.** The upper and lower arrival curves of the incoming event stream 1 and the arrival curves of the processed stream coming out of  $CPU_1$  (dotted line show the upper curve and the solid line shows the lower curve).

$R[t_0,t)$  and  $R'[t_0,t)$  denote the number of arrived and processed events in the interval  $[t_0,t)$  for  $t_0 < t$ , respectively. Then we can derive  $R[t_0,t-e_{max}) \leq R'[t_0,t) \leq R[t_0,t-e_{min})$  if  $t_0 < t-e_{max}$ . Using these inequalities, we find for s < t the relation  $R'[s,t) \leq R[t_0,t-e_{min}) - R[t_0,s-e_{max}) = R[s-e_{max},t-e_{min}) \leq \alpha^u((t-s) + (e_{max}-e_{min}))$ . In a similar way, we have  $R'[s,t) \geq R[t_0,t-e_{max}) - R[t_0,s-e_{min}) = R[s-e_{min},t-e_{min}) \leq \alpha^l((t-s) - (e_{max}-e_{min}))$  for  $t-s > e_{max} - e_{min}$ .

As a first result, we find the feasible lower and upper curves of the processed events as  $\alpha^{u'}(\Delta) = \alpha^u(\Delta + (e_{max} - e_{min}))$  for  $\Delta > 0$  and  $\alpha^{l'}(\Delta) = \alpha^l(\Delta - (e_{max} - e_{min}))$  for  $\Delta > e_{max} - e_{min}$  and  $\alpha^{l'}(\Delta) = 0$  otherwise.

Hence, the number of events that can be seen at the output within any time interval of length  $\Delta$  is greater than or equal to the number of events that can be seen at the input over any time interval of length  $\Delta - (e_{\max} - e_{\min})$ , and is less than or equal to the number of events that can be seen at the input within any time interval of length  $\Delta + (e_{\max} - e_{\min})$ . This implies that the jitter of the output event stream increases by  $(e_{\max} - e_{\min})$  over the jitter of the input event stream. If the input stream is periodic with period p and jitter equal to  $(e_{\max} - e_{\min})$ .

**Example 2** A system consists of two processors  $CPU_1$  and  $CPU_2$ , on each of which two processes are implemented,

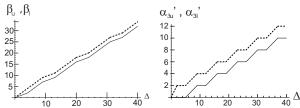

**Figure 6.** The service curves used to process stream 2 in  $CPU_1$  and the arrival curves of the processed stream coming out of  $CPU_1$ .

as shown in Figure 3. Two purely periodic event streams 1 and 2, with periods  $p_1 = 7$  and  $p_2 = 11$  respectively are processed by the two processes implemented on  $CPU_1$ . The per event processing time for both the event streams is equal to 2.  $CPU_1$  schedules the two processes processing streams 1 and 2 according to rate monotonic scheduling, and therefore stream 1 has higher priority over stream 2. The two outgoing, processed event streams are then processed by the two processes implemented on  $CPU_2$ , where the per event processing time is again equal to 2.  $CPU_2$  implements proportional share scheduling and gives equal processor share to both the processes. Both  $CPU_1$  and  $CPU_2$  implement preemptive scheduling. What are the characteristics of the two processed event streams coming out of  $CPU_2$ ?

We use the arrival curves of the input event streams entering  $CPU_1$  and from them compute the arrival curves of the final processed event streams coming out of  $CPU_2$ . These are then used to deduce the timing behaviour of the processed event streams. Figure 4 shows the scheduling network corresponding to the system. The entire processing capability of  $CPU_1$  is available to stream 1 since this has the higher priority. This is represented by  $\beta^u = \beta^l$ , both being straight lines of slope 1 passing through the origin. Figure 5 shows the arrival curves of the stream 1 and those of the processed stream. As described in Section 2, note that the processed stream is still periodic with period 7. In Figure 5, the arrival curves of the input event stream represent the discrete stream, but since the Equations (1-4) hold for continuous streams, to interpret the right hand figure in Figure 5 as a discrete stream, a *floor* function should be applied to the lower curve and a *ceiling* function to the upper curve.

The remaining processing capability of  $CPU_1$  that is available to stream 2 can be obtained by using Equations (3) and (4). These resulting service curves and the arrival curves of the processed stream are shown in Figure 6. The arrival curve of stream 2 is shown on the left hand side of Figure 8. As can be seen from this figure, the processed stream is still periodic with period 11, but now has a jitter smaller than or equal to 2.

In the case of  $CPU_2$ ,  $\beta_2^u$  and  $\beta_2^l$  represent the total unloaded processor capacity (see Figure 4) and are given by straight lines of slope 1 passing through the origin. Be-

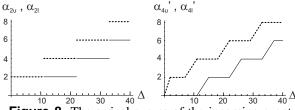

**Figure 7.** The service curves used to process stream 1 coming out of  $CPU_1$  (indicated as stream 3) and the arrival curves of the processed stream (by  $CPU_2$ ).

**Figure 8.** The arrival curves of the incoming event stream 2, and those of the finally processed stream coming out of  $CPU_2$  (i.e. after being processed at  $CPU_1$  and  $CPU_2$ ).

cause of the proportional share scheduling, both the incoming streams into  $CPU_2$  are guaranteed at least 50% of the available resource. But if one stream does not fully use its allocated resources, then the resulting leftover is available to the other stream. Therefore, the upper and lower service curves for stream 3 (i.e. the processed stream 1) are equal to  $\beta^u(\Delta) = 0.5 \cdot \beta_2^u(\Delta) + \max\{\inf_{\lambda \ge \Delta}\{0.5 \cdot \beta_2^u(\lambda) - \alpha_4^l(\lambda)\}, 0\}$  and  $\beta^l(\Delta) = 0.5 \cdot \beta_2^l(\Delta) + \sup_{0 \le \lambda \le \Delta}\{0.5 \cdot \beta_2^l(\lambda) - \alpha_4^u(\lambda)\}$  respectively. Here,  $\alpha_4^l$  and  $\alpha_4^u$  (which are equal to  $\alpha_2^{l'}$  and  $\alpha_2^{l'}$ , respectively) are the arrival curves of stream 4. The service curves available to stream 4 can similarly be computed from  $\beta_2^u, \beta_2^l, \alpha_3^l (= \alpha_1^{l'})$  and  $\alpha_3^u (= \alpha_1^{u'})$ .

Based on these service curves, the arrival curves of the processed streams 3 and 4 (by  $CPU_2$ ) are given in (the right hand of) Figures 7 and 8. From these curves, it can be deduced that the processed stream 1 (after passing through  $CPU_1$  and  $CPU_2$ ) has period 7 and a jitter smaller than or equal to 2 and the processed stream 2 (after passing  $CPU_1$  and  $CPU_2$ ) has the period 11 and jitter smaller than or equal to 4. These values exactly conform to those that can be obtained using classical scheduling theoretic results.

# 5 Conclusions

The framework (Real-Time Calculus) presented in this paper allows for a formal analysis of different system properties in heterogeneous platform-based designs. In particular, it is suited if the design is communication–centric, i.e. consisting of processing elements which are connected by a communication network that imposes constraints on delay and memory demand.

The purpose of the simple examples given in the paper is to show that known results can be easily derived from the Real-Time-Calculus. But it is important to note that one may use many different forms of input streams and not just periodic or sporadic ones. They all can be abstracted in the form of curves. In a similar way, the scheduling policies (fixed priority, proportional share, TDMA bus) are examples only.

The framework provides a single coherent way of deducing many results that can be derived using different event models and scheduling theoretic results from the domain of real-time systems.

#### References

- R. Bergamaschi, S. Bhattacharya, R. Wagner, C. Fellenz, M. Muhlada, W. Lee, F. White, and J.-M. Daveau. Automating the design of SoCs using cores. *IEEE Design & Test of Computers*, 18(5):32–45, 2001.

- [2] J. L. Boudec and P. Thiran. Network Calculus A Theory of Deterministic Queuing Systems for the Internet. LNCS 2050, Springer Verlag, 2001.

- [3] S. Chakraborty, S. Künzli, L. Thiele, A. Herkersdorf, and P. Sagmeister. Performance evaluation of network processor architectures: Combining simulation with analytical estimation. *Computer Networks* (to appear), 2003.

- [4] M. Gries, C. Kulkarni, C. Sauer, and K. Keutzer. Comparing analytical modeling with simulation for network processors: A case study. In *DATE*, Munich, 2003.

- [5] Blue Logic technology and CoreConnect bus architecture, IBM. http://www.chips.ibm.com/bluelogic/.

- [6] K. Keutzer, S. Malik, R. Newton, J. Rabaey, and A. Sangiovanni-Vincentelli. System level design: Orthogonolization of concerns and platform-based design. *IEEE Transactions on Computer-Aided Design*, 19(12), 2000.

- [7] P. Pop, P. Eles, and Z. Peng. Bus access optimization for distributed embedded systems based on schedulability analysis. In *DATE*, 2000.

- [8] K. Richter and R. Ernst. Model interfaces for heterogeneous system analysis. In *DATE*, 2002.

- [9] K. Richter, D. Ziegenbein, M. Jersak, and R. Ernst. Model composition for scheduling analysis in platform design. In *39th DAC*, 2002.

- [10] Seamless Hardware/Software Co-Verification, Mentor Graphics. http://www.mentor.com/seamless/.

- [11] L. Thiele, S. Chakraborty, M. Gries, and S. Künzli. Design space exploration of network processor architectures. In *Network Processor Design: Issues and Practices, Volume 1.* Morgan Kaufmann Publishers, October 2002.

- [12] L. Thiele, S. Chakraborty, M. Gries, and S. Künzli. A framework for evaluating design tradeoffs in packet processing architectures. In 39th DAC, New Orleans, 2002.

- [13] The Cadence Virtual Component Co-design (VCC). http://www.cadence.com/products/vcc.html.

- [14] T. Wolf. Design and Performance of a Scalable High-Performance Programmable Router. PhD thesis, Department of Computer Science, Washington University in St. Louis, May 2002.