# Improved Dielectric and Interface Properties of 4H-SiC MOS Structures Processed by Oxide Deposition and N<sub>2</sub>O Annealing

T. Kimoto<sup>1, a</sup>, H. Kawano<sup>1</sup>, M. Noborio<sup>1</sup>, J. Suda<sup>1, b</sup>, and H. Matsunami<sup>2, c</sup>

<sup>1</sup> Dept. of Electronic Sci. and Eng., Kyoto University, Katsura, Nishikyo, Kyoto 615-8510, Japan

<sup>2</sup> JST Innovation Plaza Kyoto, Oharagoryo, Nishikyo, Kyoto 615-8524, Japan

<sup>a</sup> kimoto@kuee.kyoto-u.ac.jp, <sup>b</sup> suda@kuee.kyoto-u.ac.jp, <sup>c</sup> hmatsunami@kyoto.jst-plaza.jp

Keywords: MOS, CVD, Nitridation, Channel mobility, RESURF MOSFET

Abstract. Oxide deposition followed by high-temperature annealing in N<sub>2</sub>O has been investigated to improve the quality of 4H-SiC MOS structures. Annealing of deposited oxides in N<sub>2</sub>O at 1300°C significantly enhances the breakdown strength and decreases the interface state density to  $3 \times 10^{11}$  cm<sup>-2</sup>eV<sup>-1</sup> at  $E_{\rm C} - 0.2$  eV. As a result, high channel mobility of 34 cm<sup>2</sup>/Vs and 52 cm<sup>2</sup>/Vs has been attained for inversion-type MOSFETs fabricated on 4H-SiC(0001)Si and (000-1)C faces, respectively. The channel mobility shows a maximum when the increase of oxide thickness during N<sub>2</sub>O annealing is approximately 5 nm. A lateral RESURF MOSFET with gate oxides formed by the proposed process has blocked 1450 V and showed a low on-resistance of 75 mΩcm<sup>2</sup>, which is one of the best performances among lateral SiC MOSFETs reported.

## Introduction

SiC power MOSFETs have been recognized as an ideal power switch, showing high voltage, low on-resistance, and fast switching speed. In recent years, a variety of efforts have been made for improving the quality of MOS interface. Nitridation of SiC MOS interface is a widely accepted technique, by which the channel mobility is remarkably enhanced in MOSFETs fabricated on 4H-SiC(0001) [1-3] as well as on other crystal faces [4]. Although the origin of interface defects has not been fully understood, several analyses have revealed that the SiO<sub>2</sub>/SiC interface is not abrupt and a high density of carbon (SiC<sub>x</sub>O<sub>y</sub> or SiO<sub>2</sub>+C clusters) is detected near the interface [4-6]. Since the residual carbon near the MOS interface might be inherent to thermal oxidation of SiC, the authors have investigated the potential of deposited oxides for SiC MOSFET fabrication. Though a few studies on deposited oxides have been reported [7-9], more systematic investigation and device application are described in this paper.

# **Experiments**

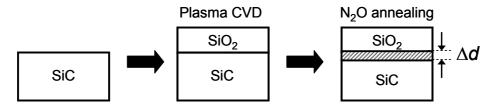

SiO<sub>2</sub> films were deposited on 4H-SiC(0001)Si and (000-1)C epilayers by plasma-enhanced CVD at 400°C by using TEOS and O<sub>2</sub> as source gases. The thickness of deposited oxides was varied in the range from 40 nm to 85 nm. In order to improve the oxide quality, the samples were annealed in Ar or N<sub>2</sub>O (10% in N<sub>2</sub>) at 1300°C for 60-360 min. During the N<sub>2</sub>O annealing (nitridation), the oxide thickness increased by  $\Delta d$ , as shown in Fig.1. MOS structures formed by N<sub>2</sub>O oxidation at 1300°C [8] were also prepared as a reference.

Fig.1. Schematic flow of "CVD + N<sub>2</sub>O annealing" process. The increase of oxide thickness by N<sub>2</sub>O annealing is denoted by  $\Delta d$ .

All rights reserved. No part of contents of this paper may be reproduced or transmitted in any form or by any means without the written permission of Trans Tech Publications, www.ttp.net. (#69695838, Pennsylvania State University, University Park, USA-12/09/16,17:34:01) To characterize the dielectric and interface properties, n-type MOS capacitors were fabricated. The diameter of Al electrodes was 300  $\mu$ m. The donor concentration of n-type epilayers was 1-3x10<sup>16</sup> cm<sup>-3</sup>. The channel mobility was assessed by processing planar inversion-type MOSFETs on p-type epilayers doped to 1x10<sup>16</sup> cm<sup>-3</sup>. Lateral high-voltage MOSFETs with a two-zone RESURF (Reduced Surface Field) structure [10,11] were also fabricated.

#### **Characterization of MOS capacitors**

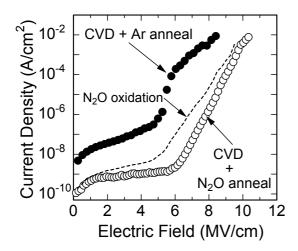

Figure 2 depicts the current density (*J*)–electric field (*E*) characteristics of n-type 4H-SiC(0001) MOS capacitors ( $d_{ox} = 60-72$  nm) formed by (a) plasma CVD and Ar annealing, (b) plasma CVD and N<sub>2</sub>O annealing, and (c) N<sub>2</sub>O oxidation. The typical characteristics among 20 MOS capacitors for each process are shown. The annealing time was 180 min in this particular case. Although the oxide formed by the "CVD + Ar anneal" process is leaky, N<sub>2</sub>O annealing resulted in significantly improved dielectric properties (resistivity:  $10^{16} \Omega$ cm, breakdown field > 10 MV/cm). From the ln(*J*/*E*<sup>2</sup>)–1/*E* plot (not shown), the barrier height was estimated to be 2.84 eV, in good agreement with a value theoretically expected. It should be noted that the oxides formed by CVD and N<sub>2</sub>O annealing exhibited almost the same (or slightly better) dielectric properties as those of N<sub>2</sub>O-grown oxides. Tanimoto et al. reported that ONO stack films formed on 4H-SiC by the CVD and oxidation process showed significantly improved dielectric properties, compared to standard thermal oxides [12]. Thus, "deposited oxides" may possess much potential if proper annealing such as N<sub>2</sub>O annealing at high temperature is performed.

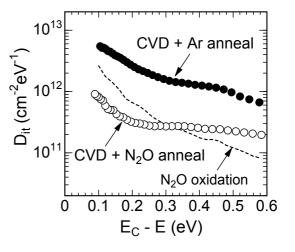

Figure 3 represents the distribution of interface state density ( $D_{it}$ ) for various MOS structures, which was determined from quasi-static and high-frequency (1 MHz) *C-V* curves of n-type 4H-SiC(0001) MOS capacitors ( $d_{ox} = 60-72$  nm). The "CVD + Ar anneal" sample showed very high interface state density, indicating that the interface formed by deposition itself is rather defective. However, both the CVD + N<sub>2</sub>O annealing and N<sub>2</sub>O oxidation processes yielded relatively low  $D_{it}$  values. The  $D_{it}$  values of "CVD + N<sub>2</sub>O anneal" sample are higher in the energetically deep region but lower near the conduction band edge ( $D_{it} = 3x10^{11}$  cm<sup>-2</sup>eV<sup>-1</sup> at  $E_C - 0.2$  eV), compared to the N<sub>2</sub>O-grown sample. Since electron trapping induced by a high density of interface states near the conduction band edge for "CVD + N<sub>2</sub>O anneal" sample will be promising.

Fig.2. Typical current density – electric field characteristics of n-type 4H-SiC(0001) MOS capacitors formed by different processes.

Fig.3. Distribution of interface state density for n-type 4H-SiC(0001) MOS capacitors formed by different processes (determined by a hi-lo method).

#### **Characteristics of MOSFETs**

Inversion-type test MOSFETs were processed on p-type 4H-SiC {0001} epilayers with an acceptor concentration of  $1 \times 10^{16}$  cm<sup>-3</sup>. The channel length and width were 50 µm and 200 µm, respectively. The source/drain regions were formed by high-dose ( $4 \times 10^{15}$  cm<sup>-2</sup>) P<sup>+</sup> ion implantation at 300°C followed by annealing at 1700°C for 20 min. Ni metals annealed in Ar at 1000°C were employed as ohmic contacts.

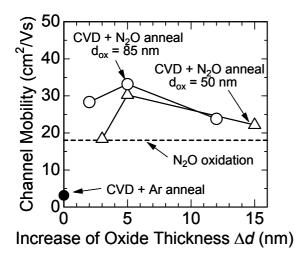

The MOSFET with a "CVD + Ar anneal" oxide showed a poor mobility of 4 cm<sup>2</sup>/Vs, as predicted from its high  $D_{it}$ . When the time of post-deposition annealing in N<sub>2</sub>O was changed, the channel mobility showed a maximum value for 90 min-annealing in the case of 50 nm-thick deposited oxide and 180 min for 85 nm-thick oxide, meaning that the optimum annealing time is dependent on the thickness of deposited oxide. This oxide-thickness dependence of the optimum annealing time may be more easily understood in Fig.4, where the channel mobility is plotted against the increase of oxide thickness during N<sub>2</sub>O annealing ( $\Delta d$  shown in Fig.1). At the  $\Delta d$  value of about 5 nm, maximum channel mobilities of 30-34 cm<sup>2</sup>/Vs were attained for two different thicknesses of deposited oxides. This result indicates about 50% improvement in mobility, compared to the standard N<sub>2</sub>O oxidation in the authors' group. The interface of deposited oxide/SiC should be modified, but the interface quality approaches that of N<sub>2</sub>O-grown interface when oxidation proceeds too much during the N<sub>2</sub>O annealing. The effective interface charge density of an optimized MOS structure was estimated to be 5-7x10<sup>11</sup> cm<sup>-2</sup> (negative) from the difference between experimental and theoretical threshold voltages. MOSFETs fabricated on the 4H-SiC(000-1)C face showed even higher mobilities of 46-52 cm<sup>2</sup>/Vs.

The proposed process (CVD + N<sub>2</sub>O anneal) with the optimum condition ( $\Delta d = 5$  nm) was applied to fabrication of lateral RESURF MOSFETs. The MOSFETs were fabricated on 10 µm-thick p-type 4H-SiC(0001) epilayers with an acceptor concentration of  $7.0 \times 10^{15}$  cm<sup>-3</sup>. The N<sup>+</sup> implant doses of 0.6 µm-deep two-zone RESURF regions were  $2.4 \times 10^{12}$  cm<sup>-2</sup> and  $7.8 \times 10^{12}$  cm<sup>-2</sup>. The details of device structure are described elsewhere [11]. Post-implantation annealing was performed at 1700°C for 20 min. The thickness of deposited oxide was 85 nm, and the channel length and width were 2 µm and 200 µm, respectively. Figure 5 shows the output characteristics of the fabricated 4H-SiC(0001) RESURF MOSFET measured at room temperature. The fabricated RESURF MOSFET exhibited a high breakdown voltage of 1450 V and a low on-resistance of 75 mΩcm<sup>2</sup> at an oxide field of 3.0 MV/cm. The effective channel mobility of test MOSFETs processed on the same substrate was 31

Fig.4. Effective channel mobility vs. increase of oxide thickness during  $N_2O$  annealing (4H-SiC(0001) face).

Fig.5. Drain characteristics of a 4H-SiC(0001) RESURF MOSFET with a deposited oxide followed by  $N_2O$  annealing at 1300°C.

cm<sup>2</sup>/Vs. The threshold voltage was 3.6 V, and the leakage current at 1000 V under zero-gate bias was 14 nA. The gate leakage at a drain voltage of 1000 V was below 20 pA. These characteristics are comparable to those of the MOSFET with a N<sub>2</sub>O-grown oxide and the same dose (breakdown voltage: 1280-1320 V, on-resistance: 67-84 m $\Omega$ cm<sup>2</sup>), and the present result is one of the best performances ( $V_{\rm B}^2/R_{\rm on} = 28$  MW/cm<sup>2</sup>) among any normally-off lateral MOSFETs. Advantages of the proposed process include the reduction of process time, especially on (0001)Si face, and nearly isotropic formation of oxides on trench sidewalls.

# Summary

4H-SiC MOS structures formed by oxide deposition followed by high-temperature annealing in N<sub>2</sub>O has been investigated. Although the deposited oxides annealed in Ar showed poor dielectric and interface properties, N<sub>2</sub>O annealing at 1300°C significantly improved the breakdown characteristics and reduced the interface state density to  $3x10^{11}$  cm<sup>-2</sup>eV<sup>-1</sup> at  $E_C - 0.2$  eV. The channel mobility was increased from about 20 cm<sup>2</sup>/Vs for N<sub>2</sub>O-grown oxides to 34 cm<sup>2</sup>/Vs by the "CVD + N<sub>2</sub>O annealing" process. The maximum channel mobility was obtained when the increase of oxide thickness during N<sub>2</sub>O annealing was about 5 nm. A high mobility of 51 cm<sup>2</sup>/Vs was realized by employing the 4H-SiC(000-1)C face. The lateral RESURF MOSFET with gate oxides formed by the proposed process blocked 1450 V and showed a low on-resistance of 75 mΩcm<sup>2</sup> at a gate oxide field of 3.0 MV/cm, which is one of the best performances among lateral SiC MOSFETs reported. Although the deposited oxides have not been an attractive choice in Si technology, the "CVD + N<sub>2</sub>O annealing" is a promising process for SiC MOS devices.

## Acknowledgements

This work was supported by a Grant-in-Aid for Scientific Research (No. 16360153) and the 21st century COE program (No. 14213201), from the Ministry of Education, Culture, Sports and Technology, Japan.

## References

- G.Y. Chung, C.C. Tin, J.R. Williams, K. McDonald, R. Chanana, R.A. Weller, S.T. Pantelides, L.C. Feldman, O.W. Holland, M.K. Das and J.W. Palmour: IEEE Electron Device Lett. Vol. 22 (2001), p. 176.

- [2] S. Dimitrijev, H.F. Li, H.B. Harrison, D. Sweatman: IEEE Trans. Electron Dev. Lett. Vol. 18 (1997), p. 175.

- [3] C.Y. Lu, J.A. Cooper, Jr., T. Tsuji, G. Chung, J.R. Williams, K. McDonald, and L.C. Feldman: IEEE Trans. Electron Devices, Vol. 50 (2003), p. 1582.

- [4] T. Kimoto, Y. Kanzaki, M. Noborio, and H. Matsunami: Jpn. J. Appl. Phys. Vol. 44 (2005), p. 1213.

- [5] K.C. Chang, N.T. Nuhfer, L.M. Porter, and Q. Wahab: Appl. Phys. Lett. Vol. 77 (2000), p. 2186.

- [6] V.V. Afanas'ev, F. Ciobanu, G. Pensl, and A. Stesmans: Silicon Carbide- Recent Major Advances, W.J. Choyke, H. Matsunami, and G. Pensl, Eds. Springer, Berlin (2003), p. 343.

- [7] G.Y. Chung, J.R. Williams, T. Isaacs-Smith, F. Ren, K. McDonald, and L.C. Feldman: Appl. Phys. Lett. Vol. 81 (2002), p. 4266.

- [8] L.A. Lipkin, M.K. Das and J.W. Palmour: Mater. Sci. Forum Vols. 389-393 (2002), p. 985.

- [9] H. Yano, T. Hatayama, Y. Uraoka, and T. Fuyuki: Mat. Sci. Forum Vols. 483-485 (2005), p. 685.

- [10] W. Wang, S. Banerjee, T.P. Chow and R.J. Gutmann: IEEE Electron Device Lett. Vol. 25 (2004), p. 185.

- [11] T. Kimoto, H. Kosugi, J. Suda, Y. Kanzaki, and H. Matsunami: IEEE Trans. Electron Devices Vol. 52 (2005), p. 112.

- [12] S. Tanimoto, H. Tanaka, T. Hayashi, Y. Shimoida, M. Hoshi, and T. Mihara: Mat. Sci. Forum Vols. 483-485 (2005), p. 677.

- [13] N.S. Saks: Silicon Carbide- Recent Major Advances, W.J. Choyke, H. Matsunami, and G. Pensl, Eds. Springer, Berlin (2003), p. 387.