## Lecture Notes in Computer Science

*Commenced Publication in 1973* Founding and Former Series Editors: Gerhard Goos, Juris Hartmanis, and Jan van Leeuwen

#### Editorial Board

| David Hutchison, UK           | Takeo Kanade, USA               |

|-------------------------------|---------------------------------|

| Josef Kittler, UK             | Jon M. Kleinberg, USA           |

| Alfred Kobsa, USA             | Friedemann Mattern, Switzerland |

| John C. Mitchell, USA         | Moni Naor, Israel               |

| Oscar Nierstrasz, Switzerland | C. Pandu Rangan, India          |

| Bernhard Steffen, Germany     | Madhu Sudan, USA                |

| Demetri Terzopoulos, USA      | Doug Tygar, USA                 |

| Gerhard Weikum, Germany       |                                 |

## Advanced Research in Computing and Software Science Subline of Lectures Notes in Computer Science

#### Subline Series Editors

Giorgio Ausiello, University of Rome 'La Sapienza', Italy Vladimiro Sassone, University of Southampton, UK

#### Subline Advisory Board

Susanne Albers, University of Freiburg, Germany Benjamin C. Pierce, University of Pennsylvania, USA Bernhard Steffen, University of Dortmund, Germany Madhu Sudan, Microsoft Research, Cambridge, MA, USA Deng Xiaotie, City University of Hong Kong Jeannette M. Wing, Carnegie Mellon University, Pittsburgh, PA, USA

# Tools and Algorithms for the Construction and Analysis of Systems

18th International Conference, TACAS 2012 Held as Part of the European Joint Conferences on Theory and Practice of Software, ETAPS 2012 Tallinn, Estonia, March 24 – April 1, 2012 Proceedings

Volume Editors

Cormac Flanagan University of California at Santa Cruz Jack Baskin School of Engineering Computer Science Department 1156 High Street, Santa Cruz, CA 95064, USA E-mail: cormac@ucsc.edu

Barbara König Universität Duisburg-Essen Fakultät für Ingenieurwissenschaften Abteilung für Informatik und Angewandte Kognitionswissenschaft Lotharstraße 65, 47057 Duisburg, Germany E-mail: barbara\_koenig@uni-due.de

ISSN 0302-9743 e-ISSN 1611-3349 ISBN 978-3-642-28755-8 e-ISBN 978-3-642-28756-5 DOI 10.1007/978-3-642-28756-5 Springer Heidelberg Dordrecht London New York

Library of Congress Control Number: 2012932744

CR Subject Classification (1998): F.3, D.2, C.2, D.3, D.2.4, C.3

LNCS Sublibrary: SL 1 – Theoretical Computer Science and General Issues

The use of general descriptive names, registered names, trademarks, etc. in this publication does not imply, even in the absence of a specific statement, that such names are exempt from the relevant protective laws and regulations and therefore free for general use.

Typesetting: Camera-ready by author, data conversion by Scientific Publishing Services, Chennai, India

Printed on acid-free paper

Springer is part of Springer Science+Business Media (www.springer.com)

<sup>©</sup> Springer-Verlag Berlin Heidelberg 2012

This work is subject to copyright. All rights are reserved, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, re-use of illustrations, recitation, broadcasting, reproduction on microfilms or in any other way, and storage in data banks. Duplication of this publication or parts thereof is permitted only under the provisions of the German Copyright Law of September 9, 1965, in its current version, and permission for use must always be obtained from Springer. Violations are liable to prosecution under the German Copyright Law.

#### Foreword

ETAPS 2012 is the fifteenth instance of the European Joint Conferences on Theory and Practice of Software. ETAPS is an annual federated conference that was established in 1998 by combining a number of existing and new conferences. This year it comprised six sister conferences (CC, ESOP, FASE, FOSSACS, POST, TACAS), 21 satellite workshops (ACCAT, AIPA, BX, BYTECODE, CMCS, DICE, FESCA, FICS, FIT, GRAPHITE, GT-VMT, HAS, IWIGP, LDTA, LINEARITY, MBT, MSFP, PLACES, QAPL, VSSE and WRLA), and eight invited lectures (excluding those specific to the satellite events).

The six main conferences received this year 606 submissions (including 21 tool demonstration papers), 159 of which were accepted (6 tool demos), giving an overall acceptance rate just above 26%. Congratulations therefore to all the authors who made it to the final programme! I hope that most of the other authors will still have found a way to participate in this exciting event, and that you will all continue to submit to ETAPS and contribute to making it the best conference on software science and engineering.

The events that comprise ETAPS address various aspects of the system development process, including specification, design, implementation, analysis, security and improvement. The languages, methodologies and tools that support these activities are all well within its scope. Different blends of theory and practice are represented, with an inclination towards theory with a practical motivation on the one hand and soundly based practice on the other. Many of the issues involved in software design apply to systems in general, including hardware systems, and the emphasis on software is not intended to be exclusive.

ETAPS is a confederation in which each event retains its own identity, with a separate Programme Committee and proceedings. Its format is open-ended, allowing it to grow and evolve as time goes by. Contributed talks and system demonstrations are in synchronised parallel sessions, with invited lectures in plenary sessions. Two of the invited lectures are reserved for 'unifying' talks on topics of interest to the whole range of ETAPS attendees. The aim of cramming all this activity into a single one-week meeting is to create a strong magnet for academic and industrial researchers working on topics within its scope, giving them the opportunity to learn about research in related areas, and thereby to foster new and existing links between work in areas that were formerly addressed in separate meetings.

This year, ETAPS welcomes a new main conference, *Principles of Security* and *Trust*, as a candidate to become a permanent member conference of ETAPS. POST is the first addition to our main programme since 1998, when the original five conferences met in Lisbon for the first ETAPS event. It combines the practically important subject matter of security and trust with strong technical connections to traditional ETAPS areas. A step towards the consolidation of ETAPS and its institutional activities has been undertaken by the Steering Committee with the establishment of *ETAPS e.V.*, a non-profit association under German law. ETAPS e.V. was founded on April 1st, 2011 in Saarbrücken, and we are currently in the process of defining its structure, scope and strategy.

ETAPS 2012 was organised by the Institute of Cybernetics at Tallinn University of Technology, in cooperation with

- ▷ European Association for Theoretical Computer Science (EATCS)

- ▷ European Association for Programming Languages and Systems (EAPLS)

- ▷ European Association of Software Science and Technology (EASST)

and with support from the following sponsors, which we gratefully thank:

INSTITUTE OF CYBERNETICS AT TUT; TALLINN UNIVERSITY OF TECH-NOLOGY (TUT); ESTONIAN CENTRE OF EXCELLENCE IN COMPUTER SCIENCE (EXCS) FUNDED BY THE EUROPEAN REGIONAL DEVELOP-MENT FUND (ERDF); ESTONIAN CONVENTION BUREAU; and MI-CROSOFT RESEARCH.

The organising team comprised:

| General Chair:        | Tarmo Uustalu                                                                   |

|-----------------------|---------------------------------------------------------------------------------|

| Satellite Events:     | Keiko Nakata                                                                    |

| Organising Committee: | James Chapman, Juhan Ernits, Tiina Laasma,                                      |

|                       | Monika Perkmann and their colleagues in the                                     |

|                       | Logic and Semantics group and administration<br>of the Institute of Cubernetics |

The ETAPS portal at http://www.etaps.org is maintained by *RWTH Aachen University*.

Overall planning for ETAPS conferences is the responsibility of its Steering Committee, whose current membership is:

Vladimiro Sassone (Southampton, Chair), Roberto Amadio (Paris 7), Gilles Barthe (IMDEA-Software), David Basin (Zürich), Lars Birkedal (Copenhagen), Michael O'Boyle (Edinburgh), Giuseppe Castagna (CNRS Paris), Vittorio Cortellessa (L'Aquila), Koen De Bosschere (Gent), Pierpaolo Degano (Pisa), Matthias Felleisen (Boston), Bernd Finkbeiner (Saarbrücken), Cormac Flanagan (Santa Cruz), Philippa Gardner (Imperial College London), Andrew D. Gordon (MSR Cambridge and Edinburgh), Daniele Gorla (Rome), Joshua Guttman (Worcester USA), Holger Hermanns (Saarbrücken), Mike Hinchey (Lero, the Irish Software Engineering Research Centre), Ranjit Jhala (San Diego), Joost-Pieter Katoen (Aachen), Paul Klint (Amsterdam), Jens Knoop (Vienna), Barbara König (Duisburg), Juan de Lara (Madrid), Gerald Lüttgen (Bamberg), Tiziana Margaria (Potsdam), Fabio Martinelli (Pisa), John Mitchell (Stanford), Catuscia Palamidessi (INRIA Paris), Frank Pfenning (Pittsburgh), Nir Piterman (Leicester), Don Sannella (Edinburgh), Helmut Seidl (TU Munich), Scott Smolka (Stony Brook), Gabriele Taentzer (Marburg), Tarmo Uustalu (Tallinn), Dániel Varró (Budapest), Andrea Zisman (London), and Lenore Zuck (Chicago).

I would like to express my sincere gratitude to all of these people and organisations, the Programme Committee Chairs and PC members of the ETAPS conferences, the organisers of the satellite events, the speakers themselves, the many reviewers, all the participants, and Springer-Verlag for agreeing to publish the ETAPS proceedings in the ARCoSS subline.

Finally, I would like to thank the Organising Chair of ETAPS 2012, Tarmo Uustalu, and his Organising Committee, for arranging to have ETAPS in the most beautiful surroundings of Tallinn.

January 2012

Vladimiro Sassone ETAPS SC Chair

## Preface

This volume contains the proceedings of the 18th International Conference on Tools and Algorithms for the Construction and Analysis of Systems (TACAS 2012). TACAS 2012 took place in Tallinn, Estonia, March 27–30, 2012, as part of the 15th European Joint Conferences on Theory and Practice of Software (ETAPS 2012), whose aims, organization, and history are presented in the foreword of this volume by the ETAPS Steering Committee Chair, Vladimiro Sassone.

TACAS is a forum for researchers, developers, and users interested in rigorously based tools and algorithms for the construction and analysis of systems. The research areas covered by TACAS include, but are not limited to, formal methods, software and hardware verification, static analysis, programming languages, software engineering, real-time systems, communications protocols, and biological systems. The TACAS forum provides a venue for such communities at which common problems, heuristics, algorithms, data structures, and methodologies can be discussed and explored.

This year TACAS solicited four kinds of papers. Research papers are fulllength papers that contain novel research on topics within the scope of the TACAS conference and relevant to tool construction. Case study papers report on case studies, describing goals of the study and the research methodologies and approach used. Regular tool papers present a new tool, a new tool component, or novel extensions to an existing tool, and focus primarily on engineering aspects. Tool demonstration papers are shorter papers that give an overview of a particular tool and its applications or evaluation.

This edition of the conference attracted a total of 147 submissions (108 research papers, 7 case study papers, 11 regular tool papers, and 21 tool demonstration papers). Each submission was evaluated by at least three reviewers, who wrote detailed evaluations and gave insightful comments. After a six-week reviewing process, we had a three-week electronic Program Committee meeting, during which we accepted 36 papers (25 research papers, 2 case study papers, 3 regular tool papers, and 6 tool demonstration papers) for presentation at the conference. In addition, the TACAS conference program was greatly enriched by the invited talk by Holger Hermanns and by the ETAPS unifying speakers Bruno Blanchet and Georg Gottlob.

One novel aspect of TACAS this year was the inclusion of a Competition on Software Verification. This volume includes an overview of the competition organization and results, presented by the TACAS Competition Chair Dirk Beyer, as well as short papers describing individual tools in the competition.

We would like to thank the authors of all submitted papers, the Program Committee members, and the external referees for their invaluable contributions. We also thank Alessandro Cimatti for serving as the TACAS Tool Chair and Dirk Beyer for organizing the Competition on Software Verification. The EasyChair system greatly facilitated the TACAS conference submission and program selection process. Finally, we would like to express our appreciation to the ETAPS Steering Committee and especially its Chair, Vladimiro Sassone, as well as the Organizing Committee, for their efforts in making ETAPS 2012 such a successful event.

January 2012

Cormac Flanagan Barbara König

## Organization

## Steering Committee

| Rance Cleaveland    | University of Maryland and Fraunhofer USA, USA |

|---------------------|------------------------------------------------|

| Joost-Pieter Katoen | RWTH Aachen, Germany                           |

| Kim G. Larsen       | Aalborg University, Denmark                    |

| Bernhard Steffen    | TU Dortmund, Germany                           |

| Lenore Zuck         | University of Illinois at Chicago, USA         |

## Program Committee

| Rajeev Alur        | University of Pennsylvania, USA                           |

|--------------------|-----------------------------------------------------------|

| Armin Biere        | Johannes Kepler University, Austria                       |

| Alessandro Cimatti | FBK-irst, Italy (Tool Chair)                              |

| Rance Cleaveland   | University of Maryland and Fraunhofer USA, USA            |

| Giorgio Delzanno   | University of Genova, Italy                               |

| Javier Esparza     | TU Munich, Germany                                        |

| Cormac Flanagan    | University of California at Santa Cruz, USA<br>(Co-chair) |

| Patrice Godefroid  |                                                           |

|                    | Microsoft Research, Redmond, USA                          |

| Susanne Graf       | Université Joseph Fourier/CNRS/Verimag, France            |

| Orna Grumberg      | Technion – Israel Institute of Technology, Israel         |

| Aarti Gupta        | NEC Labs America, USA                                     |

| Michael Huth       | Imperial College London, UK                               |

| Ranjit Jhala       | University of California at San Diego, USA                |

| Vineet Kahlon      | University of Texas at Austin, USA                        |

| Daniel Kroening    | University of Oxford, UK                                  |

| Marta Kwiatkowska  | University of Oxford, UK                                  |

| Barbara König      | University of Duisburg-Essen, Germany (Co-chair)          |

| Kim G. Larsen      | Aalborg University, Denmark                               |

| Rustan Leino       | Microsoft Research, Redmond, USA                          |

| Matteo Maffei      | Saarland University, Germany                              |

| Ken McMillan       | Cadence Berkeley Labs, USA                                |

| Doron Peled        | Bar Ilan University, Israel                               |

| Anna Philippou     | University of Cyprus, Cyprus                              |

| Nir Piterman       | University of Leicester, UK                               |

| Arend Rensink      | University of Twente, The Netherlands                     |

|                    |                                                           |

| Andrey Rybalchenko | TU Munich, Germany                     |

|--------------------|----------------------------------------|

| Stefan Schwoon     | ENS Cachan, France                     |

| Scott Smolka       | SUNY at Stony Brook, USA               |

| Bernhard Steffen   | TU Dortmund, Germany                   |

| Serdar Tasiran     | Koc University, Turkey                 |

| Lenore Zuck        | University of Illinois at Chicago, USA |

## Program Committee of the Competition on Software Verification

| University of Passau, Germany (Chair)         |

|-----------------------------------------------|

| University of Southampton, UK                 |

| Russian Academy of Sciences, Russia           |

| TU Munich, Germany                            |

| Karlsruhe Institute of Technology, Germany    |

| University of Oxford, UK                      |

| Vienna University of Technology, Austria      |

| Brno University of Technology, Czech Republic |

| Princeton University, USA                     |

| University of Passau, Germany                 |

| University of Paderborn, Germany              |

|                                               |

#### **Additional Reviewers**

Acciai. Lucia Aldini, Alessandro Alglave, Jade Ancona, Davide Bagherzadeh, Mehdi Ball, Thomas Bartocci, Ezio Bekar, Can Belinfante, Axel Blanchette, Jasmin Christian Bouajjani, Ahmed Bulychev, Peter Burckhardt, Sebastian Chen, Taolue Cheng, Chih-Hong Chilton, Chris Clemente, Lorenzo D'Silva, Vijay Dalsgaard, Andreas Dannenberg, Frits

David. Alexandre De Mol, Maarten Delahaye, Benoit Deshmukh, Jyotirmoy Deshpande, Tushar Diciolla, Marco Donaldson, Alastair Draeger, Klaus Duggirala, Parasara Sridhar Duret-Lutz, Alexandre Edelkamp, Stefan Elmas, Tayfun Falke, Stephan Feng, Lu Feo, Sergio Fernandez, Jean-Claude Ferrara, Pietro Filiot, Emmanuel Flur, Shaked Forejt, Vojtech

Gaiser, Andreas Ganty, Pierre Garg, Pranav Gastin, Paul Ghamarian, Amir Hossein Giro, Sergio Guerrini, Giovanna Guttman, Joshua Haar, Stefan Habermehl, Peter Haddad, Serge Haller, Leopold Han, Tingting He, Nannan Heule, Marijn Hinrichs, Timothy Howar, Falk Isberner, Malte Ivancic. Franio Järvisalo, Matti Kant, Gijs Khasidashvili, Zurab Kinder, Johannes Komuravelli, Anvesh Kretinsky, Jan Kulahcioglu, Burcu Kuru, Ismail La Torre, Salvatore Lal, Akash Lamprecht, Anna-Lena Lazic, Ranko Leroux, Jerome Lewis, Matt Mandrykin, Mikhail Matar, Hassan Salehe Mauborgne, Laurent Meller, Yael Mereacre, Alexandru Merten. Maik Merz, Stephan Methravil Varghese, Praveen Thomas Mikučionis, Marius Moskal, Michal Mounier, Laurent Møller, Mikael H.

Nadel. Alexander Naujokat, Stefan Neubauer, Johannes Nghiem, Truong Nimal, Vincent Norman, Gethin Nyman, Ulrik Ober, Iulian Olesen, Mads Chr. Palikareva, Hristina Parker, David Passerone, Roberto Phan, Linh Popeea, Corneliu Quinton, Sophie Rajan, Ajitha Ramachandran, Jaideep Raymond, Pascal Reuss, Andreas Ruething, Oliver Ryvchin, Vadim Rüthing, Oliver Sa'Ar, Yaniv Sangnier, Arnaud Schewe, Sven Seghir, Mohamed Nassim Seidl, Martina Sezgin, Ali Sheinvald, Sarai Shin, Insik Shoham, Sharon Simaitis, Aistis Soliman, Sylvain Srba. Jiri Stoelinga, Mariëlle Strichman, Ofer Subasi. Omer Tautschnig, Michael Timmer, Mark Tiwari, Ashish Traonouez, Louis-Marie Trivedi, Ashutosh Ummels, Michael Vaandrager, Frits Veanes, Margus

Viswanathan, Mahesh Vizel, Yakir Wang, Bow-Yaw Weissenbacher, Georg Windmüller, Stephan Wolf, Verena Yrke Jørgensen, Kenneth Zambon, Eduardo Zhang, Lijun Zuliani, Paolo

## Table of Contents

## Invited Contribution

| Quantitative Models for a Not So Dumb Grid                                                                                          | 1   |

|-------------------------------------------------------------------------------------------------------------------------------------|-----|

| SAT and SMT Based Methods                                                                                                           |     |

| History-Aware Data Structure Repair Using SAT<br>Razieh Nokhbeh Zaeem, Divya Gopinath, Sarfraz Khurshid, and<br>Kathryn S. McKinley | 2   |

| The Guardol Language and Verification System<br>David Hardin, Konrad Slind, Michael Whalen, and Tuan-Hung Pham                      | 18  |

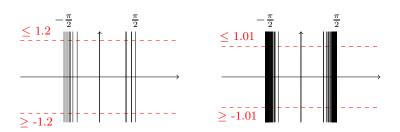

| A Bit Too Precise? Bounded Verification of Quantized Digital Filters<br>Arlen Cox, Sriram Sankaranarayanan, and Bor-Yuh Evan Chang  | 33  |

| Numeric Bounds Analysis with Conflict-Driven Learning<br>Vijay D'Silva, Leopold Haller, Daniel Kroening, and<br>Michael Tautschnig  | 48  |

| Automata                                                                                                                            |     |

| Ramsey-Based Analysis of Parity Automata<br>Oliver Friedmann and Martin Lange                                                       | 64  |

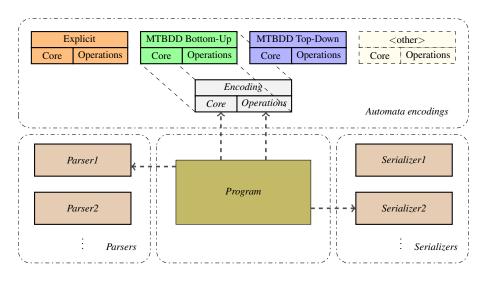

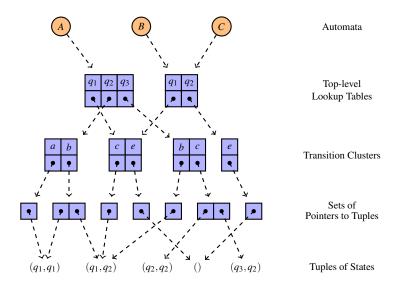

| VATA: A Library for Efficient Manipulation of Non-deterministic Tree<br>Automata<br>Ondřej Lengál, Jiří Šimáček, and Tomáš Vojnar   | 79  |

| LTL to Büchi Automata Translation: Fast and More Deterministic<br>Tomáš Babiak, Mojmír Křetínský, Vojtěch Řehák, and Jan Strejček   | 95  |

| Model Checking                                                                                                                      |     |

| Pushdown Model Checking for Malware Detection<br>Fu Song and Tayssir Touili                                                         | 110 |

| Aspect-Oriented Runtime Monitor Certification<br>Kevin W. Hamlen, Micah M. Jones, and Meera Sridhar                                 | 126 |

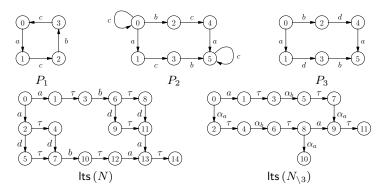

| Partial Model Checking Using Networks of Labelled Transition Systems |     |

|----------------------------------------------------------------------|-----|

| and Boolean Equation Systems                                         | 141 |

| Frédéric Lang and Radu Mateescu                                      |     |

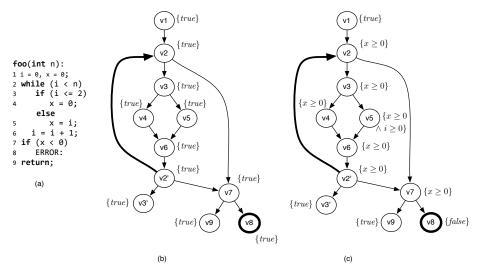

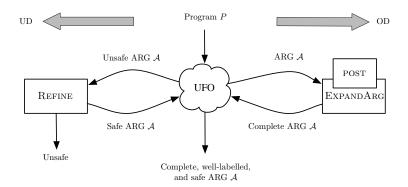

| From Under-Approximations to Over-Approximations and Back            | 157 |

| Aws Albarghouthi, Arie Gurfinkel, and Marsha Chechik                 |     |

#### **Case Studies**

| Automated Analysis of AODV Using UPPAAL                       | 173 |

|---------------------------------------------------------------|-----|

| Ansgar Fehnker, Rob van Glabbeek, Peter Höfner,               |     |

| Annabelle McIver, Marius Portmann, and Wee Lum Tan            |     |

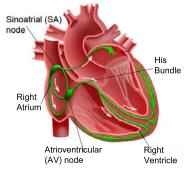

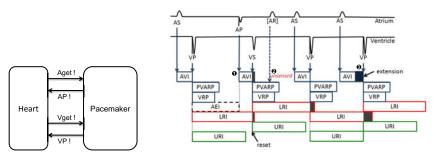

| Modeling and Verification of a Dual Chamber Implantable       |     |

| Pacemaker                                                     | 188 |

| Zhihao Jiang, Miroslav Pajic, Salar Moarref, Rajeev Alur, and |     |

| Rahul Mangharam                                               |     |

#### Memory Models and Termination

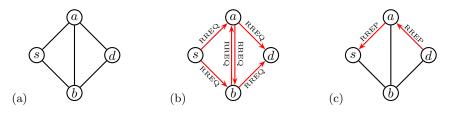

| Counter-Example Guided Fence Insertion under TSO<br>Parosh Aziz Abdulla, Mohamed Faouzi Atig, Yu-Fang Chen,<br>Carl Leonardsson, and Ahmed Rezine | 204 |

|---------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Java Memory Model-Aware Model Checking<br>Huafeng Jin, Tuba Yavuz-Kahveci, and Beverly A. Sanders                                                 | 220 |

| Compositional Termination Proofs for Multi-threaded Programs<br>Corneliu Popeea and Andrey Rybalchenko                                            | 237 |

| Deciding Conditional Termination<br>Marius Bozga, Radu Iosif, and Filip Konečný                                                                   | 252 |

#### **Internet Protocol Verification**

| The AVANTSSAR Platform for the Automated Validation of Trust  |     |

|---------------------------------------------------------------|-----|

| and Security of Service-Oriented Architectures 2              | 267 |

| Alessandro Armando, Wihem Arsac, Tigran Avanesov,             |     |

| Michele Barletta, Alberto Calvi, Alessandro Cappai,           |     |

| Roberto Carbone, Yannick Chevalier, Luca Compagna,            |     |

| Jorge Cuéllar, Gabriel Erzse, Simone Frau, Marius Minea,      |     |

| Sebastian Mödersheim, David von Oheimb, Giancarlo Pellegrino, |     |

| Serena Elisa Ponta, Marco Rocchetto, Michael Rusinowitch,     |     |

| Mohammad Torabi Dashti, Mathieu Turuani, and Luca Viganò      |     |

|                                                               |     |

| Reduction-Based Formal Analysis of BGP Instances 2            | 283 |

Anduo Wang, Carolyn Talcott, Alexander J.T. Gurney, Boon Thau Loo, and Andre Scedrov

## Stochastic Model Checking

| Minimal Critical Subsystems for Discrete-Time Markov Models<br>Ralf Wimmer, Nils Jansen, Erika Ábrahám, Bernd Becker, and<br>Joost-Pieter Katoen | 299 |

|--------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Automatic Verification of Competitive Stochastic Systems<br>Taolue Chen, Vojtěch Forejt, Marta Kwiatkowska,<br>David Parker, and Aistis Simaitis | 315 |

| Coupling and Importance Sampling for Statistical Model Checking<br>Benoît Barbot, Serge Haddad, and Claudine Picaronny                           | 331 |

| Verifying pCTL Model Checking<br>Johannes Hölzl and Tobias Nipkow                                                                                | 347 |

| Synthesis                                                                                                                                        |     |

| Parameterized Synthesis<br>Swen Jacobs and Roderick Bloem                                                                                        | 362 |

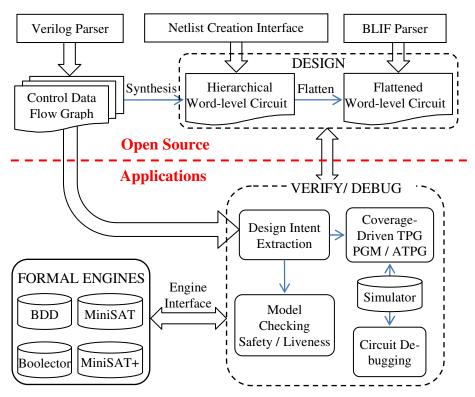

| QuteRTL: Towards an Open Source Framework for RTL Design<br>Synthesis and Verification                                                           | 377 |

| Template-Based Controller Synthesis for Timed Systems<br>Bernd Finkbeiner and Hans-Jörg Peter                                                    | 392 |

## Provers and Analysis Techniques

| Zeno: An Automated Prover for Properties of Recursive Data                          |     |

|-------------------------------------------------------------------------------------|-----|

| Structures                                                                          | 407 |

| William Sonnex, Sophia Drossopoulou, and Susan Eisenbach                            |     |

| A Proof Assistant for Alloy Specifications                                          | 422 |

| Reachability under Contextual Locking                                               | 437 |

| Bounded Phase Analysis of Message-Passing Programs Ahmed Bouajjani and Michael Emmi | 451 |

## **Tool Demonstrations**

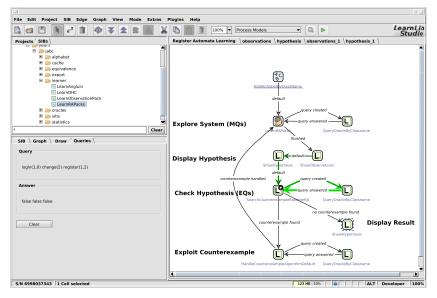

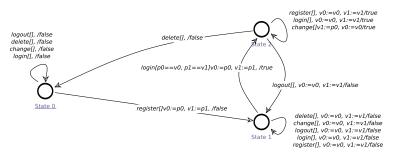

| Demonstrating Le | earnir | ng of Re | gister Aut | omata    |       |         |     | 466 |

|------------------|--------|----------|------------|----------|-------|---------|-----|-----|

| Maik Merten,     | Falk   | Howar,   | Bernhard   | Steffen, | Sofia | Cassel, | and |     |

| Bengt Jonsson    |        |          |            |          |       |         |     |     |

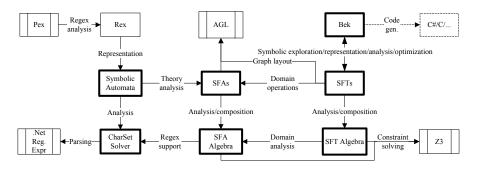

| Symbolic Automata: The Toolkit<br>Margus Veanes and Nikolaj Bjørner                                                                                                                | 472 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

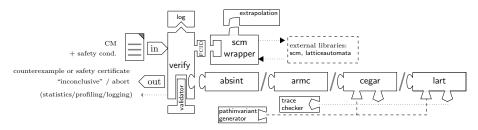

| McScM: A General Framework for the Verification of Communicating<br>Machines                                                                                                       | 478 |

| SLMC: A Tool for Model Checking Concurrent Systems against<br>Dynamical Spatial Logic Specifications<br>Luís Caires and Hugo Torres Vieira                                         | 485 |

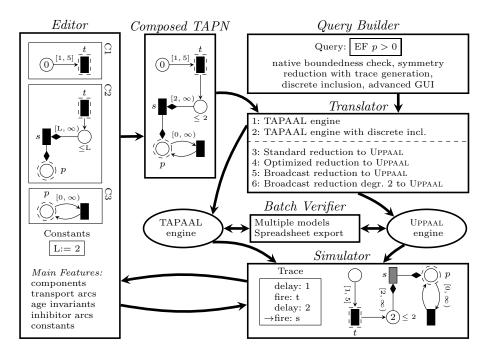

| TAPAAL 2.0: Integrated Development Environment for Timed-ArcPetri NetsAlexandre David, Lasse Jacobsen, Morten Jacobsen,<br>Kenneth Yrke Jørgensen, Mikael H. Møller, and Jiří Srba | 492 |

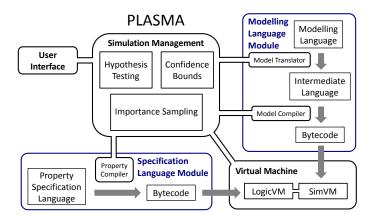

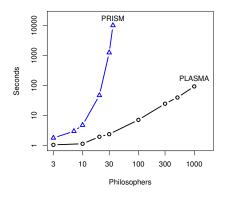

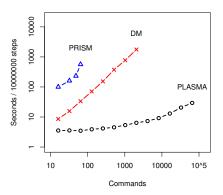

| A Platform for High Performance Statistical Model<br>Checking – PLASMA<br>Cyrille Jegourel, Axel Legay, and Sean Sedwards                                                          | 498 |

| Competition on Software Verification                                                                                                                                               |     |

| Competition on Software Verification (SV-COMP)<br>Dirk Beyer                                                                                                                       | 504 |

| Predicate Analysis with BLAST 2.7 (Competition Contribution)<br>Pavel Shved, Mikhail Mandrykin, and Vadim Mutilin                                                                  | 525 |

| CPACHECKER with Adjustable Predicate Analysis<br>(Competition Contribution)<br>Stefan Löwe and Philipp Wendler                                                                     | 528 |

| Block Abstraction Memoization for CPAchecker   |     |

|------------------------------------------------|-----|

| (Competition Contribution)                     | 531 |

| Daniel Wonisch                                 |     |

|                                                |     |

| Context-Bounded Model Checking with ESBMC 1.17 |     |

| (Competition Contribution)                     | 534 |

| Luca | s Cordeiro, | Jeremy Morse | e, Denis Nicole, | and Bernd Fischer           |     |

|------|-------------|--------------|------------------|-----------------------------|-----|

| Andr | eas Holzer  | <i>v</i> 0   | ning, Christian  | n Contribution) Schallhart, | 538 |

| LLBMC: A Bounded Model Checker for LLVM's Intermediate |     |

|--------------------------------------------------------|-----|

| Representation (Competition Contribution)              | 542 |

| Carsten Sinz, Florian Merz, and Stephan Falke          |     |

| Predator: A Verification Tool for Programs with Dynamic Linked Data<br>Structures (Competition Contribution)                               | 545 |

|--------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Kamil Dudka, Petr Müller, Petr Peringer, and Tomáš Vojnar                                                                                  |     |

| HSF(C): A Software Verifier Based on Horn Clauses                                                                                          |     |

| (Competition Contribution)<br>Sergey Grebenshchikov, Ashutosh Gupta, Nuno P. Lopes,<br>Corneliu Popeea, and Andrey Rybalchenko             | 549 |

| SatAbs: A Bit-Precise Verifier for C Programs                                                                                              |     |

| (Competition Contribution)<br>Gérard Basler, Alastair Donaldson, Alexander Kaiser,<br>Daniel Kroening, Michael Tautschnig, and Thomas Wahl | 552 |

| WOLVERINE: Battling Bugs with Interpolants                                                                                                 |     |

| (Competition Contribution)<br>Georg Weissenbacher, Daniel Kroening, and Sharad Malik                                                       | 556 |

| Author Index                                                                                                                               | 559 |

## Quantitative Models for a Not So Dumb Grid

Holger Hermanns

#### Dependable Systems and Software, Saarland University, Saarbrücken, Germany http://d.cs.uni-saarland.de/hermanns/

How to dimension buffer sizes in a network on chip? What availability can be expected for the Gallileo satellite navigation system? Is it a good idea to ride a bike with a wireless brake? Can photovoltaic overproduction blow out the European electric power grid? Maybe. Maybe not. Probably? The era of power-aware, wireless and distributed systems of systems asks for strong quantitative answers to such questions.

Stochastic model checking techniques have been developed to attack these challenges [2]. They merge two well-established strands of informatics research and practice: verification of concurrent systems and performance evaluation. We review the main achievements of this research strand by painting the landscape of behavioural models for probability, time, and cost, discussing important aspects of compositional modelling and model checking techniques. Different real-life cases show how these techniques are applied in practice.

A rich spectrum of quantitative analysis challenges is posed by the 'smart grid' vision [1,4]. That vision promises a more stable, secure, and resilient power grid operation, despite increasing volatility of electric power production. It is expected to come with more decentralized and autonomous structures, and with a lot of IT put in place to manage the grid. However, that vision is in its infancy, while the reality of power production is already changing considerably in some regions of Europe. We focus on a regulation put in place by the German Federal Network Agency to increase grid stability in case of photovoltaic overproduction. We show that this regulation may in fact decrease grid stability [3]. We also propose improved and fully decentralized stabilization strategies that take inspiration from probabilistic MAC protocols. Quantitative properties of these strategies are calculated by state-of-the-art stochastic model checking tools.

#### References

- 1. Amin, M.: Smart grid: Overview, issues and opportunities: Advances and challenges in sensing, modeling, simulation, optimization and control. In: IEEE Conference on Decision and Control and European Control Conference (2011)

- 2. Baier, C., Haverkort, B., Hermanns, H., Katoen, J.-P.: Performance evaluation and model checking join forces. Communications of the ACM 53(9), 74–83 (2010)

- 3. Berrang, P., Bogdoll, J., Hahn, E.M., Hartmanns, A., Hermanns, H.: Dependability results for power grids with decentralized stabilization strategies. Reports of SFB/TR 14 AVACS - ATR 83 (2012), http://www.avacs.org

- 4. Hermanns, H., Wiechmann, H.: Future design challenges for electric energy supply. In: IEEE International Conference on Emerging Technologies & Factory Automation (2009)

## History-Aware Data Structure Repair Using SAT

Razieh Nokhbeh Zaeem<sup>1</sup>, Divya Gopinath<sup>1</sup>, Sarfraz Khurshid<sup>1</sup>, and Kathryn S. McKinley<sup>2</sup>

<sup>1</sup> The University of Texas at Austin

Abstract. Data structure repair corrects erroneous executions in deployed programs while they execute, eliminating costly downtime. Recent techniques show how to leverage specifications and a SAT solver to enforce specification conformance at runtime. While this powerful methodology increases the reliability of deployed programs, scalability remains a key technical challenge-satisfying a specification often results in the exploration of a huge state space. We present a novel technique, called history-aware contract-based repair for more efficient data structure repair using SAT. Our insight is two-fold: (1) the dynamic program trace of field writes and reads provides useful guidance to repair incorrect state mutations by a faulty program; and (2) we show how to execute SAT using unsatisfiable cores it generates, in an efficient iterative approach on successive problems with increasing state spaces, in order to utilize the history of previous runs as captured in the unsatisfiable core. We implement this approach in a new tool, called Cobbler, that repairs Java programs. Experimental results on two large applications and a library implementation of a linked list show that Cobbler significantly outperforms previous techniques for specification-based repair using SAT, and finds and repairs a previously undetected bug.

#### 1 Introduction

Software systems are pervasive and integrated into almost every aspect of life. Software reliability is essential for life-critical, science, and business applications. Much research addresses producing reliable software in various phases of the software development life cycle before deployment, from analyzing requirements to design, implementation, and testing. However, improving the reliability of an already deployed (possibly faulty) system using error recovery is a less explored area.

In practice, systems are deployed with unknown and known unfixed bugs. When bugs cause failures, the usual tactic is to restart the program because fixing bugs and redeploying software may take months. Although the latter approach may resolve the fundamental source of the problem, system downtime is undesirable and not always feasible. Many *mission critical applications* such as operating systems, may prefer to trade slight deviations in intended functionality for system uptime. Better still, if developers annotate programs with specifications, then the runtime may restore the system state to provide its intended functionality. Continuing program execution by fixing the effect of bugs on-the-fly is called *repair*. Existing techniques for repair have not so far lived up to their full potential, because they are either not general purpose or too inefficient.

<sup>C. Flanagan and B. König (Eds.): TACAS 2012, LNCS 7214, pp. 2–17, 2012.

© Springer-Verlag Berlin Heidelberg 2012</sup>

Some critical systems include code that repairs erroneous executions on-the-fly using dedicated application specific repair routines [6,7,13,14]. Recent work introduced general purpose approaches including constraint-based repair [4, 8, 10] and contract-based repair [18, 25], some of which utilize SAT solvers [18, 25]. Constraint-based repair emphasizes data structure integrity rules and repairs the data structures when a bug leads to an invariant violation. Contract-based repair adds pre- and post-condition specifications of a method which aid in generating an accurate repair, i.e., a structure that is the same or very close to the one that a correct method would generate. General purpose repair, however, has a huge state space of possible post-states and exploring them to find a solution is currently too expensive to use in practice.

This paper seeks to make repair substantially more efficient by utilizing the *history* of code execution as well as SAT solving. Our insights are two-fold: (1) the dynamic program trace of field writes and reads provides useful guidance to identify incorrect state mutations made by a faulty program; and (2) the unsatisfiable core generated by a SAT run captures core elements of the solver's reasoning, which not only facilitates locating faults but can even be leveraged directly to optimize a successive SAT run. We utilize program traces and unsatisfiable cores in tandem to define an efficient iterative methodology where SAT is run on successive problems with increasing state spaces and each run utilizes the history of the previous run. To our knowledge, our work is the first to use the history of program execution or constraint solving in data structure repair.

History-aware repair utilizes a faulty program execution by focusing repair on fields recently modified or read by the program, thereby reducing the search space for SAT. We record program writes and reads to the key data structure with *barriers*. A barrier is a code sequence that performs an action just prior to a write or read. Barriers are widely available in commercial and research implementations of managed languages, e.g., the HotSpot and Jikes RVM Java Virtual Machines, and the .NET C# system. Our approach inserts barrier instrumentation on writes and reads or piggybacks on existing barriers.

While using the history of program execution aids in improving repair performance, its heuristic nature implies that there exist cases in which we have to perform a broader search and consider fields not included in the execution trace. In such cases, we take advantage of *UNSAT* cores, which are minimal unsatisfiable sub-formulas provided by failed SAT invocations. When SAT invocations fail, we utilize their UNSAT cores to identify faulty fields. A final SAT invocation with the list of faulty fields extracted from the UNSAT core results in a repaired data structure.

We implement repair for Java in a tool called Cobbler. Cobbler uses class invariants and method post-conditions expressed in the Alloy specification language [9]. Cobbler inserts write and read instrumentation for the specified data structures to log dynamic program behavior. When Cobbler detects a violation, it uses a SAT solver to mutate the data structure until it satisfies the specification.

We explore the efficiency and accuracy of Cobbler on microbenchmarks and two open source programs: Kodkod solver [22] and ANTLR [2,16]. We compare our history-aware contract-based repair tool, Cobbler, to contract-based repair alone using PBnJ [18] and Tarmeem [25], two repair tools which leverage user guides and heuristics along with a SAT solver. Cobbler is substantially more efficient and scalable than PBnJ and Tarmeem. We also compare Cobbler with Juzi, which uses data structure

specifications for repair, but does not use method post-conditions [5]. Juzi's dedicated constraint solver is more efficient than Cobbler, but Juzi's repair is applicable to far fewer cases and Cobbler is much more accurate. Our experiments show that for small to moderate instantiations of data structures, Cobbler provides repaired data structures which are 100% to 90% similar to the correct structure in more than 90% of the cases. Cobbler also finds and repairs a previously unknown error in ANTLR.

We make the following contributions: **History-aware contract-based repair** combines the program's dynamic behavior with specifications and the current erroneous state of a program to perform repair. **Read and write barriers for repair** are an unconventional use of barriers to obtain program execution history for repair. **Minimal unsatisfiable cores** provided by SAT solvers help to reduce the search space when a field outside the execution trace should be modified. **Cobbler** is an automated portable framework for repairing Java programs that enhances real applications with repair functionality. **Evaluation** shows that Cobbler efficiently and accurately repairs text-book examples and real world programs. Cobbler's more efficient and accurate repair facilitates the use of repair in real world applications and enhances software reliability.

#### 2 Background

This section describes data structure repair and the Alloy tool-set, which Cobbler uses.

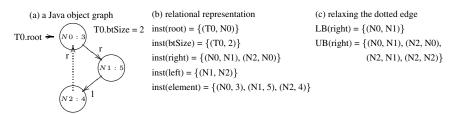

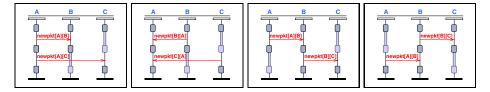

**Repair:** Data structure repair corrects erroneous executions on-the-fly by enforcing data integrity constraints (also known as repOK) and method pre- and post-conditions (contracts). Figure 1 (a) shows the faulty output of a method, which violates the acyclicity constraint as a binary search tree. A repair tool detects the violation and fixes it by removing the dotted edge. Further fixes may be needed to enforce method contracts too.

Alloy tool-set: Alloy is a relational first order logic language [9]. An Alloy model consists of relations and constraints on them. The Alloy Analyzer performs bounded exhaustive analysis of Alloy models. A *bound* is a function which maps each relation to a set of tuples (bound:  $R \rightarrow 2^T$ ), where each tuple consists of atoms. For each relation R, two sets are defined: a lower bound LB(R), which includes all tuples that R must have in its instance (inst(R)), and an upper bound UB(R), which includes all tuples that R may have in its instance. Therefore,  $LB(R) \subseteq inst(R) \subseteq UB(R)$ . Figure 1 (b) shows the relational representation of the Java object graph shown in Figure 1 (a).

We use Kodkod [22], the back-end of Alloy Analyzer, which is a SAT-based constraint solver for first order logic that supports relations, transitive closure, and partial

Fig. 1. Relational representation of data structures in Alloy models

models. Kodkod provides a finite model for satisfiable specifications and an UNSAT core for unsatisfiable ones. To perform repair, Kodkod suggests mutations to the data structure such that it meets the Alloy specification. Specifically, given a satisfiable relational formula and the bounds, Kodkod uses a backtracking search to find a satisfying instance. The search space is typically exponential in the number of atoms.

Kodkod allows explicit specification of upper and lower bounds for analysis, which provides partial solutions and restricts the search space. We use this functionality to specify which fields of the state can be mutated by the SAT solver to perform repair. Thus, to *relax* a field in Kodkod means to let the SAT solver suggest different values other than the one present in the faulty post-state, in order to find a satisfiable answer. Relaxing a field, which is a mutation of a field of a specific object, is done through binding a relation to suitable lower and upper bounds. For example, in Figure 1 (a) the dotted edge can be relaxed by setting the lower and upper bounds as shown in Figure 1 (c). Setting both lower and upper bounds to the same set makes it the only answer for that relation, i.e., the set becomes a partial solution for the Kodkod model.

**Minimal Unsatisfiable Cores:** If Kodkod cannot satisfy the constraints in a model, it produces a minimal unsatisfiable core, which is a subset of the constraints of the model. Given an unsatisfiable CNF formula X, a minimal unsatisfiable sub-formula is a subset of X's clauses that is both unsatisfiable and minimal, which means any subset of it is satisfiable. There could be many independent reasons for a formula's unsatisfiablity and hence more than one minimal core. The Recycling Core Extractor algorithm, implemented as the RCE Strategy in Kodkod, returns an unsatisfiable core of specifications written in the Alloy language that is guaranteed to be sound (constraints not included in the core are irrelevant to the unsatisfiability proof) and irreducible (removal of any constraint from the set would make the remaining formula satisfiable).

#### **3** Cobbler Framework

This section describes our history-aware contract-based repair framework.

#### 3.1 Overview

We use class invariants and method post-conditions to detect erroneous executions. Once an error is detected, we utilize two major sources of information about the intended behavior: the specification and the dynamic trace of execution which we obtain through write and read logs. Although the post-condition specifies the expected behavior of the method, there is often a wide range of correct possibilities for a given input since there may be many ways to implement the same specification. Additionally, for a SAT-based repair framework, relaxing all fields of the data structure explodes the search space and is infeasible for real world applications.

We use the program execution to help guide our repair process. In deployed software, the program is expected to contain most of the intended logic. Furthermore, given sufficient pre-deployment testing, there should not be many bugs in the code. By observing the dynamic behavior of a faulty execution, we can substantially reduce the size of the search space and make the repair process more efficient and effective. The core idea is to focus on fields modified and/or read during the execution. To obtain the execution history, we record write and read actions performed by the program. Our implementation instruments the program, but alternatively the Java Virtual Machine could efficiently provide them [1]. We start by restricting the SAT solver to correcting written fields and values, followed by read fields during the execution, and if the SAT solver has still not found a correction, it utilizes the UNSAT core provided by the previous SAT invocations to identify and mutate faulty fields of the data structure. Hence, our technique handles both errors of *commission* when the programmer writes an incorrect assignment and errors of *omission* when she forgets to update the required fields.

While repair has various applications, it does not suit all types of software systems. For systems that cannot tolerate even slight divergences in the state of the program from the original behavior (e.g, financial systems), it is not advisable to use automatic repair routines unless complete contracts with all the required details are available.

When repair is applicable, this approach has two benefits: (1) it improves the repair performance by reducing the size of the search space, and (2) it reduces the amount of data structure perturbation introduced by the repair process by focusing on fields that a correct method conceivably would modify.

Listing 1.1 shows the repair algorithm in pseudo-code. If an assertion is violated, the repair framework initially only mutates (relaxes) fields in the write log, holding all other data structure fields constant (through providing a partial solution for the SAT solver). It then calls the SAT solver to compute correct values for the relaxed fields. If this step does not yield a structure satisfying the contracts, the next step relaxes the fields in the read and write logs. If it still is unsuccessful, it relaxes fields appearing in the UNSAT core. If the SAT solver finds no solution, there is an inconsistency in the contract itself which the repair framework reports.

```

if (! assertContracts ()) {

1

2

relaxSAT (writeBarrierLog);

3

if (! assertContracts ()) {

4

relaxSAT(writeBarrierLog, readBarrierLog);

if (! assertContracts ()) {

5

relaxSAT(unsatCoreFields);

6

if (! assertContracts ()) {

7

reportModelInconsistency ();}}}

8

```

Listing 1.1. History-aware contract-based repair using read and write logs and unsatisfiable cores

#### 3.2 Example

Consider a binary search tree example written in Java in Listing 1.2 and its remove method. In Cobbler, developers must write a specification in the Alloy relational first order logic language. Listing 1.3 shows the acyclicity and size constraints that describe a correct binary search tree in Alloy. Additional constraints include search relations on the nodes and that the elements are unique. The repOK method describes all methodindependent constraints. The developer may also express method post-conditions, as shown in the remove\_postcondition method. This post-condition specifies a correct remove with respect to the data structure and the return value from the remove method.

```

1 class BinarySearchTree {

Node root; int btSize;

2

3

boolean remove(int x) {

4

if (root == null) return false;

5

else {

boolean result;

6

if (root.element == x) {

7

8

Node auxRoot = new Node();

auxRoot.left = root;

9

result = root.remove(x, auxRoot);

10

11

root = auxRoot.left;

} else result = root.remove(x, null);

12

if (result) btSize --;//using uniqueness of elements

13

14

return result;}}}

class Node {

15

16

Node left, right; int element;

boolean remove(int x, Node parent) {

17

if (x < element) {

18

if (left != null) return left.remove(x, this);

19

20

else return false;

} else if (x > element) {

21

if (right != null) return right.remove(x, this);

22

else return false;

23

24

else

if (left != null && right != null) {

25

element = right.minNode().element;

26

27

right.remove(element, this);

28

} else if (parent.left == this) {

29

if (left != null) parent.left = left;

else parent.left = right;

30

} else if (parent.right == this) {

31

if (left != null) parent.right = left;

32

//to introduce bug cycle replace with left.right = parent

33

else parent.right = right;}

34

35

return true;}}

36

Node minNode () \{\ldots\}

```

Listing 1.2. A binary search tree implementation in Java

```

1 abstract sig BinarySearchTree {

root, root': lone Node,

2

3

btSize, btSize': one Int}

л

abstract sig Node{

left, left', right, right': lone Node,

5

element, element': lone Int}

6

pred repOK(t: BinarySearchTree) { // class invariant

7

// directed acyclicity

8

all n: t.root'.*(left'+right')|n !in n.^(left'+right')

0

//size OK

10

11

# t.root'.*(left'+right') = int t.btSize'

12

//unique elements

13

14

//search property

15

. . . }

16 pred remove-postcondition (This: BinarySearchTree, x: Int, removeResult: (True+

False)){

17

repOK[This]

18

// correct remove

This.root.*(right+left).element - x = This.root'.*(right'+left').element'

19

20

// correct remove result

x in This.root.*(right+left).element <=> removeResult in True}

21

```

Listing 1.3. A binary search tree specification in Alloy

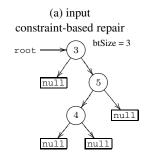

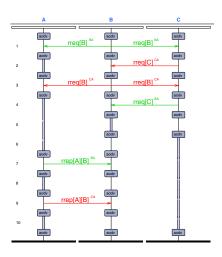

(b) expected output of remove (5) history-aware contract-based repair

(c) faulty output of remove (5)

(d) contract-based repair

(e) write barrier log (dotted lines in part (c)):

{[4].right, btSize}, [x] represents the node with value x before execution.

(f) read barrier log (dashed lines in part (c)):

{root, [3].element, [3].right, [5].element, [5].left, [5].right, [3].left}

Fig. 2. cycle manifested as a faulty output and the repair result

Alloy represents Java classes with signatures (e.g., sig BinarySearchTree in Listing 1.3) and field relations with a relational view. The keywords lone and one for a unary relation denote that the relation may or must not be empty, respectively. Binary relations can be defined as total or partial functions among other options (e.g., right is a partial function). We use the syntactic sugar of adding back-tick ('.') to distinguish post-state Alloy relations from pre-state relations. The Alloy repOK predicate (pred) expresses data structural integrity rules. For instance, the directed acyclicity constraint specifies that for any node reachable from root by applying zero or more left or right pointers, the node cannot reach itself by following one or more left or right pointers, so it cannot traverse a cycle.  $\star$  and ^ represent "zero or more" and "one or more" applications of a relation. Alloy supports membership, cardinality, and complement, in, #, and - respectively as in the acyclicity, size, and correct remove constraints.

To illustrate our repair process, consider inserting the following bug. **Bug cycle:** in Listing 1.2 line 32, replace the correct statement: parent.right = left with the incorrect: left.right = parent. For this incorrect implementation, after the method returns, checking the conjunction of repOK and the method post-condition indicates that there is an error, triggering the repair process.

To repair the erroneous output of the cycle faulty implementation, constraint-based repair methods [4, 8, 10] observe the cycle and remove it from Figure 2(c) to produce Figure 2(a), but fail to remove node 5. Contract-based repair techniques *without history* [18, 25] may generate Figure 2(d), which although a correct output, is different from what the program would have been generated in the absence of any bugs.

History-aware contract-based repair first invokes the SAT solver and tries to find a solution by only changing the values of the fields which the program writes into during the execution (Figure 2 (e)). These fields are distinguished by dotted lines in the faulty output. In this invocation, it does not find a solution because the program failed to update a field that needs to be modified. Our repair framework next considers changing fields read by the program (Figure 2 (f)) and shown as dashed lines. It invokes SAT to find suitable replacements for the fields written or read by the program. This invocation produces a repaired structure as shown in Figure 2 (b), which is identical to the expected output. Utilizing the barrier logs keeps us from generating Figure 2 (d) since the left field of node 4 is not relaxed and is held constant to be null. However, there remains a chance that a field that was not touched at all during the execution needs to be changed. Our repair framework obtains an UNSAT core from the previous SAT invocations. The UNSAT core is the conjunction of contradicting repOK and post-condition specifications, which were not satisfiable at the same time. In this example, if we were to proceed to the third SAT call, the UNSAT core would not include, for example, the correct remove result post-condition. Therefore, the final invocation of SAT would not relax the removeResult field.

#### 3.3 Implementation in Cobbler

Cobbler works as follows. (1) The user provides the Java data structure class and its methods. Cobbler instruments this code with setters and getters to obtain logs of the writes and reads. Cobbler also instruments the program for our experiments to measure the repair time, edit distance and other metrics. (2) Cobbler generates a stub for the repOK and method post-conditions for the Java class. Cobbler extracts class-specific relations, types, and properties into the stubs, and the user enhances them with the application specific logic. (3) Cobbler then instruments the program to check the post-conditions and call the repair method when needed. (4) The user executes the Java program inside the Cobbler framework.

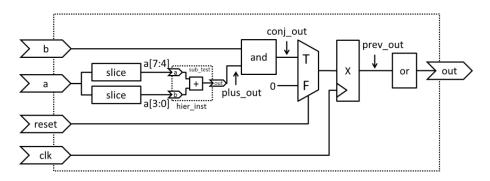

Figure 3 shows how the repair framework sits on top of the Java Virtual Machine and executes the Java program. The layers use shared memory to communicate. This design enhances the portability of our framework and makes it independent of JVM and the program. Alternative implementations could implement the framework inside the JVM, which would lower the overhead when pro-

**Fig. 3.** The relationship between Cobbler, the Java Virtual Machine, and the program

grams are correct. When programs need to be repaired, the SAT solving time is orders of magnitude bigger than time saved by merging the repair framework into JVM.

#### 4 Evaluation

The objectives of our evaluation are to empirically validate the hypothesis that using execution history and UNSAT cores improves the efficiency, accuracy, and scalability of contract-based repair with SAT solvers. To this end, we simulated various errors in microbenchmarks and examined two real world applications: Kodkod [22] and ANTLR [2, 16]. Cobbler discovered a previously unreported bug in the addChild method of ANTLR version 3.3 that resulted in a cycle in the output Tree. Our repair algorithm fixes this error accurately for a Tree with 300 nodes within 30 seconds.

Throughout the evaluation, we ran each experiment five times and reported the averages. All the experiments used a 2.50GHz Core 2 Duo processor with 4.00GB RAM running Windows 7 and Sun's Java SDK 1.6.0 JVM. All the repair frameworks used their default SAT solvers: Cobbler used MiniSat and MiniSatProver, Tarmeem used DefaultSAT4J, and PBnJ used MiniSat.

#### 4.1 Evaluation Metrics

To evaluate the efficiency of repair, we measured: (1) **logging time:** the overhead due to logging read and write actions; (2) **check time:** the time to detect a contract violation; and (3) **repair time:** the time to search and find a repaired data structure.

To evaluable the accuracy of repair, we measure the *edit distance* between the object graphs of the repaired data structure r, and the expected data structure e that a correct implementation would produce. Note that, r satisfies the method contract but might be different from the expected output. We define edit distance as the minimum number of edge additions/deletions to change a graph to another [19, 25]. We create the correct graphs by a separate correct implementation and then measure the edit distance in set difference operations between two graphs using the relational representation discussed in Section 2. Here  $inst_i(R)$  is the instance of relation R in data structure i.

#### **Definition 1.** $dist(e, r) = \sum_{R} (|inst_e(R) - inst_r(R)| + |inst_r(R) - inst_e(R)|).$

The lower this distance, the closer the repaired data structure is to the expected poststate data structure. We define the similarity percentage between the repaired output rand the expected output e as follows.

**Definition 2.**

$$sim(e,r) = (1 - \frac{dist(e,r)}{\sum_{R} |inst_e(R)|}) \times 100.$$

#### 4.2 Subject Programs

We applied Cobbler to (1) the remove method of Singly Linked List, (2) the insert method of the Kodkod.util.ints.IntTree class of the Kodkod solver implementation, and (3) the deleteChild and addChild methods of BaseTree of ANTLR.

**Singly-linked list:** Linked list is widely used and is a part of libraries such as java.util.Collection. The post-condition of the remove(int value) method, checks if the method has (1) deleted all nodes with elements equal to the input value, (2) maintained acyclicity, (3) inserted no new nodes, and (4) deleted no other nodes.

**Red-black tree of Kodkod:** Kodkod [22] is a SAT-based constraint solver for first order logic. It consists of 33,985 lines of Java code in 169 classes. The IntTree class with 570 lines of code and 21 methods sits at the core of the Kodkod solver, and is a generic implementation of the red-black tree data structure. Red-black tree comprises complex data structure invariants which include binary search tree invariants: every node has at most two children, key values of the left subtree are smaller and those of the right subtree are greater than the node value, and the tree is acyclic. In addition, constraints are imposed on the color of each node to keep the tree balanced: every node is either red or black, every leaf node is black, no red node has a red parent and all paths from the root to a descendant leaf contain the same number of black nodes. The insert method of this class comprises 58 lines of code with 67 branch statements. The post-condition of the insert(int newKey) method checks if an element with the new key value has been added without adding or deleting any other elements.

**BaseTree of ANTLR:** We use ANTLR (ANother Tool for Language Recognition) from the DaCapo 2009 benchmark suite, version 9.12 [2, 16]. ANTLR builds language parsers, interpreters, compilers, and translators from grammars. It comprises 29,710 lines of Java code, and has a download rate of about 5,000 per month. Rich tree data structures represent language grammars and are the backbone of this application. The abstract class BaseTree is a generic tree implementation. Each tree instance maintains a list of successor children. The childIndex represents its position in the list. Each child node is a tree and points back to its parent. Every node may contain a token field that represents the payload of the node. Based on the documentation and the program logic, we derived invariants for the BaseTree data structure such as acyclicity through children references, accurate parent-child relationships, and correct values for child indices. The addChild(Tree node) and deleteChild(int childIndex) methods are the main functions used to build and manipulate all tree structures in ANTLR. The respective post-conditions check that nodes are added or deleted without any unwarranted perturbations to the other nodes.

#### 4.3 Errors

Table 1 enumerates all the inserted faults and, for ANTLR, a detected error. It explains the errors and displays the violated constraints. The accuracy and performance of the repair algorithm depends on which and how many fields are relaxed in each step, and the number of calls to the solver. The data structure size, size of the log, and size of violated constraint formula influence repair accuracy and efficiency. We explore these parameters with a range of errors that violate different constraints and appear in different program statements, such as incorrect field assignments, incorrect branch conditions, and errors of omission. The last column in the table indicates if the field(s) that needs to be corrected appear in the write barrier log (WB), read barrier log (RB), or neither (ALL fields).

The program logic and thus which fields Cobbler logs depends on the input structures. Faults five and six of the red-black tree insert method execute the same faulty code versions as that of three and four, but with a different data structure. The program writes and reads different fields on the first and second inputs and Cobbler repairs the outputs by relaxing read and written fields respectively.

| Method                                                                        | Fault description                                                                                                                                                                                                                                                                                                                   | Violates                                                                                                                             | Error in                                             |

|-------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|

| Err 1<br>err 2<br>Err 2<br>Err 3<br>Err 4<br>Err 5<br>Err 6<br>Err 7          | Sets the header to null<br>Fails to update the size<br>Deletes a node with a non-matching element<br>Introduces a cycle after performing correct remove<br>Breaks the list to retain only the first two nodes<br>Deletes the matching element but adds it again<br>Fails to remove the element and updates the size incorrectly     | Correct remove, Size<br>Size<br>Correct remove, Size<br>Acyclicity<br>Correct remove, Size<br>Correct remove<br>Correct remove, Size | WB<br>ALL fields<br>WB<br>WB<br>WB<br>WB<br>WB<br>WB |

| Err 1<br><b>t</b> Err 2<br><b>e</b> Err 3<br><b>i</b> Err 4<br>Err 6<br>Err 7 | Creates a cycle of length one<br>Sets the color of a node to black instead of red<br>Adds the new element as right child instead of left<br>Violates key constraints due to a branch condition error<br>Same as Err 3 with a different input<br>Same as Err 4 with a different input<br>Skips balancing of the tree after insertion | Acyclicity<br>Color constraints<br>Key constraints<br>Key constraints<br>Key constraints<br>Key constraints<br>Color constraints     | WB<br>WB<br>RB<br>RB<br>WB<br>WB<br>ALL fields       |

| <b>ANTL</b><br><b>Bete Control</b><br>Etr 1<br>Etr 2<br>Etr 3<br>Etr 4        | Skips deletion of the appropriate child<br>Skips updating children indices after deletion<br>Sets a wrong child index due to an incorrect branch condition in a loop<br>Sets a node as its own parent                                                                                                                               | Correct Remove<br>Child Index constraints<br>Child Index constraints<br>Acyclicity                                                   |                                                      |

|                                                                               | Adds a node to itself as a child                                                                                                                                                                                                                                                                                                    | Acyclicity, Child Index                                                                                                              | WB                                                   |

#### Table 1. The injected faults and ANTLR addChild() fault

#### 4.4 Subject Tools

We compare Cobbler to Juzi repair framework, which only uses structural constraints, and to Tarmeem and PBnJ, two repair frameworks that consider post-conditions too.

Juzi's assertion-based repair automatically corrects data structure violations in Java programs [5]. Upon detecting a constraint violation, Juzi searches for a repair solution based on the data structure traversal encoded in repok [3]. Juzi further boosts its performance with symbolic execution. Since Juzi does not use a SAT solver, it is generally faster than SAT-based approaches. Juzi however does not consider method post-conditions, which causes it to miss errors that result in well-formed output. Even if repok is violated, without the post-condition, Juzi cannot accurately correct the structure with respect to the contracts as discussed in Section 3.2. To compare Juzi and Cobbler, we manually implemented a check for the post-condition in Juzi by recording the method pre-state and the desired data structure specific post-state.

Our previous work, Tarmeem, uses Alloy contracts and a SAT solver [25]. Tarmeem repairs faulty post-states using automated and user-guided techniques, such as iterative relaxation of relations and error localization in predicates to improve the efficiency of repair. We experimented with all four of Tarmeem's heuristics and picked the best.

Samimi et al. implement a similar technique in PBnJ that executes method specifications when methods fail to produce a correct data structure [18]. They express invariants and specifications in a declarative first order relational logic. Translating them into Java methods and then invoking the methods implements program logic declaratively. This program synthesis approach leverages constraint solving technology.

#### 4.5 Results

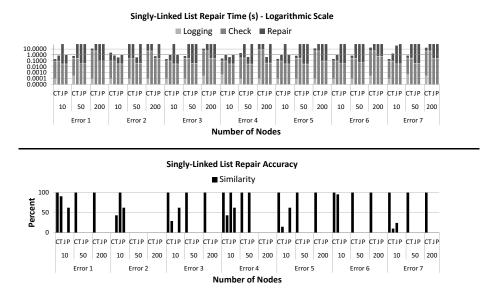

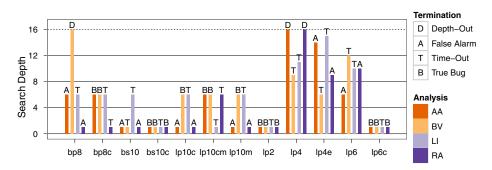

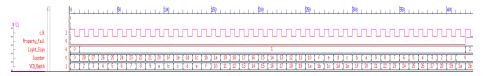

Figure 4 compares the performance and accuracy of repair of Cobbler, Tarmeem, Juzi, and PBnJ on the singly-linked list microbenchmark. Logging, check, and repair times

**Fig. 4.** Performance and accuracy: repairing singly-linked lists with Cobbler (C), Tarmeem (T), an enhanced version of Juzi (J), and PBnJ (P)

are accumulated into a single bar on a logarithmic scale. Logging time is only applicable to Cobbler and is negligible. Tarmeem and Cobbler have the same check time since they both use Kodkod evaluation (not SAT solving) to perform checks after methods execute. Juzi executes repok and PBnJ translates specifications to Java assertions, which more efficiently check the data structure. Cobbler's overhead on an error-free execution includes both logging and check times. Using the approach of PBnJ to translate specifications to assertions could reduce the check time and the total overhead. We timeout after 60 seconds and report zero for accuracy upon a timeout.

Cobbler is substantially faster than all the other tools on five of the seven errors, despite the fact that Tarmeem and PBnJ receive specific user annotations to guide the repair process and Juzi performs symbolic execution. Error two skips a required update to size. Since the size field is not read or written, Cobbler does not correct it until the third call to the SAT solver, which causes its time to exceed the other repair schemes. Error four introduces a cycle. Juzi is tailored for such errors: it satisfies the constraint by breaking cycles quickly and performs better than Cobbler in this case.

Cobbler, except for one case, always produces the most accurate data structure among the four. When Cobbler does not time out, it achieves exactly the same output as expected. The edit distance between the result of a correct implementation and the repaired data structure is zero. This comparison is solely for evaluation, since in the wild, the system would not know the correct implementation.

Because Juzi solely relies on the repOK method instead of checking method postconditions, it does not find error six at all. Moreover, Juzi cannot access out of scope nodes that are not reachable from the header. Since Juzi does not consider the execution

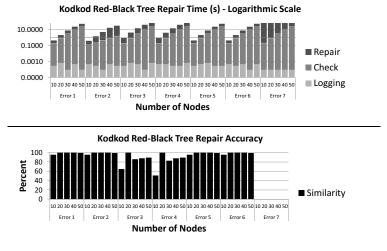

Fig. 5. Cobbler performance and accuracy: repairing Kodkod red-black trees

history, it first explores all the correct data structures nearby, but there is no guarantee that the expected output is close to the faulty one. We could enhance Juzi to work with post-conditions, as we did for evaluation of accuracy, but the original Juzi did not perform any repairs with respect to the post-conditions.

Tarmeem is not very accurate because when it invokes the SAT solver, it relaxes *all* tuples of a relation together, causing unnecessary changes. Cobbler significantly improves efficiency and accuracy over Tarmeem, especially for errors which involve incorrectly updated fields.

PBnJ's performance is similar to Tarmeem at best. The reason is that it always ignores the current faulty state and utilizes SAT to regenerate an acceptable output from scratch. It is however more accurate than Tarmeem in some cases.

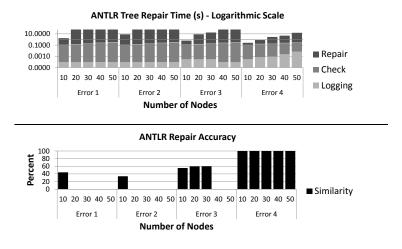

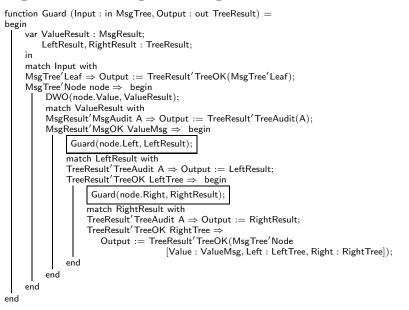

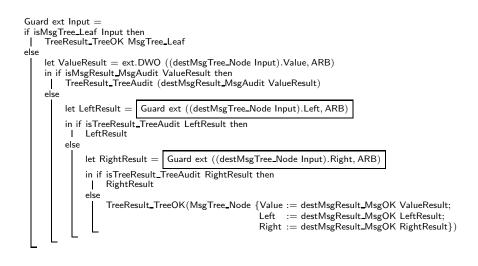

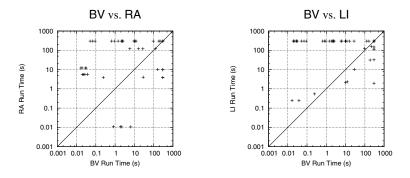

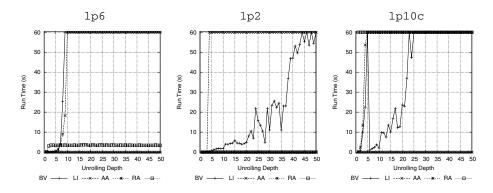

Figure 5 shows the performance and accuracy of Cobbler on a faulty Kodkod redblack tree insert method. Figure 6 depicts the results of experimenting with ANTLR. We do not include the other frameworks here for brevity. Juzi always fails to repair correctly when a contract requires the addition of a node and the node is not present, because Juzi only uses those nodes currently accessible from the faulty data structure. When it does not timeout, Cobbler is very accurate on these real world applications.

The results show that the read and write field logs improve the scalability and efficiency of repair. Cobbler repairs linked lists with up to 200 nodes within 20 seconds. It performs well even on more complex data structures. For the red-black tree remove method, it repairs up to 50 nodes within 40 seconds and for the deletechild method of ANTLR BaseTree, it repairs 40 nodes within 30 seconds. The size of the logs is proportional to the number of reads and writes to the data structure and was usually a few hundred bytes with a maximum of 900 bytes for error four of ANTLR.

For errors that cannot be fixed by relaxing only written and read fields, such as error two of linked list, error seven of red-black tree insert, and error two of ANTLR deleteChild (see Table 1), Cobbler uses the UNSAT core to identify which fields

Fig. 6. Cobbler performance and accuracy: repairing ANTLR trees

to modify, and performs better than the other SAT-based tools. These cases however are challenging for Cobbler, because despite barrier logs that indicate fields of specific objects, UNSAT cores identify all fields with the same name as potentially faulty.

#### 4.6 ANTLR BaseTree addChild

The public method addChild adds child node trees to an ANTLR BaseTree object. When the input tree does not have a payload (isNil), the method adds the children of the input tree to the children list of the current tree, otherwise, it adds the input tree itself to the children list. In the addChild method (v3.3), when the input tree does not have any payload, a check ensures that the current tree is not being added to itself. However, such a check is not performed for input trees with payloads. Hence, when the current tree has a payload, it may be added as a child of itself. Similarly, any tree with a payload which is already an existing child of the current tree may be added as a child again. We generated inputs that caused invariant (such as acyclicity and ascending child indices) violations. Cobbler repairs the Tree structure and restores it back to its pre-state, which is correct. This state would be the output of addChild if it had been implemented correctly. Cobbler repairs a tree with 300 nodes within 30 seconds.

#### 5 Related Work

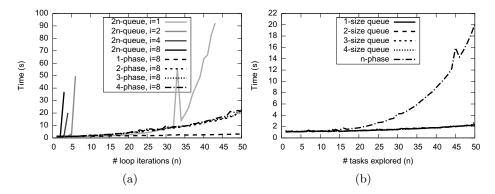

Dynamic repair aims to counteract faults at runtime and prolong system uptime. File system utilities such as fsck [6] and chkdsk [13], database check-pointing and rollback techniques are application-specific repair routines that monitor and correct system state at runtime. DIRA [20] extends database repair with post-conditions to detect buffer overflow attacks and fix damaged data structures. Clearview [17] and Exterminator [15] also aid in repairing memory errors at runtime, but none of these techniques are suitable for repairing general purpose complex data structures. On the other hand, some commercially developed systems, such as the IBM MVS operating system [14] and the Lucent 5ESS telephone switch [7], have dedicated routines for monitoring and maintaining properties of their key data structures. These systems are tailor-made for their system structures and cannot be generalized as data structure repair tools.