# A Multimetal Surface Micromachining Process for Tunable RF MEMS Passives

Yonghyun Shim, Student Member, IEEE, Zhengzheng Wu, Student Member, IEEE, and Mina Rais-Zadeh, Member, IEEE

Abstract—This paper reports on a microfabrication technology for implementing high-performance passive components suitable for advanced RF front-ends. This technology offers three metal layers with different thicknesses, one dielectric, and two sacrificial layers, enabling the fabrication of continuously tuned capacitors, capacitive and ohmic switches, as well as high-Q inductors all on a single chip. To demonstrate the versatility of this technology, several passive components are fabricated on a Borosilicate glass substrate ( $\varepsilon_r = 4.6$ ). A high-Q tunable capacitor is fabricated exhibiting an electrostatic tuning range of more than 6:1. The temperature variation of capacitance from 223 to 333 K is less than 9%, and the tuning speed is better than 80  $\mu$ s. To achieve a higher zero-bias capacitance, a tunable capacitor bank is also implemented, which can be tuned from 2.2 pF to 6.1 pF. In addition, a coupled inductor pair with self-inductances of 15 and 21 nH is implemented showing Qs exceeding 40 at 800 MHz. Measurements are compared with high frequency structure simulator (HFSS) electromagnetic simulations, showing good agreement. The technology reported is post-CMOS compatible and low cost. [2011-0331]

*Index Terms*—High quality factor, RF MEMS, surface micromachining, tunable passives, ultra high frequency.

# I. INTRODUCTION

THE POTENTIAL of RF microelectromechanical systems (MEMS) technology for implementing front-end components and modules with strict RF performance is already proven. Using micromachining technologies, individual RF components including antenna arrays [1], [2], matching network [3], [4], phase shifters [5], [6], single-input multipleoutput switches [7], [8], and band-select filters [9]–[12] are demonstrated. However, as each of the aforementioned RF modules requires diverse types of passives and as such poses different constraints on the fabrication technology, it is fabricated on a separate substrate and integrated with other parts in a system-in-package [13] or assembled on a printed circuit board [14], [15]. Compared with the system-on-chip, these approaches not only demand a larger area but are also more costly. In addition, the loss and parasitics of metal routings and bondwires required for chip-to-chip connections would be

The authors are with the Department of Electrical Engineering and Computer Science, University of Michigan, Ann Arbor, MI 48109 USA (e-mail: yhshim@umich.edu; zzwu@umich.edu; minar@umich.edu).

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/JMEMS.2012.2192911

major concerns, particularly at higher frequencies where they could significantly degrade the RF performance [16]. Therefore, a technology is needed that offers all possible RF passives, the building blocks of RF systems, on a single substrate at low cost. To this end, several issues must be addressed. First, such a technology must offer multiple metal layers to allow implementation of different passives, tunable or fixed, rigid, or compliant. Thick electroplated metals will be necessary for high-Q inductors, whereas thinner metals with low intrinsic stress will be needed for the released membrane of tunable capacitors and switches. Another consideration would be the selection of sacrificial layers and the release process for tunable components including air-suspended membranes. Last, a number of interlayer dielectrics with different properties might be needed for large-value metal-insulator-metal (MIM) capacitors or small-capacitance under-pass routings.

Philips Inc. has shown a fabrication technology for tunable capacitors using silicon dioxide and silicon nitride as the sacrificial layers and nature oxide of aluminum as the dielectric [17]. However, the breakdown voltage of the thin intrinsic aluminum oxide  $(Al_2O_3)$  is not sufficiently high, and thus the capacitors cannot sustain high RF powers. Researchers at Georgia Institute of Technology have shown a two metal micromachining process suitable for obtaining laterally tunable capacitors and high-Q inductors [10], [11]. While high-performance components were shown using this technology, the tuning bias voltage of the capacitors was high, as the same electroplated layer defined the tunable capacitors and thick inductors. A different process developed by University of Michigan for fabrication of switches utilized poly-methylmethacrylate (PMMA) as the sacrificial layer [18], but lacked thick metal processing, which is essential for co-integration of high-Q inductors.

In this paper, a surface micromachining process is reported that offers simultaneous fabrication of switches, tunable capacitors, fixed MIM capacitors, high-Q inductors, and coupled inductors. The performance and characterization results of several passives fabricated using this technology are demonstrated and compared with simulations. The proposed technology can be used to fabricate reconfigurable RF modules needed for multistandard radios [19].

# **II. FABRICATION PROCESS**

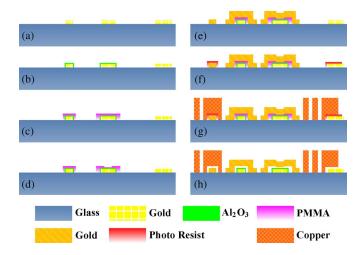

The fabrication process flow is schematically shown in Fig. 1. First, a metal layer consisting of  $300A^{\circ}Cr/5000A^{\circ}Au/300A^{\circ}Cr$  is deposited and patterned on borosilicate glass substrate using the lift-off process. This layer is used for bias

Manuscript received November 8, 2011; revised February 23, 2012; accepted March 18, 2012. This work was supported in part by Harris Corporation under the "Wide Tuning Range Integrated Filters for Tactical Radios" project and in part by the National Science Foundation under Grant #1055308. Subject Editor R. T. Howe.

Fig. 1. Fabrication process flow. (a) Au lift-off. (b)  $Al_2O_3$  deposition. (c) PMMA patterning. (d) PMMA thinning. (e) Au electroplating. (f) S1813 lithography. (g) Cu electroplating. (h) Release in acetone followed by CPD.

lines and bottom electrodes of tunable capacitors. Borosilicate glass is chosen because of its low RF loss. Though, the same fabrication process can be applied to other substrates, such as high resistivity and passivated CMOS-grade silicon. Next, a 1000A° thick Al<sub>2</sub>O<sub>3</sub> layer is deposited using an atomic layer deposition (ALD) tool with water vapor at 250 °C. ALD Al<sub>2</sub>O<sub>3</sub> is chosen as the inter-layer dielectric because of its high dielectric constant ( $\varepsilon_r$ ) of close to 10 and uniform side-wall coverage. The Al<sub>2</sub>O<sub>3</sub> is patterned using Transene aluminum etchant Type A at 50 °C.

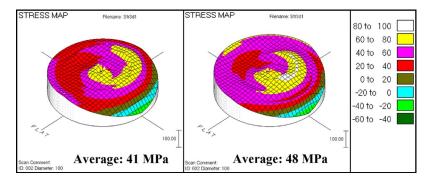

Next, a sacrificial layer is deposited and patterned. For the selection of the sacrificial layer, the following factors should be considered: the sacrificial layer should not be deformed or attacked during the subsequent processing steps, and its etchant during the release step should have good selectivity against other layers. Some commonly used sacrificial layers are polymers [20], [21], metals [22], [23], silicon dioxide [24], and amorphous silicon [25]. Amorphous silicon can be deposited with various methods such as plasma enhanced chemical vapor deposition (PECVD) or sputtering, and it is not easily attacked or deformed during the post processing steps [26]. The main problem with PECVD amorphous silicon is that it is hard to remove with either wet etchants such as KOH or dry etchants such as xenon difluoride (XeF<sub>2</sub>) [27]. Sputtered amorphous silicon is easier to remove with XeF<sub>2</sub>. However, the removal of sputtered amorphous silicon in XeF<sub>2</sub> is nonuniform; thereby, long etch time is needed to release the device. The long  $XeF_2$ release step results in increased stress in other metal layers on the wafer (in our case when the release time is increased beyond 15 min). Fig. 2 shows the stress distribution of a gold electroplated silicon wafer when 30 cycles (15 min) and 90 cycles (45 min) of  $XeF_2$  is applied, respectively. Each  $XeF_2$ cycle is composed of 30 s of gas flow step. The stress in the gold layer clearly increases upon long exposure to XeF<sub>2</sub>. Although the release condition is subjective to the deposition parameters and properties of the amorphous silicon layer as well as the  $XeF_2$  etch process, and one might characterize a recipe for better release of amorphous silicon, the increased stress in metal layers is hard to avoid. The initial value and the tuning characteristic of capacitive devices are highly dependent on the stress in the released metal film, and therefore, amorphous silicon was not chosen as the sacrificial layer in this process. Instead, uncured PMMA is used as the sacrificial layer. The main advantage of using uncured PMMA is that it can be easily removed in a relatively short time and without damaging other layers on the substrates. Alternatively, a metal could be used as the sacrificial layer. However, for a process consisting of three metal layers and several metal adhesions layers, it is unlikely to find a metal that its etchant is selective to all other metals on the wafer during release.

The PMMA patterning is done in three steps; first, PMMA is removed from unwanted areas. Next, it is thinned down in select areas in two steps to define two different gaps for the continuously tuned capacitors and capacitive switches.  $500A^{\circ}$  of TiW is used as a hard mask during the PMMA patterning process with O<sub>2</sub> plasma. TiW is subsequently removed in a hydrogen peroxide (H<sub>2</sub>O<sub>2</sub>) solution.

After sacrificial layer deposition and patterning, 4  $\mu$ m of gold layer is electroplated to form the top membrane of capacitors and the inductor interconnects. The gold layer is electroplated using the BDT-20 solution at 50 °C and with current density of 2 mA/cm<sup>2</sup>, an optimal processing condition for obtaining a uniform and low-stress film. The residual stress and stress gradient of the electroplated gold layer are extracted to be 40 MPa and 2 MPa/ $\mu$ m, respectively, using a microstrain gauge [28] and a cantilever included on the wafer.

After removal of the mold and seed layer, the inductors and thick routing layers are fabricated. Shipley 1813 photoresist is utilized as a sacrificial layer for creating air bridges between the electroplated gold (interconnection) layer and the thick electroplated copper layer (inductor and ground lines). A 35  $\mu$ m copper layer is electroplated using a 40  $\mu$ m thick AZ9260 photoresist mold. Finally, the sacrificial layers are removed using PRS2000 followed by acetone and the wafer is dried using critical point drier (CPD) to prevent stiction. Another possible release method is using O<sub>2</sub> plasma. However, long-time O<sub>2</sub> plasma can increase the substrate temperature and cause additional stress in the released membrane [29].

## **III. DESIGN AND MEASUREMENT RESULTS**

Tunable capacitors, capacitor banks, and inductors are designed and fabricated using the fabrication process outlined in Fig. 1. Unless otherwise stated, the fabricated passive components are measured using an N5241A Agilent PNA-X network analyzer and Cascade Microtech GSG Z-probes. Calibration is performed using the short-open-load-thru method.

#### A. Tunable Capacitor

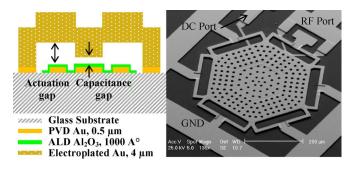

For the design of tunable capacitors, the specifications listed in Table I were targeted. A capacitor meeting these specifications allows the implementation of high-performance tunable filters such as the one presented in [19]. In this paper, the capacitors are electrostatically tuned, temperature stable, and have separate RF and dc electrodes for better power handling as well as more convenient tuning. The layout of the tunable capacitor is schematically shown in Fig. 3 (left). For continuously SHIM et al.: MULTIMETAL SURFACE MICROMACHINING PROCESS FOR TUNABLE RF MEMS PASSIVES

Fig. 2. Residual stress distribution of a 2 µm thick gold layer electroplated on a silicon wafer after 30 cycles (left) and after 90 cycles of XeF<sub>2</sub> etch (right).

| TABLE I                                  |         |

|------------------------------------------|---------|

| TARGET SPECIFICATIONS OF THE TUNABLE CAR | PACITOR |

|                                          |         |

| Specifications                                                              | Target                  |  |  |

|-----------------------------------------------------------------------------|-------------------------|--|--|

| Configuration                                                               | One port                |  |  |

| Tuning-type                                                                 | Continuous / Switched   |  |  |

| Initial capacitance (C <sub>IN</sub> )                                      | 200 fF                  |  |  |

| Tuning range $(C_{FN}/C_{IN})$                                              | > 5                     |  |  |

| Quality factor $(Q)$                                                        | >100 @ 1GHz             |  |  |

| Operation range                                                             | up to 2 GHz             |  |  |

| Mechanical resonant frequency $(f_M)$                                       | >20 kHz                 |  |  |

| Maximum tuning bias (V <sub>T</sub> )                                       | <40 V                   |  |  |

| Temperature variation (C <sub>IN</sub> , C <sub>FN</sub> , V <sub>T</sub> ) | < 10 % (223 K ~ 333 K)  |  |  |

| Dimensions                                                                  | $<400	imes400\ \mu m^2$ |  |  |

Fig. 3. Layout of the tunable capacitor. Schematic diagram showing crosssection view (left) and top-down SEM view (right).

tuned capacitors (i.e., varactors), a dual-gap configuration is adopted (with an actuation to sense gap of 4 : 1) to overcome the pull-in limitation and achieve better linearity [26]. In switched capacitors, on the other hand, a 4 : 3 dual-gap ratio is used for better fabrication yield. The size of the entire membrane is decided by the center area for initial capacitance of 200 fF and the actuation area for maximum tuning bias of 40 V. The size of the center RF node is  $145 \ \mu m \times 145 \ \mu m$ , while the overall size of the top membrane is  $310 \ \mu m \times 310 \ \mu m$ . The actuation air gap is designed to be 2  $\ \mu m$ , considering the membrane size and the fabrication yield. Fig. 3 (right) shows a scanning electron microscope (SEM) view of a fabricated tunable capacitor.

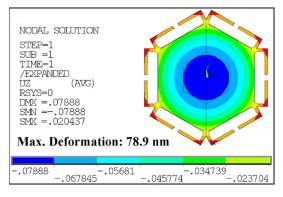

For the mechanical design of the capacitor, ANSYS finiteelement simulation software [30] is used, considering the residual stress (40 MPa) and stress gradient (2 MPa/ $\mu$ m) of gold extracted from measurements. Other material properties of the gold layer is set as 45 GPa (Young's modulus), 19.30 g/cm<sup>3</sup>

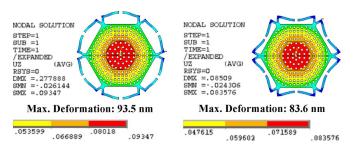

Fig. 4. Deformation of the hexagonal membrane upon 40 MPa of residual stress and 2 MPa/ $\mu$ m of stress gradient at room temperature (300 K).

(mass density), and 14.7 ppm/°C (thermal expansion coefficient), according to the published values for electroplated gold [31]. Two major specifications considered here are the mechanical resonant frequency  $(f_{\rm M})$  and the temperature stability of capacitance. For the springs, the geometrically compensated spring and anchoring design introduced in [32] was adopted. Prior work using this compensation technique utilized a squareshape membrane [32]. In this paper, a hexagon-shape membrane is selected since it offers a higher mechanical resonant frequency for a temperature stable design. Fig. 4 shows the room temperature deformation of the top membrane for a hexagonal design, having a resonant frequency of 23 kHz, when 40 MPa of residual stress and 2 MPa/ $\mu$ m of stress gradient are considered for the gold layer. This design shows a maximum deformation of less than 80 nm, which is relatively small compared to the capacitance air gap of 0.5  $\mu$ m.

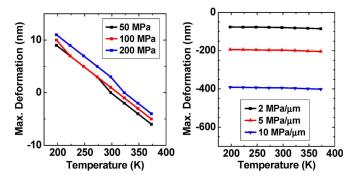

For the design shown in Fig. 4, the deformation of the gold membrane under different stress conditions is further analyzed. First, the deformation of the membrane with 50, 100, or 200 MPa of residual stress and no residual stress gradient is simulated over the temperature range of 198 K to 373 K. As shown in Fig. 5(a), the deformation is not affected by the residual stress and is less than 10 nm. Therefore, this hexagonal membrane design is very robust against residual stress and temperature variations. The second simulation is under 40 MPa of residual stress and different residual stress gradient of 2, 5, or 10 MPa/ $\mu$ m, respectively [Fig. 5(b)]. The deformation of the membrane is highly affected by the stress gradient. Thus, the stress gradient in the electroplated gold should be carefully controlled. Finally, the membrane deformation is simulated under the same stress conditions over the temperature range of

JOURNAL OF MICROELECTROMECHANICAL SYSTEMS

Fig. 5. Maximum deformation of the hexagonal membrane when temperature is varied from 198 K to 373 K: (a) under 50, 100, or 200 MPa of residual stress and (b) under 40 MPa of residual stress and 2, 5, or 10 MPa/ $\mu$ m of stress gradient.

Fig. 6. Deformation of the top membrane upon 40 MPa of residual stress and 2 MPa/ $\mu$ m of stress gradient at 223 K (left) and 333 K (right).

223 K to 333 K, as shown in Fig. 6. The temperature-induced change in the deformation of the central part, which defines the capacitive gap, is limited to 10 nm. The resulting change in the initial capacitance is thus less than 2.5%, proving that this design meets the target specification in terms of temperature stability.

To simulate the electrical properties, such as  $C_{\rm IN}$ ,  $C_{\rm FN}$ , and Q, the high frequency structure simulator (HFSS) 3-D electromagnetic tool [33] is utilized. The conductivity of copper and gold is taken as  $5.5 \times 10^7$  S/m and  $4.0 \times 10^7$  S/m in simulations, respectively. The properties of the substrate ( $\varepsilon_{\rm r} =$ 4.6 and tan  $\delta = 0.001$ ) are taken into account for accurate simulation of quality factor and self-resonant frequency (SRF). Accurate simulation of  $C_{\rm FN}$  during touch-down of the top membrane is difficult since it is dependent on various factors such as deformation of the top membrane, electrical properties and surface conditions of the dielectric layer, and the electrodes. To reflect these nonidealities,  $C_{\rm FN}$  is simulated using a reduced dielectric constant for the aluminum oxide dielectric layer, less than quarter of the bulk value. The dielectric loss (tan  $\delta$ ) of aluminum oxide is assumed to be 0.005.

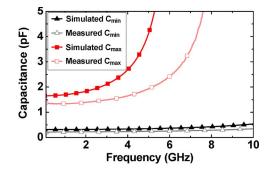

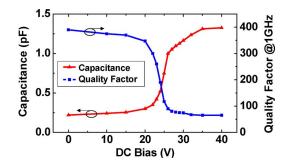

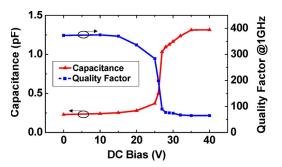

The simulated capacitance at the initial and final tuned states is shown in Fig. 7. The measured results of the tunable capacitors (varactors) are also shown on the same figure for easy comparison. The fabricated varactor is continuously tuned from 220 fF to 1.33 pF. The tuning range is slightly smaller than the simulated range of 300 fF to 1.7 pF. The discrepancy between the measured and simulated initial capacitance values can be due to the larger warping of the top membrane, which itself might be the result of a larger stress gradient in the electroplated gold layer. From the measured initial capacitance, around 0.2  $\mu$ m of membrane warping is expected, which corresponds

Fig. 7. Initial capacitance and maximum capacitance extracted from the HFSS simulation and measurement result, respectively.

Fig. 8. Q at initial and final states extracted from the HFSS simulation and measurement result, respectively.

Fig. 9. Measured tuning characteristics of the continuously tuned capacitor. At Stage 1, the air gap closes uniformly. At Stage 2 (after touch-down at 26 V), the membrane conforms to the substrate.

to a residual stress gradient of 4 MPa/ $\mu$ m. The smaller touchdown capacitance value is also due to the warping of the top membrane as well as the rough surface of the electrode.

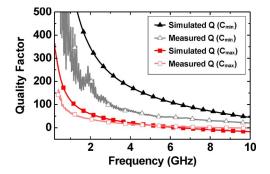

Fig. 8 shows simulated and measured Qs at the initial and final tuned states. The measured Q is higher than 65 at 1 GHz at all tuned states. The measured SRF is more than 13.5 GHz at the initial state and higher than 8.7 GHz at the final tuned state, which is similar to the simulated value. The measured Q is however lower than simulated value at low frequencies because of the lower conductivity of metals and higher dielectric loss of aluminum oxide compared to the values considered in the HFSS simulations. It is worth mentioning that accurate measurement of Qs in excess of 100 requires more complex measurement methods. One such method is to extract the Q from the bandwidth of a resonator implemented using the capacitor under test and an inductor with a known quality factor [34].

The tuning characteristics of the varactor and switched capacitor are compared in Figs. 9 and 10. Since both capacitors

Fig. 10. Measured tuning characteristics of the switched capacitor. At Stage 1, the air gap closes uniformly. At Stage 2 (after touch-down at 27 V), the membrane conforms to the substrate.

Fig. 11. Measured initial and final capacitance values as well as the maximum dc bias are stable within 5%, 7%, and 9% of their room temperature values.

have the same springs and membrane design and only different capacitance gap size, the final capacitance value and Q is very similar. However, the C-V trend shows a clear difference; the largest transition slope of the varactor is 0.25 pF/V while that of the switched capacitor is more than 0.5 pF/V. This is due to the larger actuation to sense gap ratio for the continuously tuned capacitor [17]. For both designs, the largest capacitance value is not achieved at the pull-in bias, but is reached at larger bias voltages close to 35 V at which the membrane is flattened with a larger actuation force. The warping in the membrane can be reduced with a more optimized gold electroplating process. The structural compensation can also be improved to allow better tolerance on the stress gradient.

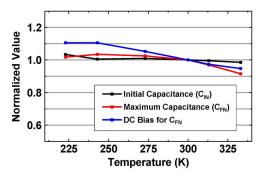

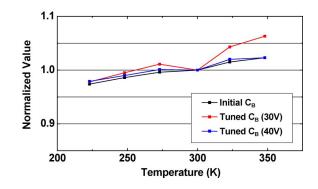

Fig. 11 shows variation of initial capacitance, maximum capacitance, and tuning bias over temperature range of 223 K to 333 K. Microtech KV-230 cryogenic station and GGB RF probes are used for these measurements. Calibration is redone at each temperature to remove the effect of the probes and cables. The initial and final capacitance values only show 5% and 7% variation, respectively, from the values at room temperature; whereas the required tuning bias shows larger variation of 9%. These results are consistent with ANSYS simulations; the deformation of the top membrane as a result of temperature change is small as the uniformly induced stress is well relieved, laterally.

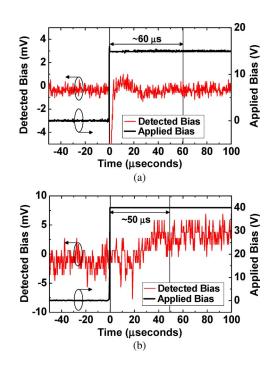

The tuning speed of the varactor is measured using the setup discussed in [26]. Fig. 12 shows the response of the capacitor (the detected output of the power detector) when 15 V and 40 V of tuning bias is applied, respectively. From the ringing seen in Fig. 12, the mechanical resonance frequency is extracted to be 25 kHz. The measured resonance frequency is in good

Fig. 12. Tuning speed measurement: (a) with 15 V of tuning bias and (b) with 40 V of tuning bias.

Fig. 13. Schematic view of the tunable capacitor array.

agreement with the ANSYS simulation results (i.e., 25 kHz measured versus 23 kHz simulated). The stabilization time is less than 80  $\mu$ s.

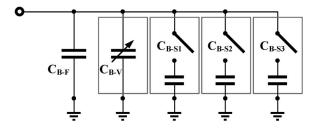

## B. Tunable Capacitor Bank

The tunable capacitor in the previous section has an initial capacitance of 200 fF. To increase the initial capacitance value, a tunable capacitor bank is designed, comprising of one fixed capacitor  $(C_{B-F})$ , one varactor  $(C_{B-V})$ , and three capacitive switches  $(C_{B-S})$  as shown in Fig. 13. The tuning mechanism is as following: first, the varactor is tuned to its maximum value; next a switch is turned on and the varactor is simultaneously released. For further tuning, the varactor is tuned again until it reaches its maximum value and the next switch is turned on. To achieve continuous tuning, the maximum capacitance of the switched capacitor is designed to be slightly smaller than that of the varactor. The reason to integrate a single varactor and multiple capacitive switches is to improve the fabrication yield and ease the tuning control.

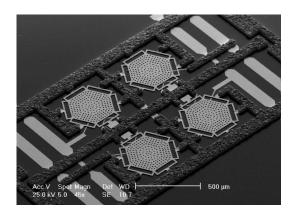

Fig. 14 shows a SEM view of a fabricated tunable capacitor array. The thick copper layer is utilized for routing between the capacitors in the bank and the ground ring in order to minimize

Fig. 14. SEM view of the fabricated tunable capacitor array.

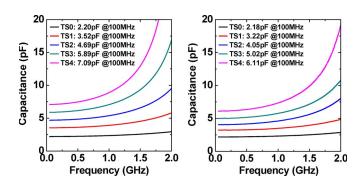

Fig. 15. Extracted capacitance of the tunable capacitor bank at each tuned state: simulation result (left) and measurement result (right).

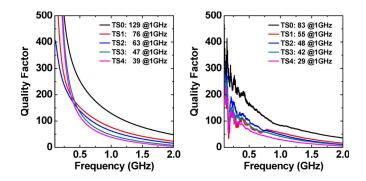

Fig. 16. Extracted Q of the tunable capacitor bank at each tuned state: simulation result (left) and measurement result (right).

RF losses. For insulation of the dc bias lines, 2  $\mu$ m air bridges are used between the ground and the bias lines. MIM capacitors are implemented using the two thick top metal layers. The MIM capacitors, with a higher capacitance density of 0.4 fF/ $\mu$ m<sup>2</sup> and higher Q compared to the varactors, are used to adjust the initial capacitance value.

The measured and simulated capacitance values at each tuned state are shown in Fig. 15. Tuning state N indicates that N numbers of tunable capacitors are completely tuned. The measured tuning range of capacitance is from 2.2 pF to 6.1 pF, which is smaller than the simulated value in HFSS (i.e., 2.2 pF to 7.1 pF). As described earlier, the membrane deformation and rough surfaces are the reasons for this discrepancy. As expected, the measured Q is also smaller than the simulated value (Fig. 16).

Fig. 17. Temperature variation measurements of the tunable capacitor bank; normalized value of the initial and tuned capacitance with 30 V and 40 V of dc bias.

The temperature variation is performed at different tuning states of the tunable capacitor bank (Fig. 17). Compared to the initial and final tuned states of the varactor, the intermediate tuned state at dc bias of 30 V shows more temperature sensitivity of up to 8.5% over temperature range of 223 K to 348 K.

Table II lists the specifications of recently published, highperformance, continuously tunable capacitors. In order to utilize the capacitor in RF front-ends, all performance aspects of the device need to be carefully addressed; some or none of which is considered for most reported tunable capacitors. These include tuning speed, initial capacitance value, Q, SRF, and temperature stability. The presented tunable capacitor exhibits high Q, high continuous tuning range, and good temperature stability. By placing such high-performance tunable capacitors in a bank, larger value continuously tuned capacitive elements are demonstrated. To our best knowledge, this is the highest performance capacitor bank that offers continuous tuning. Compared to other reported capacitor banks that are switched or digitally tuned [38], [39], the presented capacitor bank offers higher tuning resolution at the cost of lower Q and slower tuning speed.

## C. Coupled Inductors

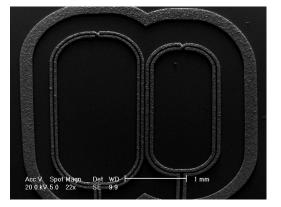

All inductors are designed using the two electroplated metal layers, Au and Cu, to obtain high Q and SRF. To reduce parasitic capacitance and enhance the SRF, the bottom interconnection layer (electroplated Au) is separated from the top copper layer using an air gap of 2  $\mu$ m. As a proof of concept, a mutually coupled inductor pair is designed. To achieve high Q(>40) and sufficient coupling constant (> 0.2), the planar configuration is used and the inductor shape adjusted to allow larger overlap. The fabricated coupled inductor pair is shown in Fig. 18.

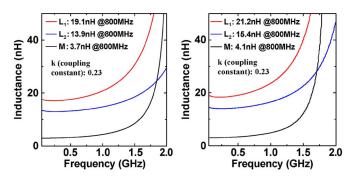

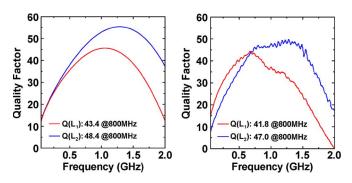

The simulated and measured inductance value is shown in Fig. 19. The extracted effective self-inductances  $(L_1, L_2)$  are larger than the simulated value because of larger capacitive parasitics. The measured coupling constant also shows slight difference with the simulated value, which might be due to the substrate characteristics and inaccuracy of simulations. The same trend is observed in the measured Q. Due to the larger

SHIM et al.: MULTIMETAL SURFACE MICROMACHINING PROCESS FOR TUNABLE RF MEMS PASSIVES

|                                           | Rijks '06 [17]            | McFeetors '06 [35]         | Mahameed '10 [36]                 | Shavezipur '10 [37] | This work<br>(a single varactor) | This work<br>(a capacitor bank) |

|-------------------------------------------|---------------------------|----------------------------|-----------------------------------|---------------------|----------------------------------|---------------------------------|

| Initial<br>Capacitance                    | 0.26 pF                   | 0.31 pF                    | 0.09 ~ 0.10 pF                    | 1.20 pF             | 0.22 pF                          | 2.18 pF                         |

| Tuning Ratio                              | 4.5                       | 6.2                        | $2.8 \sim 3.3$                    | 10.5                | 6.0                              | 2.8                             |

| Quality Factor<br>(at down-state<br>Cap.) | > 100 @ 4 GHz,<br>1.17 pF | > 100 @ 20 GHz,<br>1.40 pF | > 100 @ 5 GHz,<br>0.29 to 0.31 pF | N / A               | > 65 @ 1 GHz,<br>1.33 pF         | > 50 @ 600 MHz,<br>6.11 pF      |

| Tuning Speed                              | < 400 µs                  | N / A                      | N / A                             | N / A               | < 100 µs                         | < 100 µs                        |

| Max. Bias                                 | 30 V                      | 45 V, 80 V                 | 75 ~ 80 V                         | 40 V                | 35 V                             | 35 V                            |

| Temperature<br>Stability                  | < 20%                     | N / A                      | < 10%                             | N / A               | < 9%                             | < 9%                            |

TABLE II

Comparison Between the High-Performance Continuously Tunable Capacitors

Fig. 18. SEM view of the fabricated coupled inductors.

Fig. 19. Extracted inductance from simulation (left) and measurement (right).

Fig. 20. Extracted Q from simulation (left) and measurement (right). The drop of quality factor at 900 MHz is due to the substrate effects.

substrate loss and parasitics seen in the fabricated devices, the measured Q and SRF are slightly lower than the simulated values (Fig. 20).

#### **IV. CONCLUSION**

A surface micromachining technology is described which allows fabrication of high-performance RF passive components at low temperature and low cost. Several high-performance components were developed, including a tunable capacitor bank and a coupled inductor pair. The presented passive components can be utilized as a part of the RF front-end systems such as tunable antennas, phase shifters, matching networks, and tunable band selection filters. The presented fabrication technology can be extended to implement other passive components and circuits.

#### REFERENCES

- [1] J. Schoebel, T. Buck, M. Reimann, M. Ulm, M. Schneider, A. Jourdain, G. J. Carchon, and H. A. C. Tilmans, "Design considerations and technology assessment of phased-array antenna systems with RF MEMS for automotive radar applications," *IEEE Trans. Microw. Theory Tech.*, vol. 53, no. 6, pp. 1968–1975, Jun. 2005.

- [2] L. Petit, L. Dussopt, and J. M. Laheurte, "MEMS-switched parasiticantenna array for radiation pattern diversity," *IEEE Trans. Antennas Propag.*, vol. 54, no. 9, pp. 2624–2631, Sep. 2006.

[3] Q. Shen and N. S. Barker, "Distributed MEMS tunable matching network

- [3] Q. Shen and N. S. Barker, "Distributed MEMS tunable matching network using minimal-contact RF-MEMS varactors," *IEEE Trans. Microw. The*ory Tech., vol. 54, no. 6, pp. 2646–2658, Jun. 2006.

- [4] Y. Lu, D. Peroulis, S. Mohammadi, and L. P. B. Katehi, "A MEMS reconfigurable matching network for a class AB amplifier," *IEEE Microw. Wireless Compon. Lett.*, vol. 13, no. 10, pp. 437–439, Oct. 2003.

- [5] S. Barker and G. M. Rebeiz, "Distributed MEMS true-time delay phase shifters and wide-band switches," *IEEE Trans. Microw. Theory Tech.*, vol. 46, no. 11, pp. 1881–1890, Nov. 1998.

- [6] A. Malczewski, S. Eshelman, B. Pillans, J. Ehmke, and C. L. Goldsmith, "X-band RF MEMS phase shifters for phased array applications," *IEEE Microw. Guided Wave Lett.*, vol. 9, no. 12, pp. 517–519, Dec. 1999.

- [7] S. P. Pacheco, D. Peroulis, and L. P. B. Katehi, "MEMS singlepole double-throw (SPDT) X and K-band switching circuits," in *IEEE MTT-S Int. Microw. Symp. Dig.*, 2001, vol. 1, pp. 321–324.

- [8] I.-J. Cho, T. Song, S.-H. Baek, and E. Yoon, "A low-voltage push-pull SPDT RF MEMS switch operated by combination of electromagnetic actuation and electrostatic hold," in *Proc. IEEE Int. Conf. Microelectromech. Syst.*, Feb. 2005, pp. 32–35.

- [9] K. Entesari and G. M. Rebeiz, "A 12–18-GHz three-pole RF MEMS tunable filter," *IEEE Trans. Microw. Theory Tech.*, vol. 53, no. 8, pp. 2566– 2571, Aug. 2005.

- [10] M. Rais-Zadeh and F. Ayazi, "Small-bandwidth integrated tunable bandpass filters for GSM applications," in *Proc. IEEE Int. Conf. Microelectromech. Syst.*, Jan. 2008, pp. 1032–1035.

- [11] M. Rais-Zadeh, H. M. Lavasani, A. Kapoor, and F. Ayazi, "An integrated 800-MHz coupled-resonator tunable bandpass filter in silver with a constant bandwidth," *J. Microelectromech. Syst.*, vol. 18, no. 4, pp. 942–949, Aug. 2009.

- [12] Y. Shim, R. Tabrizian, F. Ayazi, and M. Rais-Zadeh, "Low-loss MEMS band-pass filters with improved out-of-band rejection by exploiting inductive parasitics," in *Proc. IEEE Int. Electron Devices Meeting*, Dec. 2009, pp. 1–4.

#### JOURNAL OF MICROELECTROMECHANICAL SYSTEMS

- [13] K. L. Tai, "System-In-Package (SIP): Challenges and opportunities," in Proc. Asia South Pacific Design Autom. Conf., Jun. 2000, pp. 191–196.

- [14] B. A. Cetiner, J. Y. Qian, H. P. Chang, M. Bachman, G. P. Li, and F. De Flaviis, "Monolithic integration of RF MEMS switches with a diversity antenna on PCB substrate," *IEEE Trans. Microw. Theory Tech.*, vol. 51, no. 1, pp. 332–335, Jan. 2003.

- [15] R. Ramadoss, A. Sundaram, and L. M. Feldner, "RF MEMS phase shifters based on PCB MEMS technology," *Electron. Lett.*, vol. 41, no. 11, pp. 654–656, May 2005.

- [16] Z. Jiafeng, M. J. Lancaster, and H. Frederick, "Coplanar quarterwavelength quasi-elliptic filters without bond-wire bridges," *IEEE Trans. Microw. Theory Tech.*, vol. 52, no. 4, pp. 1150–1156, Apr. 2004.

- [17] T. G. S. M. Rijks, P. G. Stteneken, J. T. M. van Beek, M. J. E. Uleanaers, A. Jourdain, H. A. C. Tilmans, J. De Coster, and R. Puers, "Microelectromechanical tunable capacitors for reconfigurable RF architectures," *J. Micromech. Microeng.*, vol. 16, no. 3, pp. 601–611, 2006.

- [18] J. S. Hayden and G. M. Rebeiz, "Very low-loss distributed X-band and Ka-band MEMS phase shifters using metal-air-metal capacitors," *IEEE Trans. Microw. Theory Tech.*, vol. 51, no. 1, pp. 309–314, Jan. 2003.

- [19] Y. Shim, J. Ruan, Z. Wu, and M. Rais-Zadeh, "An integrated RF MEMS tunable filters," in *Proc. IEEE Int. Conf. Microelectromech. Syst.*, Jan. 29–Feb. 2, 2012, pp. 15–18.

- [20] C. L. Goldsmith, Y. Zhimin, S. Eshelman, and D. Denniston, "Performance of low-loss RF MEMS capacitive switches," *IEEE Microw. Guided Wave Lett.*, vol. 8, no. 8, pp. 269–271, Aug. 1998.

- [21] A. Bagolini, L. Pakula, T. L. M. Scholtes, H. T. M. Pham, P. J. French, and P. M. Sarro, "Polyimide sacrificial layer and novel materials for postprocessing surface micromachining," *J. Micromech. Microeng.*, vol. 12, no. 4, pp. 385–389, Jul. 2002.

- [22] P. M. Zavracky, S. Majumder, and N. E. McGruer, "Micromechanical switches fabricated using nickel surface micromachining," *J. Microelectromech. Syst.*, vol. 6, no. 1, pp. 3–9, Mar. 1997.

- [23] G. Songbin, S. Hui, and N. S. Barker, "A cryogenic broadband DC contact RF MEMS switch," in *IEEE MTT-S Int. Microw. Symp. Dig.*, Jun. 2009, pp. 1225–1228.

- [24] J. Buhler, F. P. Steiner, and H. Baltes, "Silicon dioxide sacrificial layer etching in surface micromachining," J. Micromech. Microeng, vol. 7, no. 1, pp. R1–R13, Mar. 1997.

- [25] S. Frederico, C. Hibert, R. Fritschi, P. Fluckiger, P. Renaud, and A. M. Ionescu, "Silicon sacrificial layer dry etching (SSLDE) for freestanding RF MEMS architectures," in *Proc. IEEE 16th Annu. Int. Conf. Micro Electro Mech. Syst.*, Jan. 2003, pp. 570–573.

- [26] Y. Shim, Z. Wu, and M. Rais-Zadeh, "A high-performance, temperaturestable, continuously tuned MEMS capacitor," in *Proc. IEEE Int. Conf. Microelectromech. Syst.*, Jan. 2011, pp. 752–755.

- [27] A. A. E. Stevens, M. C. M. van de Sanden, H. C. W. Beijerinck, and W. M. M. Kessels, "Roughening during XeF<sub>2</sub> etching of Si(100) through interface layers: H:Si(100) and a-Si/Si(100)," *J. Vac. Sci. Technol. A, Vac., Surf., Films*, vol. 27, no. 2, pp. 367–375, 2009.

- [28] L. Liwei, A. P. Pisano, and R. T. Howe, "A micro strain gauge with mechanical amplifier," *J. Microelectromech. Syst.*, vol. 6, no. 4, pp. 313– 321, Dec. 1997.

- [29] C.-W. Baek, Y.-K. Kim, Y. Ahn, and Y.-H. Kim, "Measurement of the mechanical properties of electroplated gold thin films using micromachined beam structures," *Sens. Actuators A, Phys.*, vol. 117, no. 1, pp. 17–27, Jan. 2005.

- [30] ANSYS, Inc., ANSYS 12, (2009). [Online]. Available: http://www. ansys.com/

- [31] T. C. Hodge, S. A. Bidstrup-Allen, and P. A. Kohl, "Stresses in thin film metallization," *IEEE Trans. Compon., Packag., Manuf. Technol., A*, vol. 20, no. 2, pp. 241–250, Jun. 1997.

- [32] H. Nieminen, V. Ermolov, S. Silanto, K. Nybergh, and T. Ryhanen, "Design of a temperature-stable RF MEM capacitor," *J. Microelectromech. Syst.*, vol. 13, no. 5, pp. 705–714, Oct. 2004.

- [33] ANSYS, Inc., ANSYS HFSS 12, (2009). [Online]. Available: http://www.ansoft.com/products/hf/hfss/

- [34] G. M. Rebeiz, *RF MEMS Theory, Design, and Technology*. New York: Wiley, 2003.

- [35] G. McFeetors and M. Okoniewski, "Performance and operation of stressed dual-gap RF MEMS varactors," in *Proc. EUMC*, Sep. 2006, pp. 1064–1067.

- [36] R. Mahameed and G. M. Rebeiz, "Electrostatic RF MEMS tunable capacitors with analog tunability and low temperature sensitivity," in *IEEE MTT-S Int. Microw. Symp. Dig.*, May 2010, pp. 1254–1257.

- [37] M. Shavezipur, P. Nieva, A. Khajepour, and S. M. Hashemi, "Development of parallel-plate-based MEMS tunable capacitors with linearized capacitance-voltage response and extended tuning range," *J. Micromech. Microeng.*, vol. 20, no. 2, pp. 1–8, Feb. 2010.

- [38] B. Lakshminarayanan, D. Mercier, and G. M. Rebeiz, "High-reliability miniature RF-MEMS switched capacitors," *IEEE Trans. Microw. Theory Tech.*, vol. 56, no. 4, pp. 971–981, Apr. 2008.

- [39] J. Muldavin, C. Bozler, S. Rabe, and C. Keast, "Large tuning range analog and multi-bit MEMS varactors," in *IEEE MTT-S Int. Microw. Symp. Dig.*, 2004, pp. 1919–1922.

**Yonghyun Shim** (S'09) received the B.S. degree in electrical engineering from Seoul National University, Seoul, Korea, in 2007, and the M.S.E. degree in electrical engineering and computer science from the University of Michigan, Ann Arbor, in 2009, where he is currently working toward the Ph.D. degree in electrical engineering and computer science.

His research interests include micromachined RF front-end filters, RF MEMS passives, RF IC and wireless front-end, and CMOS-MEMS integration.

Zhengzheng Wu (S'09) received the B.S. degree in microelectronics from Fudan University, Shanghai, China, in 2005, and the M.S. degree in microelectronics from the Shanghai Institute of Microsystem and Information Technology, Chinese Academy of Sciences, Shanghai, China, in 2009. He is currently working toward the Ph.D. degree in electrical engineering and computer science at the University of Michigan, Ann Arbor.

During the summer of 2011, he was an Intern with Samsung Telecommunications America, Dallas, TX,

where he was involved in developing multiband RF power amplifiers for wireless handsets. His research interests include microelectromechanical systems for wireless applications and timing references, tunable RF filters and passive circuits, circuits for wireless transceivers, and integrated microsystems.

Mr. Wu received the Rackham International Student Fellowship from the University of Michigan for 2010–2011. He was a student paper competition finalist at the 2011 International Microwave Symposium.

**Mina Rais-Zadeh** (S'03–M'08) received the B.S. degree in electrical engineering from Sharif University of Technology, Tehran, Iran, and the M.S. and Ph.D. degrees in electrical and computer engineering from Georgia Institute of Technology, Atlanta, in 2005 and 2008, respectively.

From August 2008 to 2009, she was a Postdoctoral Research Fellow with the Integrated MEMS Group, Georgia Institute of Technology, Atlanta. Since January 2009, she has been with the University of Michigan, Ann Arbor, where she is currently an Assistant

Professor in the Department of Electrical Engineering and Computer Science. Her research interests include passive micromachined devices for communication applications, resonant micromechanical devices, gallium nitride MEMS, and micro/nano fabrication process development.

Dr. Rais-Zadeh was the recipient of an NSF CAREER Award (2011), the IEEE Electron Devices Society Early Career Award (2011), and was a finalist in the student paper competitions at the SiRF (2007) and IMS (2011) conferences. She serves as a member of the Technical Program Committees of IEEE IEDM, IEEE Sensors, and the Hilton Head Workshop.

8