## Department of Computer Science

# Graphical User Interface for Compiler Optimizations with Simple-SUIF

Brian Harvey

Department of Computer Science

University of California

Riverside, CA 92521

briancs.ucr.edu

Gary Tyson

Department of Computer Science

University of California

Riverside, CA 92521

tysoncs.ucr.edu

UCR-CS-96-5

### Technical Report

## COLLEGE OF ENGINEERING UNIVERSITY OF CALIFORNIA RIVERSIDE

## UNIVERSITY OF CALIFORNIA RIVERSIDE

# Graphical User Interface for Compiler Optimizations with Simple-SUIF

A Thesis submitted in partial satisfaction of the requirements for the degree of

> Master of Science in Computer Science

by Brian Keith Harvey

December, 1996

#### Thesis Committee:

Professor Gary Tyson, Chairperson

Professor Thomas Payne

Professor Frank Vahid

Copyright by Brian Keith Harvey 1996

#### ABSTRACT OF THE THESIS

Graphical User Interface for Compiler Optimizations with Simple-SUIF

by

#### Brian Keith Harvey

Master of Science, Graduate Program in Computer Science

University of California, Riverside, December, 1996

Professor Gary Tyson, Chairperson

Very few tools exist which support the process of studying back end optimizations. Currently, researchers examining different back end optimizations must rely on general debugging tools or design their own tools to help in the generation of optimizing functions. A tool designed to give information specifically tailored for optimization designers is necessary. Such a tool would allow researchers to view the results of a newly designed optimization or analyze how the intermediate code of a program changes depending on the order in which transformations are applied. More efficient development of optimization routines should be the result of using this tool.

This thesis presents the Visual Simple-SUIF Compiler (VSSC) package, designed to accomplish these tasks by providing an interactive framework that facilitates the development of code transformations in the back end component of a compiler. Code transformation algorithms are viewed by *stepping* through the transformation while actual changes to the intermediate code are performed visually. Transformations can be applied to the intermediate code in any order and can

be *undone*. Capabilities such as these aid in the educational process of learning optimization algorithms and in the testing of newly developed optimizations.

A tool of this nature requires several key components that integrate well with each other to form a single framework. These components include: an easily extendible compiler with a simple, yet functional, intermediate format, a graphical user interface toolkit to implement the graphical "interactive" component of such a tool, and a subsystem for drawing graphs which are common data structures used in code transformations.

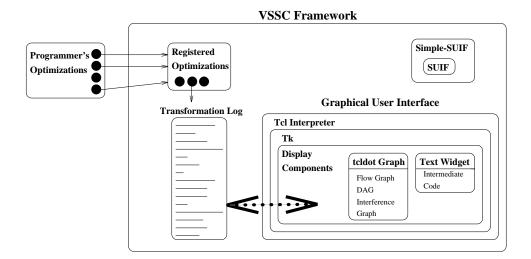

VSSC incorporates a graphical user interface (Tcl/Tk), the Simple-SUIF compiler framework, and the DOT graph drawing tool to visually illustrate data flow analysis and code transformations. VSSC has many advantages that make it useful to both optimization researchers and students alike.

The goal of this thesis to describe the design and implementation of a framework which integrates these components as well as outlining the benefits the use of a tool based on this framework provides.

## Contents

| 1 | Intr           | roduction                                | 1  |

|---|----------------|------------------------------------------|----|

|   | 1.1            | Front End                                | 2  |

|   | 1.2            | Intermediate Representation              | 3  |

|   | 1.3            | Back End                                 | 5  |

|   |                | 1.3.1 Constructing Code Optimizers       | 6  |

|   | 1.4            | Design Tools for Developing Optimizers   | 7  |

|   | 1.5            | VSSC                                     | 8  |

|   | 1.6            | Thesis Organization                      | 12 |

|   |                |                                          |    |

| 2 | $\mathbf{Ret}$ | argetable Compilers                      | 13 |

|   | 2.1            | Requirements for a Retargetable Compiler | 13 |

|   | 2.2            | GNU C Compiler (GCC)                     | 14 |

|   | 2.3            | LCC                                      | 15 |

|   | 2.4            | SUIF Compiler System                     | 17 |

|   |                | 2.4.1 SUIF Intermediate Format           | 18 |

|   |                | 2.4.2 SUIF Transformation Environent     | 19 |

|   |                | 2.4.3 Simple-SUIF                        | 21 |

|   | 2.5            | Summary                                  | 25 |

| 3 | Con | ompiler Visualization Tools 26       |    |  |  |  |  |  |

|---|-----|--------------------------------------|----|--|--|--|--|--|

|   | 3.1 | Graph Drawing Tools                  | 27 |  |  |  |  |  |

|   |     | 3.1.1 <b>VCG</b>                     | 27 |  |  |  |  |  |

|   |     | 3.1.2 dflo                           | 28 |  |  |  |  |  |

|   |     | 3.1.3 DOT                            | 29 |  |  |  |  |  |

|   | 3.2 | Visual Compiler Tools                | 29 |  |  |  |  |  |

|   |     | 3.2.1 Visual SUIF Browser            | 30 |  |  |  |  |  |

|   |     | 3.2.2 UW Illustrated Compiler        | 31 |  |  |  |  |  |

|   |     | 3.2.3 xvpodb                         | 32 |  |  |  |  |  |

|   | 3.3 | Summary                              | 34 |  |  |  |  |  |

| 4 | VSS | SC Design and Implementation         | 35 |  |  |  |  |  |

|   | 4.1 | Design Goals                         | 35 |  |  |  |  |  |

|   | 4.2 | Organization of VSSC Framework       | 38 |  |  |  |  |  |

|   | 4.3 | Implementation of VSSC               | 39 |  |  |  |  |  |

|   |     | 4.3.1 Graphical User Interface       | 39 |  |  |  |  |  |

|   |     | 4.3.2 Incorporating tcldot into VSSC | 44 |  |  |  |  |  |

|   |     | 4.3.3 SUIF                           | 45 |  |  |  |  |  |

|   |     | 4.3.4 Simple-SUIF                    | 47 |  |  |  |  |  |

|   |     | 4.3.5 Transformation Log             | 48 |  |  |  |  |  |

|   |     | 4.3.6 Undo Transformation            | 50 |  |  |  |  |  |

|   | 4.4 | Programmer Interface                 | 51 |  |  |  |  |  |

|   | 4.5 | Sample Optimization                  | 53 |  |  |  |  |  |

|   | 4.6 | Summary                              | 53 |  |  |  |  |  |

| 5 VSSC Framework Examples 56 |       |         |                                             |    |  |  |  |  |

|------------------------------|-------|---------|---------------------------------------------|----|--|--|--|--|

|                              | 5.1   | Introd  | luction                                     | 56 |  |  |  |  |

|                              | 5.2   | Exam    | ple Graphs                                  | 57 |  |  |  |  |

|                              |       | 5.2.1   | Flow Graph                                  | 57 |  |  |  |  |

|                              |       | 5.2.2   | Direct Acyclic Graph                        | 60 |  |  |  |  |

|                              |       | 5.2.3   | Register-Interference Graph                 | 64 |  |  |  |  |

|                              | 5.3   | Exam    | ple Optimization:                           |    |  |  |  |  |

|                              |       | Elimir  | nation of Dead Code                         | 65 |  |  |  |  |

|                              |       | 5.3.1   | Dead Code Elimination                       | 65 |  |  |  |  |

|                              |       | 5.3.2   | Live Variable Analysis                      | 65 |  |  |  |  |

|                              |       | 5.3.3   | Eliminating Dead Code in Bubblesort Example | 67 |  |  |  |  |

|                              | 5.4   | Exam    | ple Optimization:                           |    |  |  |  |  |

|                              |       | Propa   | gating Available Copy Instructions          | 69 |  |  |  |  |

|                              |       | 5.4.1   | Copy Propagation                            | 69 |  |  |  |  |

|                              |       | 5.4.2   | Available Code Analysis                     | 71 |  |  |  |  |

|                              |       | 5.4.3   | Example of Copy Propagation                 | 72 |  |  |  |  |

|                              | 5.5   | Exam    | ple: Register Allocation                    | 75 |  |  |  |  |

|                              | 5.6   | Summ    | nary                                        | 78 |  |  |  |  |

| 6                            | Con   | ıclusio | ns and Future Direction                     | 79 |  |  |  |  |

|                              | 6.1   | Future  | e Work                                      | 80 |  |  |  |  |

| Bi                           | bliog | graphy  |                                             | 82 |  |  |  |  |

| $\mathbf{A}$                 | VSS   | SC Use  | er Manual                                   | 88 |  |  |  |  |

|                              | A.1   | Introd  | luction                                     | 88 |  |  |  |  |

| A.2 | SUIF   |                                                              |

|-----|--------|--------------------------------------------------------------|

| A.3 | Simple | SUIF                                                         |

|     | A.3.1  | Simple-SUIF Intermediate Format                              |

|     | A.3.2  | Simple-SUIF API                                              |

|     | A.3.3  | Example of Simple-SUIF                                       |

| A.4 | VSSC   | 97                                                           |

|     | A.4.1  | Introduction                                                 |

|     | A.4.2  | VSSC API                                                     |

|     | A.4.3  | Installing VSSC Components                                   |

|     | A.4.4  | Environment Variables                                        |

|     | A.4.5  | Using VSSC                                                   |

|     | A.4.6  | Your First VSSC Optimization                                 |

| A.5 | VSSC   | Tips                                                         |

|     | A.5.1  | Debugging VSSC Optimizations                                 |

|     | A.5.2  | <b>printsimple</b>                                           |

|     | A.5.3  | Non-GUI VSSC                                                 |

|     | A.5.4  | Making Assertions                                            |

|     | A.5.5  | Using Data Structures                                        |

|     | A.5.6  | Examples using SUIF data structures and VSSC API $\dots$ 121 |

|     |        |                                                              |

## List of Figures

| 1.1 | Language-processing system                                         | 2  |

|-----|--------------------------------------------------------------------|----|

| 1.2 | Simplified model of compiler                                       | 3  |

| 2.1 | C and SUIF intermediate format version of same example program     | 20 |

| 2.2 | SimpleSUIF version of example code used in Figure 2.1              | 22 |

| 2.3 | simple_instr structure used to represent a Simple-SUIF instruction | 24 |

| 3.1 | dflo data-flow equations to compute liveness                       | 28 |

| 3.2 | DOT generated flow graph for quicksort algorithm                   | 30 |

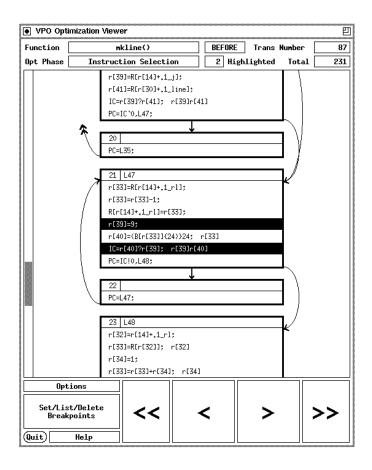

| 3.3 | Main window of $xvpodb$ application                                | 33 |

| 4.1 | Internal organization of VSSC framework                            | 39 |

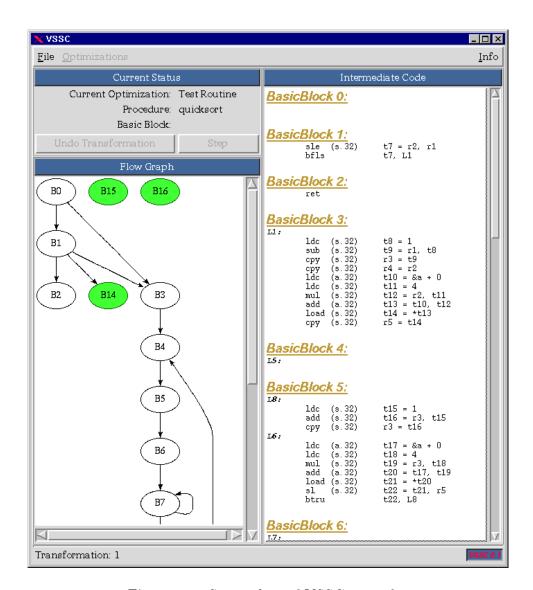

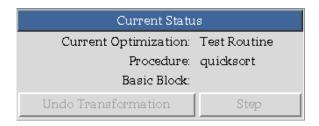

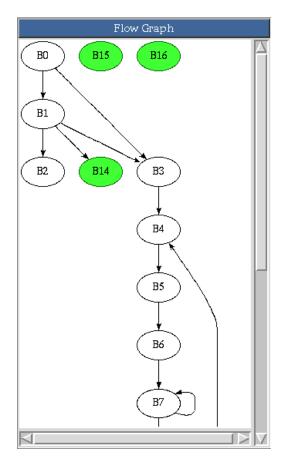

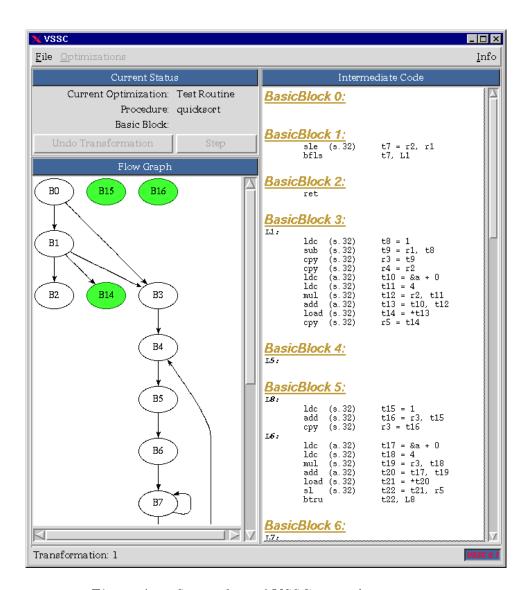

| 4.2 | Screenshot of VSSC compiler                                        | 41 |

| 4.3 | Current status component                                           | 42 |

| 4.4 | Graph component                                                    | 43 |

| 4.5 | Intermediate Code component                                        | 44 |

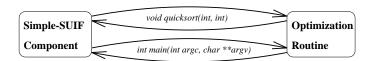

| 4.6 | Simple-SUIF component passing lists of Simple-SUIF instructions    |    |

|     | one at a time for each function to an optimization routine         | 48 |

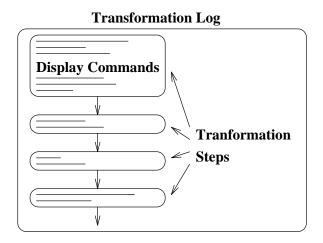

| 4.7 | Internal organization of the transformation log                    | 49 |

| 4.8 | The beginnings of a sample optimization                            | 54 |

| 5.1  | Example C program of bubblesort                                        | 59 |

|------|------------------------------------------------------------------------|----|

| 5.2  | Simple-SUIF version of bubblesort partitioned into basic blocks        | 59 |

| 5.3  | Flow graph of basic blocks for bubblesort example shown in Figure      |    |

|      | 5.2                                                                    | 60 |

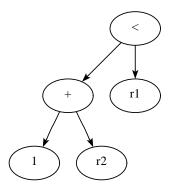

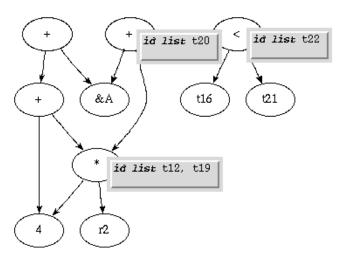

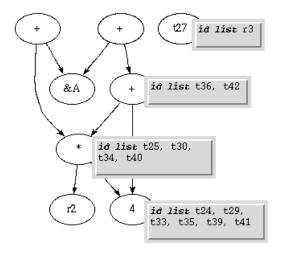

| 5.4  | Result of DAG construction for basic block $\#6$ in bubblesort example | 62 |

| 5.5  | Directed acyclic graph for basic block $\#4$ in bubblesort example     | 63 |

| 5.6  | Directed acyclic graph for basic block $\#5$ in bubblesort example     | 63 |

| 5.7  | Register-interference graph for bubblesort example                     | 64 |

| 5.8  | Algorithm for live variable analysis                                   | 66 |

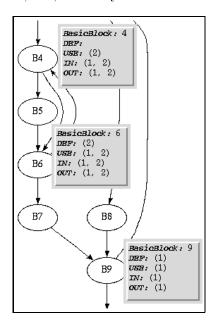

| 5.9  | Various results after performing live variable analysis                | 67 |

| 5.10 | Algorithm for the removable of dead code                               | 68 |

| 5.11 | Live-variable analysis information for basic block #8 in bubblesort    |    |

|      | example                                                                | 69 |

| 5.12 | Copy propagation algorithm                                             | 70 |

| 5.13 | Algorithm for available code analysis                                  | 72 |

| 5.14 | C and Simple-SUIF versions of copy propagation example                 | 73 |

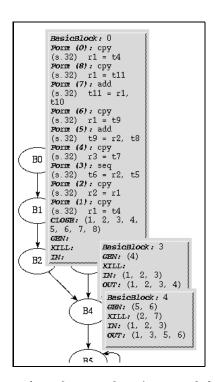

| 5.15 | Various results after performing available expression analysis         | 74 |

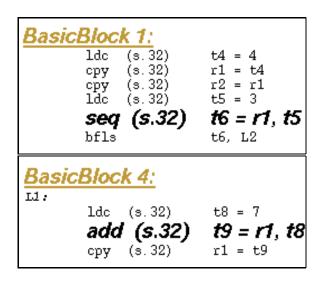

| 5.16 | Instructions that changed as a result of copy propagation on example   |    |

|      | in Figure 5.14                                                         | 75 |

| 5.17 | Graph-coloring heuristic algorithm for register-interference graph     | 76 |

| 5.18 | C and Simple-SUIF versions of register allocation example              | 77 |

| 5.19 | Register-interference graph for simple example in Figure 5.18          | 77 |

| 5.20 | Intermediate code of example in Figure 5.18 after register allocation  | 78 |

| A.1  | simple_instr structure used to represent a Simple-SUIF instruction     | 92 |

| A.2                                                          | Example demonstrating the different instruction formats                                                                                                                                                                             | 93                                     |

|--------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| A.3                                                          | Simple-SUIF API                                                                                                                                                                                                                     | 94                                     |

| A.4                                                          | Example C code to add a new Simple-SUIF instruction                                                                                                                                                                                 | 95                                     |

| A.5                                                          | Simple-SUIF base types                                                                                                                                                                                                              | 95                                     |

| A.6                                                          | Side-by-side comparison of C and Simple-SUIF                                                                                                                                                                                        | 96                                     |

| A.7                                                          | Screenshot of VSSC compiler in action                                                                                                                                                                                               | 99                                     |

| A.8                                                          | Optimizations API                                                                                                                                                                                                                   | 01                                     |

| A.9                                                          | Current Status Area API                                                                                                                                                                                                             | 02                                     |

| A.10                                                         | Header file for BasicBlock class                                                                                                                                                                                                    | 02                                     |

| A.11                                                         | Intermediate Code API                                                                                                                                                                                                               | 04                                     |

| A.12                                                         | Graph widget API                                                                                                                                                                                                                    | 05                                     |

| A.13                                                         | Graph widget API                                                                                                                                                                                                                    | 06                                     |

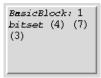

| A.14                                                         | Box that pops up when user clicks on graph node with left mouse                                                                                                                                                                     |                                        |

|                                                              |                                                                                                                                                                                                                                     |                                        |

|                                                              | button                                                                                                                                                                                                                              | 06                                     |

|                                                              | button                                                                                                                                                                                                                              |                                        |

| A.15                                                         |                                                                                                                                                                                                                                     | 07                                     |

| A.15<br>A.16                                                 | Miscellaneous VSSC commands                                                                                                                                                                                                         | 07<br>08                               |

| A.15<br>A.16<br>A.17                                         | Miscellaneous VSSC commands                                                                                                                                                                                                         | 07<br>08<br>09                         |

| A.15<br>A.16<br>A.17<br>A.18                                 | Miscellaneous VSSC commands                                                                                                                                                                                                         | 07<br>08<br>09                         |

| A.15<br>A.16<br>A.17<br>A.18<br>A.19                         | Miscellaneous VSSC commands       16         Environment variables that need to be set before using VSSC       16         Sample optimization registration       16         Sample Makefile       1                                 | 07<br>08<br>09<br>10                   |

| A.15<br>A.16<br>A.17<br>A.18<br>A.19<br>A.20                 | Miscellaneous VSSC commands       10         Environment variables that need to be set before using VSSC       10         Sample optimization registration       10         Sample Makefile       1         Sample main.cc       1  | 07<br>08<br>09<br>10<br>11             |

| A.15<br>A.16<br>A.17<br>A.18<br>A.19<br>A.20<br>A.21         | Miscellaneous VSSC commands                                                                                                                                                                                                         | 07<br>08<br>09<br>10<br>11<br>14       |

| A.15<br>A.16<br>A.17<br>A.18<br>A.19<br>A.20<br>A.21<br>A.22 | Miscellaneous VSSC commands 16   Environment variables that need to be set before using VSSC 16   Sample optimization registration 16   Sample Makefile 1   Sample main.cc 1   Assertions provided by SUIF 1   Generic List class 1 | 07<br>08<br>09<br>10<br>11<br>17       |

| A.15<br>A.16<br>A.17<br>A.18<br>A.19<br>A.20<br>A.21<br>A.22 | Miscellaneous VSSC commands16Environment variables that need to be set before using VSSC16Sample optimization registration17Sample Makefile1Sample main.cc1Assertions provided by SUIF1Generic List class1Associative List class1   | 07<br>08<br>09<br>10<br>11<br>17<br>18 |

| A.26 Example 1 source code |  |      | • |  |  |  | • |      | • |  |  |  | 122 |

|----------------------------|--|------|---|--|--|--|---|------|---|--|--|--|-----|

| A.27 Example 2 source code |  | <br> |   |  |  |  |   | <br> |   |  |  |  | 123 |

## List of Tables

| 1.1 | Some of the types of graph that can be constructed and displayed |    |

|-----|------------------------------------------------------------------|----|

|     | in VSSC                                                          | 10 |

| 2.1 | Valid Simple-SUIF instructions                                   | 23 |

| 4.1 | VSSC components and where to find them                           | 38 |

| 4.2 | Some commands in the tcldot API                                  | 46 |

| 4.3 | Command-line flags accepted by a VSSC Compiler                   | 53 |

| 5.1 | Bitsets used during live variable analysis                       | 66 |

| 5.2 | Bitsets used during available code analysis                      | 7  |

| A.1 | Valid Simple-SUIF instructions                                   | 9  |

| A.2 | VSSC components and where to find them                           | 10 |

## Chapter 1

## Introduction

Compilers play an important part in the field of Computer Science; they take a program that we have written and translate it to a form which can be executed on a computer. This can be done by reading a program written in a high-level language, called the source language, and translating it into an equivalent program in another language called the target language. A variety of compilers exist today because there are numerous source languages and many different target languages. Target languages range from the machine language for one of numerous different architectures to other high-level programming languages.

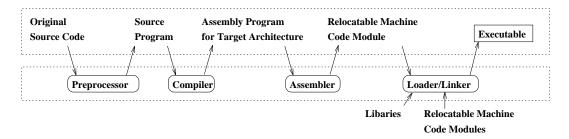

It is a common misconception that the process of compiling source code into an executable is performed by a single program. In actuality, this process is performed by an entire set of programs, each with its specific task, that together form a language-processing system [1]. This system typically includes: a preprocessor which performs macro expansion, header file inclusion, and perhaps language extensions, a compiler which takes this modified source code and translates it into equivalent assembly code, an assembler which converts assembly code generated

by the compiler into relocatable machine code, and a *loader/linker* which takes different modules of machine code and libraries and combines them into a single executable, altering reference addresses as needed. This language-processing system and its components are shown in Figure 1.1. This figure shows how the original source code transforms into the final executable program.

Figure 1.1: Language-processing system

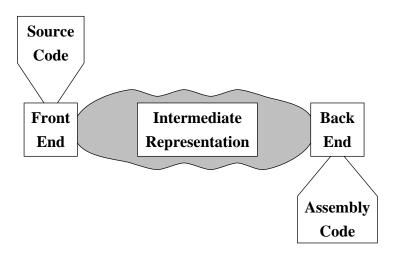

The functionality of the compiler module in a language-processing system can be separated into two main components [1]. The front end takes source code, performs lexical, syntactic, and semantic analysis on it and produces an intermediate representation of that code. The back end takes the intermediate representation, optimizes it, and generates assembly code for the target machine. As shown in Figure 1.2, the intermediate representation acts as the glue that connects the front and back ends together to produce a compiler.

#### 1.1 Front End

The front end takes source code and converts it to a format that is an intermediate representation of that source code. This process includes checking the syntax of the source code and checking the semantics of the source code. There exist several well-known tools to help compiler writers with the front end. These tools, which

Figure 1.2: Simplified model of compiler

include lex [23], yacc [20], and ANTLR [29], use a specification of the source language to generate a translator from the source language to an intermediate specification. This is often accomplished by using combinations of these tools targeting each to a portion of the translation. For example, lex generates a lexical analyzer which translates the source tokens to a token stream; similarly, yacc generates a syntactic parser which translates the token stream into a parse tree representation of the original source program. The theory behind the translation process performed by the front end is fairly mature and so are the tools which create these translators. Most of the recent front end research concentrates on the design and implementation of new language features.

#### 1.2 Intermediate Representation

The intermediate representation separates the front end, which deals with source language issues, from the back end, which deals with target issues. There are several properties necessary to make an intermediate representation useful. First

of all, it should be easy to generate from a variety of front ends. This allows it to remain useful as languages evolve (e.g.  $C \rightarrow C++$ ). Secondly, the intermediate representation should be easy to manipulate during code transformations. This simplifies the coding of the various analysis and transformations and allows changes to be made to the intermediate representation without difficulty. Finally, it must be machine-independent. This means that the intermediate code knows nothing about the target architecture. For example, it does not care about the number of registers the target provides and instead assumes an unlimited number of registers. Because it is machine-independent, intermediate code usually looks like assembly code for a virtual machine. This machine-independent feature means that the intermediate code can be retargeted to many different architectures simply by using a different back end and the compiler can use a machine-independent code optimizer in the back end.

The importance of a good intermediate representation is prevalent even in today's technologies. Java [18], a popular Internet programming language, translates Java source code into a bytecode format which acts as an assembly language for a virtual machine. This bytecode is the intermediate format between the source code and a running program. When a Java program is "executed", the bytecode is simply interpreted<sup>1</sup>. Java bytecode can be run, without modification, on any operating system that the Java interpreter has been ported to.

<sup>&</sup>lt;sup>1</sup>Recent advancements have produced Java Just-In-Time compilers, which use the Java byte-code as an intermediate representation for a completely separate compilation.

#### 1.3 Back End

Two tasks of the back end of an optimizing compiler are to modify the intermediate code to improve overall code performance by performing various code transformations and optimizations and to translate the intermediate code to assembly code for the target architecture.

Most recent research in compilers has concentrated around the optimizer component of the compiler. The optimizer determines what the final assembly code will look like and how fast it will run. The task performed by the optimizer must be separated into transformations or *phases* in order to make this enormous task manageable. The function of the optimizer is complicated by the fact that transformations cannot always be applied in any order. Additionally, these transformations normally cannot be combined because each transformation usually performs a specific task which requires data flow information useful for only that transformation.

The need to separate the optimization phases leads to some difficulties in ordering the transformations. Given a set transformations to perform, the following situation can occur: Once a certain optimization is done, a subsequent optimization may be unable to make any useful changes because of the changes made in the first transformation; whereas, if this second optimization had been executed before the other one, its transformations would have been more beneficial. Unfortunately, it is very difficult for a compiler back end to determine in what *order* the optimizations should be made.

This problem, called the *phase-ordering* problem, has been studied for many years. One example of this problem deals with register allocation and instruction scheduling. If register allocation is performed before scheduling, it may introduce

artificial data precedence, keeping the instruction scheduler from generating the best schedule. However, performing register allocation after instruction scheduling may result in the need for more registers. The phase-ordering problem can be difficult to avoid. Research in this area has proposed several solutions for specific transformations in which the phases are combined. A framework for describing optimizations and an example framework in which constant propagation, value numbering and unreachable-code elimination are combined is presented in [7]. Combining these phases allows for more information about the program to be discovered and thus more opportunities for optimization. In [25], register allocation and instruction scheduling are combined. A heuristic algorithm is used in which weights are used for controlling register pressure and instruction parallelism. Finally, a compiler in which the code generation phase and a machine-directed peephole optimizer are tightly integrated is described in [13] and [14]. These two components can be combined because they are both simple pattern matchers. A peephole optimizer replaces patterns of code with more efficient code while a code generator matches patterns of intermediate code and replaces them with assembly code. This compiler uses a single rule-based pattern matching system which makes the compiler simple, fast, and retargetable.

#### 1.3.1 Constructing Code Optimizers

Currently, few tools exist to help construct code optimizers. This is slowly changing as the importance of optimization grows. One such tool to appear is **Sharlit** [39]. Built to work with the SUIF compiler system, **Sharlit** helps in constructing data flow analyzers and the transformations that use data flow analysis information. Compiler writers are able to construct global analyzes and optimizations with the

following modular components: flow graphs, flow values (values that flow through the graph), flow functions that represent the effect of flow graph nodes and paths on flow values, action routines that are used to perform program optimizations based on the previous data flow analysis, and path simplification rules that show how to combine flow functions into other flow functions.

Like the front end of a compiler, the code generation stage of the back end is not as actively studied because the process is relatively simple: convert from one representation to another. Some tools exist to help compiler writers with this functionality of the back end. These tools, such as iburg [11], burg [12], and Twig [38], act as code generator generators. Each of these tools reads in a specification and generates C code to perform the code generation based on the specification. The specification usually specifies the cost of operands and instruction in the intermediate format. These tools use tree pattern matching and dynamic programming to produce a code generator. The main difference between the various code generator generators mentioned is how they implement their tree pattern matching and whether the dynamic programming is done when the tool is used or if it is embedded in the generated code generator.

#### 1.4 Design Tools for Developing Optimizers

There are few tools which support the process of studying back end optimizations. Currently, researchers examining different back end optimizations must rely on general debugging tools or design their own tools to help in the generation of optimizing functions. A tool designed to give information specifically tailored for optimization designers is necessary. This tool would give researchers the ability to analyze how their new optimization (or existing optimizations) and the intermediate code are affected when performing optimizations in different orders. More efficient development of optimization routines should be the result of using such a tool.

In order to develop such a tool, the intermediate format used in the compiler needs to be well designed and should not change between code transformations; the SUIF (Stanford University Intermediate Format) compiler [42] has such an intermediate format. The SUIF system is organized as a set of compiler passes built on top of a kernel that defines the intermediate format. Each pass is implemented as a separate program which reads in the SUIF representation of the source program from a file generated by the front end, performs some code transformation, and then writes out the resulting SUIF representation to a file. Since the SUIF format never changes, these passes can be performed in any order.

SUIF provides the necessary platform for true development of a tool designed to support the development of code transformations. The work described in the remainder of this thesis develops one such tool, the Visual Simple-SUIF Compiler package.

#### 1.5 VSSC

The topic of this thesis is the Visual Simple-SUIF Compiler (VSSC) package which we have developed. This package is designed to provide an interactive framework that allows the development of compiler optimizations. It incorporates a graphical user interface with an underlying Simple-SUIF compiler framework to illustrate data flow analysis and code transformations. VSSC has many advantages that

make it useful to both optimization researchers and students alike.

Built on top of the SUIF compiler, VSSC inherits all the strengths of SUIF as well as adding new ones. As in the SUIF compiler, it is easy to add new optimizations to a VSSC compiler and to perform optimizations in any order. The user can select which optimizations to perform through the use of a graphical interface. Transformations can be applied in any order and as many times as desired. This "interactive" ability allows the user to see the effects different code transformations have on the intermediate code after each transformation, as well as viewing the effects of different implementations of a particular code transformation (e.g. different methods of doing dead code elimination). This ability also allows a researcher to see the different results of the intermediate code depending on the order that the transformations are performed. In addition, the researcher can select a transformation to be performed based on the observed characteristics of the current state of the intermediate code. VSSC allows transformations to be undone, so the user can perform an optimization, undo it, and then perform another optimization. Another advantage provided by VSSC is that its GUI library allows the optimization designer freedom in controlling what information the GUI displays to the user.

A VSSC compiler runs until the user exits allowing intermediate code to be studied indefinitely between code transformations and viewed at each step during a code transformation. VSSC provides the ability for the optimization writer to display a graph during the transformation. Table 1.1 shows some of the possible types of graphs that can be displayed using VSSC. Examples of these graphs will be demonstrated in Section 5.2.

Showing a graph during the code transformation aids the user in understanding

| Type of Graph               | Purpose in a Compiler                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

|-----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Flow Graph                  | This type of graph illustrates the flow-of-control information for a procedure. Each node in the graph represents a basic block, a sequence of consecutive statements in which flow of control enters only at the beginning and exits only at the end. There is a directed edge in the graph from block $B_i$ to block $B_j$ if $B_j$ can immediately follow $B_i$ in some execution sequence.                   |  |  |  |  |  |

| Directed Acyclic Graph      | In a DAG, the information of how the value computed by each statement in a basic block is used in subsequent statements of the same block is shown. This information can be used to find common subexpressions (those expressions which are computed more than once can be eliminated). Leaves in this graph are unique identifiers (variable names of constants) and interior nodes are mathematical operators. |  |  |  |  |  |

| Register-Interference Graph | This type of graph is sometimes used when implementing register allocation using graph coloring. The nodes in this graph are symbolic registers and an edge connects two nodes (registers) if one register is live at a point where the other is defined.                                                                                                                                                        |  |  |  |  |  |

Table 1.1: Some of the types of graph that can be constructed and displayed in VSSC

the steps in the code transformation as well as emphasizing the importance of that graph data structure in the code transformation. For example, a flow graph allows the user to view the various possible execution paths between basic blocks in the intermediate code.

Perhaps one of the most important benefits provided by VSSC is the ability to step through an optimization. Much in the same way that you can step through code in a code debugger such as GDB [35], the VSSC package allows the optimiza-

tion writer to configure *steps* within the optimization and when the optimization is performed in the VSSC compiler, the GUI user can *step* through the optimization at his or her own pace. The optimization writer has complete freedom to include whatever actions he or she likes within each step.

Finally, since people tend to learn better by visualization as well as being able to step through an optimization at their own speed, the VSSC package is particularly helpful when used in the academic environment. VSSC can be used as a teaching tool in courses on optimizing compilers. Students taking a course in optimizing compilers can use VSSC in two ways. The first way in which it could be used is that the instructor provides to the students a ready-made VSSC compiler which already implements various optimizations. The students can then use VSSC to augment their learning of an optimization presented by their instructor by *stepping* through it with VSSC on any C code they wish. In this way, VSSC can be a teaching tool for the study of compiler back ends.

Students can also benefit from using VSSC when writing their own optimizations. In a typical optimizing compiler course, students implement such standard optimizations as dead-code elimination, common subexpression elimination, and others described in [1]. Students can use VSSC to facilitate their understanding of what happens during one of these optimizations. VSSC can show them the results of a particular data flow analysis and the effects of a transformation. Students can learn only so much from a textbook and from trying out an optimization on paper. They can gain more insight about the optimization when they can actually see it in action on the screen in front of them. VSSC has been used in the graduate compiler course at the University of California, Riverside. Students implemented basic block detection, various data flow analysis, and register allocation using VSSC.

#### 1.6 Thesis Organization

Chapter 2 provides background information on various retargetable compilers and the intermediate representations they use. It concludes with a description of the compiler used by VSSC. Chapter 3 includes descriptions of work in the area of compiler visualization tools and previous work related to VSSC. Chapter 4 describes the overall design, organization, and implementation of VSSC. Examples of a VSSC compiler performing various optimizations, as well as various types of graphs that can be displayed with VSSC, are shown in Chapter 5. Chapter 6 provides a conclusion along with a discussion of possible future directions for VSSC. Appendix A provides a user's manual for VSSC that describes VSSC's application program interface (API), how to get started using VSSC, and various tips and suggestions on the use of the package.

## Chapter 2

## Retargetable Compilers

In order to implement the functionality proposed in VSSC, an easily extendible compiler with a robust intermediate format was needed. This chapter discusses several free C compilers including the intermediate format that they use. Their various strengths and weaknesses will be presented as well as an analysis of their suitability for the VSSC framework.

#### 2.1 Requirements for a Retargetable Compiler

A retargetable compiler is one that can support multiple targets by incorporating multiple back ends to generate code for different target architectures. This capability of a compiler is strongly influenced by the intermediate language used by the compiler. In order to make retargeting easy, the intermediate language needs to be machine-independent. If it doesn't rely on the characteristics of the target architecture, then a code generator can be written to generate code from that intermediate code for virtually any architecture.

Academic and research groups tend to use retargetable compilers to allow for

greater flexibility in educational and research goals. Because they are retargetable, they usually also run on the various architectures in use at that institution. It is not surprising that retargetable compilers are better organized than their monolithic counterparts. In order to be retargetable, the compiler needs to have a well-defined interface and be modular in design. Most research groups also tend to use free retargetable compilers for obvious reasons. In a situation where you want to test out a new compiler feature, it is easier to incorporate it in into an existing compiler for which you have the source code than constructing your own compiler from scratch or purchasing a source code license for a commercial compiler.

In this section we look at three popular retargetable compilers in order to determine which one best supports the VSSC framework. These compilers are: the GNU gcc compiler [34] developed by Richard Stallman (and numerous other people), the 1cc compiler [9] developed by Christopher W. Fraser at AT&T Bell Laboratories and David R. Hanson at Princeton University, and the SUIF compiler [42] developed by Monica Lam at Stanford University. These systems are briefly evaluated below.

#### 2.2 GNU C Compiler (GCC)

The GNU C Compiler (GCC) [34], which can compile C, C++, and Objective-C code, is arguably the world's most popular free compiler. GCC's greatest strength is that fact that GCC has been ported to and has been retargeted to many different operating systems and architectures. This wide-range of use is made possible by GCC's robust intermediate format.

GCC's front end converts the source code into a Lisp-like register transfer

language (RTL). The RTL describes each target-dependent instruction in a target-independent algebraic form that defines the semantics of an instruction. After various code transformations are performed on the RTL, GCC's back end takes this RTL and generates code for the target architecture. The specification of the target architecture is based on a machine description that identifies the target code to generate for each possible expression in the RTL.

The widespread use of the GNU Compiler and the large number of contributors to its set of supported optimizations has led to a complex implementation. The GCC design lacks modularity and is somewhat monolithic in design. In addition, the optimization passes made on the RTL have become so dependent on each other over the years that the passes need to be done in a specific order. These limitations make it very difficult to implement the functionality planned for VSSC using the GCC compiler.

#### 2.3 LCC

The 1cc compiler [9] [10] is an ANSI C compliant retargetable compiler that can generate code for VAX, Motorola 68020, i386, SPARC, and MIPS R3000 architectures. Developed by Christopher W. Fraser at AT&T Bell Laboratories and David R. Hanson at Princeton University, 1cc is heavily used at both institutions.

1cc has many features that make it popular. The simple and compact design of 1cc makes it one of the smallest and fastest ANSI C compilers available. Probably the most useful feature of 1cc is the quality of its the documentation. The authors used the **noweb** [31] system to generate a textbook [10] and the source code for 1cc from a single source. Therefore, the textbook, which describes the implementation

of lcc, includes most of the code of lcc along with the explanation of that code and how it contributes to the implementation. When generating the textbook, noweb system automatically cross-references all code segments so a reader of the textbook can easily navigate the source code. This is very helpful, since the source code is presented in the textbook in an order that follows the description of the implementation.

The target-independent front end and the target-dependent back end of 1cc exist together in a single executable glued together by an efficient interface. This interface consists of only 18 functions and the C code being compiled is represented by a 36-operator dag language [8]. This language is the intermediate format of 1cc and represents the source program as it goes from the front end to the back end in the compilation process. The dag language has gone through many changes during the development of 1cc. In each change, the authors usually took a more complex operator out of the dag language and added functionality for it in the front end. Consequently, each change made the back end less complex.

1cc has a number of features, which are not normally found in other compilers, that increase its usefulness to the user. Command-line flags can specify that the code generated will check for the dereferencing of a null pointer (a common programming mistake in C), print out function call/return traces, and generate execution profiles. When 1cc performs frequency-based profiling, it generates code that keeps track of the number of times each expression is calculated. This allows programmers to try to simplify those expressions that are frequently calculated. The accumulated profiling data can be displayed and analyzed.

1cc, despite its many strengths, has several weaknesses. First of all, it is not an optimizing compiler. While its front end performs some target-independent op-

timizations such as local common subexpression elimination, constant folding, and other simple transformations, no other optimizations are specified. Other typical compiler systems implement many more global and target-dependent optimizations. Another weakness is the tightly-coupled design between the front and back ends. While this design allows lcc to be a small and fast compiler, it can be difficult for a researcher to use lcc for a large back-end compilation environment. The design and organization of lcc is so highly optimized for compilation speed and code compactness that small changes to one component may greatly affect other components. Other compiler systems, such as SUIF described in the next section, are more modular and robust in their design. This modularity allows a researcher to concentrate only on what they need to, without worrying about how it affects the rest of the compiler system.

#### 2.4 SUIF Compiler System

The SUIF research compiler system [42] [43], developed by a team of researchers under the direction of Monica Lam at Stanford University, is centered around the robust design of its intermediate format called SUIF (Stanford University Intermediate Format). The system has been designed and organized in such a way that it is easy to modify and extend the base system to generate custom compilers. The SUIF team took considerable effort to make the system usable by other research groups. For this reason, many researchers around the world use the SUIF compiler system to evaluate new compiler techniques and perform research on analysis and optimization algorithms.

The SUIF system is organized into two components. The kernel of the SUIF

compiler defines the central core of the compiler. The design goals of the kernel are [43]:

- to make all program information necessary for scalar and parallel compiler optimizations easily available

- to foster code reuse, sharing, and modularity

- to support experimentation and system prototyping.

The kernel performs three major tasks: it defines and manages the intermediate format SUIF, it provides a set of routines for manipulating the intermediate format, and it provides an information and communication interface between compiler passes.

#### 2.4.1 SUIF Intermediate Format

The SUIF intermediate format is different from the intermediate formats used by the previously discussed compilers. Those intermediate formats are very low-level while SUIF's intermediate format is a "mixed-level" program representation incorporating both low-level and high-level information. The high-level information includes: loops, conditional statements, and array access operations. The low-level information includes: assembly-like intermediate code, jumps and branches to labels, and symbolic registers. One of the features of the SUIF compiler system is its ability for determining the amount of parallelism in a program<sup>1</sup>. The inclusion of these high-level constructs simplifies the design of analyzers and optimizers. For example, there are many optimizations that deal with loops. However, these

<sup>&</sup>lt;sup>1</sup>This information can be used to increase program parallelism and locality.

optimizations must detect the loops using data-flow analysis. An optimization in SUIF does not need to perform such analysis, because loop information already exists in the intermediate format. Figure 2.1 shows a sample C program and the SUIF intermediate format of the same example program (using the printsuif program<sup>2</sup>).

#### 2.4.2 SUIF Transformation Environent

The second component of the SUIF system is a set of compiler passes that perform various transformations on the intermediate format. Usually, each pass reads in the intermediate code, performs some transformation, analysis, or optimization, and then writes out the intermediate code. Since each pass can exist as a separate executable in the SUIF system, passes can be run in any order in the compilation process. Information can be relayed from pass to pass by annotating components in the intermediate format. To aid in the creation of SUIF compiler passes, the SUIF system contains a robust set of libraries, commonly used data structures, and support routines.

<sup>&</sup>lt;sup>2</sup>Actually, printsuif displays a lot more information about the SUIF intermediate format for this C code, but to save space, only part of the information is shown here for comparison purposes.

```

PROC P:.main

["line": 2 "example.c"]

1: mrk

["line": 5 "example.c"]

2: FOR (Index=main.x Test=SLT Cont=L:main.L1 Brk=L:main.L2)

FOR LB

ldc t:g4 (i.32) 0

FOR UB

30:

ldc t:g4 (i.32) 100

FOR STEP

ldc t:g4 (i.32) 1

FOR LANDING PAD

32:

FOR BODY

mrk

["line": 7 "example.c"]

ldc t:g4 (i.32) main.z = 0

8:

mrk

["line": 9 "example.c"]

FOR (Index=main.y Test=SLT Cont=L:main.L3 Brk=L:main.L4)

9:

22:

ldc t:g4 (i.32) 0

FOR UB

main.x

FOR STEP

ldc t:g4 (i.32) 1

FOR LANDING PAD

25:

FOR BODY

13:

mrk

["line": 11 "example.c"]

14:

IF (Jumpto=L:main.L5)

IF HEADER

bfalse e1, L:main.L5

e1: sl t:g31 (i.32) e2, main.x

e2: add t:g4 (i.32) main.y, main.z

16:

17:

IF THEN

18:

mrk ["line": 12 "example.c"]

19:

add t:g4 (i.32) main.z = main.z, e1

e1: ldc t:g4 (i.32) 1

20:

IF ELSE

IF END

FOR END

26:

mrk

["line": 9 "example.c"]

FOR END

34: mrk

34: mrx

["line": 15 "example.c"]

35: cal t:g4 (i.32) <nullop> = e1(e2, main.z)

36: e1: ldc t:g39 (p.32) <P:.printf,0>

42: e2: ldc t:g34 (p.32) <.__tmp_string_0,0>

42: e2

39: mrk

["line": 16 "example.c"]

40: ret e1

41: e1: ldc t:g4 (i.32) 0

PROC END

```

Figure 2.1: C and SUIF intermediate format version of same example program

The SUIF compiler may not be the fastest or the most robust compiler, but the flexibility and extensibility of its design outweighs these possible shortcomings for the study of back-end code transformations. The SUIF compiler is not meant to be a production quality compiler. Instead it is meant to act as a research vehicle, designed to support modularity and experimentation at the cost of the speed of translation.

#### 2.4.3 Simple-SUIF

Since the SUIF compiler is a complete ANSI C compiler, it is a little too complex for use in a college course in compilers. The SUIF Compiler group at Stanford developed a package called **Simple-SUIF** [36] which acts as a wrapper for SUIF by providing a simplified interface to the intermediate format generated by the SUIF compiler. When using Simple-SUIF, the SUIF intermediate format remains the same internally, but differs in the way the programmer interacts with the system. This simplified interface allows students to write their own optimizations for a fully-functional ANSI C compiler without learning the high-level constructs required to perform compiler transformations (e.g. interprocedural analysis).

Figure 2.2 shows the Simple-SUIF version of the example code in Figure 2.1. As you can see, the instructions in Simple-SUIF's intermediate format resemble assembly language instructions ( $op\ dst, src1, src2$ ) or three-address C instructions ( $dst = src1\ op\ src2$ ). Each instruction has an unique opcode associated with it. The instructions are grouped into six different categories called *instruction formats*. Table 2.1 shows all the valid Simple-SUIF instructions. For each instruction, the following information is also shown: the opcode, the Simple-SUIF name, the instruction format, and a short explanation of that instruction.

```

ldc (s.32)

(s.32)

r3 = t6

сру

ldc

(s.32)

сру

(s.32)

t8 = 0

t9 = t8, r3

sl

(s.32)

t9, L6

ldc

t10 = 0

(s.32)

r4 = t10

сру

add

(s.32)

t11 = r4. r5

t12 = t11, r3

sl

(s.32)

bfls

t12, L5

(s.32)

t13 = 1

t14 = r5, t13

ldc

(s.32)

add

(s.32)

r5 = t14

сру

ldc

(s.32)

t16 = r4, t15

add

(s.32)

r4 = t16

сру

t17 = r3, r4

t17, L7

(s.32)

bfls

L6:

ldc

(s.32)

t18 = 0

сру

(s.32)

r4 = t18

_done8:

ldc

(s.32)

t19 = 1

t20 = r3, t19

{\tt add}

r3 = t20

t21 = 100

cpy

ldc

(s.32)

(s.32)

t22 = t21, r3

bfls

t22, L9

ldc

t23 = &printf + 0

t24 = &__tmp_string_0 + 0

*t23 (t24, r5)

ldc (a.32)

call (s.32)

ldc

(s.32)

t25 = 0

t25

```

Figure 2.2: SimpleSUIF version of example code used in Figure 2.1

A Simple-SUIF instruction is represented by the **simple\_instr** structure. Figure 2.3 shows the **simple\_instr** structure and its contents. When writing an optimization pass with Simple-SUIF, the intermediate format is given to the programmer as a linked list of these instructions. The optimization can then manage the items in this linked list. When an optimization is performed, the elements in the linked list are modified and the linked list is returned back to the Simple-SUIF library. This intermediate code is then saved back to a file.

| Simple-SUIF Instructions       |                                              |                        |                                                    |  |  |  |

|--------------------------------|----------------------------------------------|------------------------|----------------------------------------------------|--|--|--|

| Opcode                         | Instr. Na                                    | me Instruction Forma   | t Purpose                                          |  |  |  |

| No operand instructions        |                                              |                        |                                                    |  |  |  |

| NOP_OP                         | nop                                          | BASE_FORM              | No nothing at all                                  |  |  |  |

|                                |                                              | One source operand (si | rc1) instructions                                  |  |  |  |

| RET_OP                         | ret                                          | BASE_FORM              | Return from a procedure                            |  |  |  |

|                                | Two source operand (src1, src2) instructions |                        |                                                    |  |  |  |

| STR_OP                         | str                                          | BASE_FORM              | Store the value in the src2                        |  |  |  |

|                                |                                              |                        | register at the address contained in the           |  |  |  |

|                                |                                              |                        | src1 register                                      |  |  |  |

| MCPY_OP                        | mcpy                                         | BASE_FORM              | Memory-to-memory copy                              |  |  |  |

| Unary instructions (dst, src1) |                                              |                        |                                                    |  |  |  |

| CPY_OP                         | сру                                          | BASE_FORM              | Copy the src1 register to the                      |  |  |  |

|                                |                                              |                        | dst register                                       |  |  |  |

| CVT_OP                         | cvt                                          | BASE_FORM              | Convert the src1 register to                       |  |  |  |

|                                |                                              |                        | the result type and put it in the                  |  |  |  |

|                                |                                              |                        | dst register                                       |  |  |  |

| NEG_OP                         | neg                                          | BASE_FORM              | Negation                                           |  |  |  |

| NOT_OP                         | not                                          | BASE_FORM              | Bit-wise inversion                                 |  |  |  |

| LOAD_OP                        | load                                         | BASE_FORM              | Load the value at the address contained            |  |  |  |

|                                |                                              |                        | in the <b>src1</b> register and put it in          |  |  |  |

|                                |                                              |                        | the dst register                                   |  |  |  |

|                                |                                              | Binary instructions (  |                                                    |  |  |  |

| ADD_OP                         | add                                          | BASE_FORM              | dst = src1 + src2                                  |  |  |  |

| SUB_OP                         | sub                                          | BASE_FORM              | dst = src1 - src2                                  |  |  |  |

| MUL_OP                         | mul                                          | BASE_FORM              | dst = src1 * src2                                  |  |  |  |

| DIV_OP                         | div                                          | BASE_FORM              | $\mathrm{dst} = \mathrm{src1/src2}$                |  |  |  |

| REM_OP                         | re m                                         | BASE_FORM              | dst = src1%src2                                    |  |  |  |

| MOD_OP                         | mod                                          | BASE_FORM              | dst = abs(src1%src2)                               |  |  |  |

| AND_OP                         | and                                          | BASE_FORM              | Bit-wise AND                                       |  |  |  |

| IOR_OP                         | ior                                          | BASE_FORM              | Bit-wise inclusive OR                              |  |  |  |

| XOR_OP                         | xor                                          | BASE_FORM              | Bit-wise exclusive OR                              |  |  |  |

| ASR_OP                         | asr                                          | BASE_FORM              | Signed shift right                                 |  |  |  |

| LSL_OP                         | lsr                                          | BASE_FORM              | Unsigned shift right                               |  |  |  |

| LSR_OP                         | lsl                                          | BASE_FORM              | Unsigned shift left                                |  |  |  |

| ROT_OP                         | rot                                          | BASE_FORM              | Rotate value in src1 register left                 |  |  |  |

|                                |                                              |                        | (positive value) or right (negative value) by      |  |  |  |

|                                |                                              |                        | the amount specified in the src2                   |  |  |  |

| CEO OB                         |                                              | BASE_FORM              | register                                           |  |  |  |

| SEQ_OP<br>SNE_OP               | seq                                          | BASE_FORM  BASE_FORM   |                                                    |  |  |  |

| SL_OP                          | sne                                          |                        |                                                    |  |  |  |

|                                | sl                                           | BASE_FORM              | dst = (src1 < src2)                                |  |  |  |

| SLE_OP                         | sle                                          | BASE FORM              | $\mathbf{dst} = (\mathbf{src1} \le \mathbf{src2})$ |  |  |  |

| IMD OD                         |                                              | Branch and jump        |                                                    |  |  |  |

| JMP_OP                         | jmp                                          | BJ_FORM                | Unconditional jump: goto target                    |  |  |  |

| BTRUE_OP                       | btru                                         | BJ_FORM                | Branch if true: if (src1) goto target              |  |  |  |

| BFALSE_OP                      | bfls                                         | BJ_FORM                | Branch if false: if (!src1) goto target            |  |  |  |

| I D G O D                      | 1 11                                         | Miscellane             |                                                    |  |  |  |

| LDC_OP                         | ldc                                          | LDC_FORM               | Load a constant value                              |  |  |  |

| CALL_OP                        | call                                         | CALL_FORM              | Call a procedure                                   |  |  |  |

| MBR_OP                         | mbr                                          | MBR_FORM               | Multi-way branch                                   |  |  |  |

| LABEL_OP                       | lab                                          | LABEL_FORM             | Label pseudo-instruction                           |  |  |  |

Table 2.1: Valid Simple-SUIF instructions

```

simple_op opcode;

/* the opcode */

simple_type *type;

/* type of the result */

struct simple_instr *next; /* ptr to next instruction */

struct simple_instr *prev; /* ptr to previous instruction */

/* the variant part of the union is determined

union u:

by the result of simple op format(opcode) */

/* BASE_FORM */

struct base {

simple_reg *dst; /* destination */

simple_reg *src1; /* source 1 */

simple_reg *src2; /* source 2 */

/* BJ_FORM */

struct bj {

simple_sym *target; /* branch target label

/* source register */

simple_reg *src;

/* LDC_FORM */

struct ldc {

simple_reg *dst;

/* destination */

simple_immed value; /* immediate constant *

/* CALL_FORM */

struct call {

simple_reg *dst;

/* return value destination */

simple_reg *proc; /* address of the callee */

unsigned nargs; /* number of arguments. */

simple_reg **argsl /* array of arguments */

/* MBR_FORM */

struct MBR {

simple_reg *src;

/* branch selector */

/* branch selector offset */

int offset:

simple_sym *deflab; /* label of default target */

/* number of possible targets *

unsigned ntargets:

simple_sym **targets; /* array of labels */

/* LABEL FORM */

struct label {

simple_sym *lab; /* the symbol for this label */

```

Figure 2.3: simple\_instr structure used to represent a Simple-SUIF instruction

As you can see from Figure 2.3, the **simple\_instr** structure contains a member, **u**, which is a union of many other structures<sup>3</sup>. Each of the structures in the union represents a different instruction format in which all the Simple-SUIF instruction opcodes map to. The Simple-SUIF library contains support routines to help the programmer deal with this data structure. Appendix A provides more information on how to use and interact with Simple-SUIF.

$<sup>^3\</sup>mathrm{A}$  union is used to save memory since an instruction can only be one type of instruction format.

## 2.5 Summary

In this chapter, three retargetable compiler systems were examined for use as the compiler base for the VSSC framework. The stengths and weaknesses of each were presented. At one end of the spectrum is GCC, a large, slow, monolithic compiler with very good optimization routines. At the other end of the spectrum is 1cc, a small, fast, non-optimizing compiler whose compact design makes it difficult to expand. The design and organization of these compilers would not fit well in the VSSC framework.

The features of the SUIF compiler framework fulfill the design goals of the VSSC framework far better than those of GCC or lcc. The modular design of the SUIF compiler framework allows it to be integrated easily into the VSSC framework. Using the SUIF intermediate format, VSSC has ability to perform optimizations in any order. Finally, incorporating the Simple-SUIF package allows VSSC to be used by both researchers and students.

# Chapter 3

# Compiler Visualization Tools

Due to recent advances in GUI technology, graphical user interfaces are now becoming easier to create. This allows a program that was previously text-based to have a graphical front end to improve user interaction. A graphical user interface allows compilicated information to be presented more understandable manner. A compiler is a good example of a text-based program that can benefit from a graphical user interface. Such an interface would allow the compiler to display information of interest to those debugging a component of the compiler or learning about the compilation process.

Perhaps an important piece of information that should be displayed in the graphical user interface of a compiler while the back end is executing is the various data structures used in code transformations. These structures can be displayed to illustrate both the analysis and transformation algorithms required to perform a particular optimization. In order to display various types of graphs, a tool to handle the graph drawing capabilities is needed. This chapter first discusses various graph drawing tools, which are an important component of most compiler

visualization tools, since graphs are the primary data structures in compilers. The second part of this chapter is a discussion of several compiler visualization projects similar to VSSC.

## 3.1 Graph Drawing Tools

The graph drawing process is complicated. There is an large amount of research being done in this field [3] and many algorithms have been designed to draw graphs that look aesthetically pleasing. As a result of this research, many graph drawing tools exist to demonstrate the feasibility of these graph drawing algorithms. Such tools include: **ffgraph** [15], **daVinci** [16],  $Graph^{Ed}$  [19], and DOT [21]. Most tools are stand-alone programs, while others such as DOT can be integrated into an existing GUI such as Tcl/Tk [28] [40].

There are several other graph drawing tools that are more specialized in their functionality in that they are used to draw many of the data structures present in compilers: flow graphs, syntax trees, call graphs, and data dependence graphs. Two such tools are dflo [44] and VCG [32]. VCG is used to graphically display typical data structures found in a compiler, while dlfo can be used to solve data-flow equations.

#### 3.1.1 VCG

Textual representations of compiler data structures, such as trees or graphs, can often be confusing or unreadable. **VCG** shows trees and graphs in a natural way that allows powerful debugging of the internals of a compiler and the examination of the effects of transformations on the intermediate representation.

The specification of a graph is supplied to **VCG**, which then assigns horizontal and vertical positions to each node and computes splines for the edges in such as way that the edges do not overlap with nodes. Constructed graphs can be *folded* allowing unimportant parts of the graph to be hidden, while important components can be shown in more detail. The output of the constructed graph can viewed using a self-contained X-windows tool or saved as a postscript file.

#### 3.1.2 dflo

dflo [44] is a tool that inputs: a description of a flow graph, the variables assigned and expressions computed in each flow graph node, and a system of data-flow equations. It then solves the data-flow equations and allows the user to interactively view the results. The flow graphs generated by dflo look very nice and the data-flow equations are easy to construct. Figure 3.1 shows the dflo data-flow equations to compute liveness.

```

{ LIVE edge - [0] = any succs( LIVE ) * TRANSUP + EXPOSEUP;

LIVE.in node - [1] = LIVE.out * TRANS + EXPOSEUP;

LIVE.out node - [1] = any succs( LIVE.in ) }

```

Figure 3.1: dflo data-flow equations to compute liveness

Unfortunately, dflo uses the commercial Motif graphical user interface as its GUI front end. It therefore can not be incorporated into VSSC, since a design goal of VSSC is to only use freely available software.

#### 3.1.3 DOT

Neither VCG nor dlfo would integrate well into the VSSC framework. These tools are designed to be standalone programs, which are difficult to incorporate into a larger package like VSSC. We chose to integrate the DOT [21] package with VSSC to implement the graph drawing capabilities VSSC provides.

DOT is a general graph drawing tool which draws directed graphs using a fourstep algorithm [17]:

- 1. Assigns discrete ranks to nodes. These ranks determine the Y coordinates in the final drawing.

- 2. Orders nodes within ranks to avoid crossings.

- 3. Assigns X coordinates to nodes while keeping edges short.

- 4. Routes edge splines between nodes that have edges.

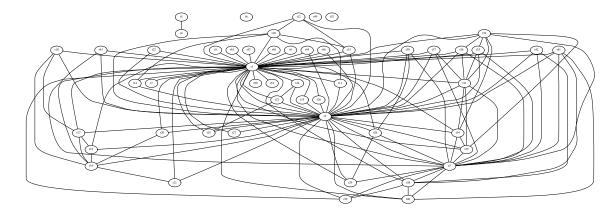

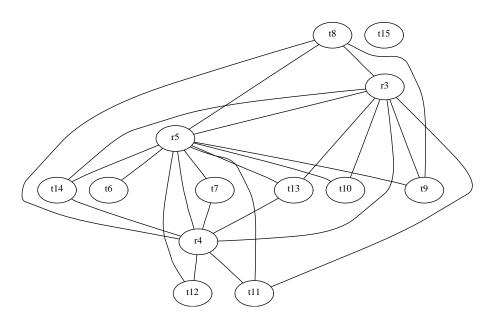

The graphs produced by DOT are well suited to display the graph data structure information necessary in a compiler. Figure 3.2 shows a sample flow graph for an implementation of the quicksort algorithm. The drawing and layout algorithms used in DOT are able to generate the graphs fast enough to support interactive GUIs. A detailed explanation of DOT and how it is integrated into the VSSC framework is presented in Section 4.3.2.

## 3.2 Visual Compiler Tools

Previously there were very few compiler visualization tools or visual compilers.

Compiler systems tended to be text-based and not designed for use with a graphical

Figure 3.2: DOT generated flow graph for quicksort algorithm